3第2章2 FPGACPLD基本结构及原理

3第2章2 FPGACPLD基本结构及原理

《3第2章2 FPGACPLD基本结构及原理》由会员分享,可在线阅读,更多相关《3第2章2 FPGACPLD基本结构及原理(18页珍藏版)》请在装配图网上搜索。

1、第二章FPGA基本概念2.2 Cyclone II 系列 FPGA1、Cyclone II 系列 FPGA 概述EP2C35F672C6,是 Altera 的 DE2 教育平台选用的 Cyclone II 系列 FPGA。 Cyclone II系列是低成本的FPGA,它将低成本FPGA的密度扩展到了 68416个逻 辑单元(LEs),从而可以在低成本FPGA上实现复杂的数字系统。Cyclone II系列FPGA采用TSMC (台积电)的90nm工艺,与竞争对手采用 的90nm工艺的FPGA相比,其性能高出60%而功耗减低一半,而其价格则几乎可 以与ASIC产品竞争。优异的性价比使Cyclone

2、 II系列FPGA可以广泛地应用于 汽车电子、消费电子、音/视频处理、通信以及测试测量等终端产品市场。Cyclone II系列FPGA支持Alt era公司的Nios II嵌入式软核处理器。Nios II具有灵活的可配置特性而且可以非常容易地实现各种外设的扩展。对于并行 事务处理,可以在一个FPGA上放置多个Nios II软核,大大提高了处理器的效 率,也方便多个小组同时开发,进一步加快了新产品的研发速度。在数字信号处理方面,Cyclone II系列FPGA也具有明显的优势。Cyclone II 系列FPGA可以内置多达150个18x18的硬件乘法器,片上大容量的M4K RAM以 及经过专门优

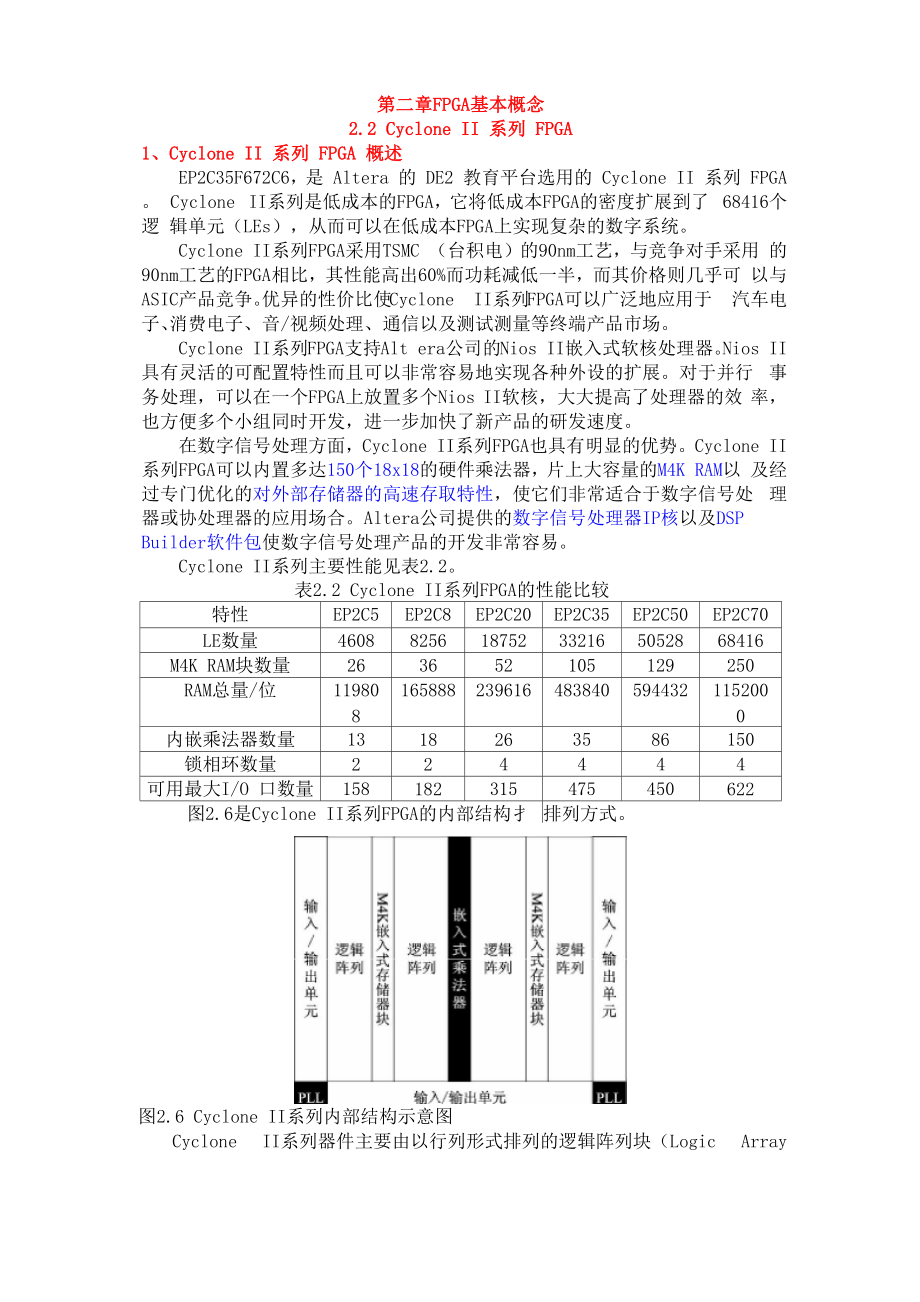

3、化的对外部存储器的高速存取特性,使它们非常适合于数字信号处 理器或协处理器的应用场合。Altera公司提供的数字信号处理器IP核以及DSP Builder软件包使数字信号处理产品的开发非常容易。Cyclone II系列主要性能见表2.2。表2.2 Cyclone II系列FPGA的性能比较特性EP2C5EP2C8EP2C20EP2C35EP2C50EP2C70LE数量4608825618752332165052868416M4K RAM块数量263652105129250RAM总量/位1198081658882396164838405944321152000内嵌乘法器数量13182635861

4、50锁相环数量224444可用最大I/O 口数量158182315475450622图2.6是Cyclone II系列FPGA的内部结构扌排列方式。图2.6 Cyclone II系列内部结构示意图Cyclone II系列器件主要由以行列形式排列的逻辑阵列块(Logic Array Block, LAB)、嵌入式存储器块及嵌入式乘法器组成,锁相环(PLL)为FPGA提 供时钟,输入/输出单元(Input/Output Elements, IOEs)提供输入/输出接口 逻辑。逻辑阵列、嵌入式存储器块、嵌入式乘法器、输入输出单元及锁相环之间 可实现各种速度的信号互连。2、逻辑单元逻辑单元是Cyclo

5、ne II系列FPGA逻辑的最小单元,它能够完成各种复杂的 逻辑应用。一个逻辑单元的主要特性如下:(1)4输入查找表相当于一个4输入的函数发生器,能够实现4变量输入 的所有逻辑。(2)一个可编程寄存器。(3 ) 一个进位链连接(Carry Chain Connec ti on)。(4)一个寄存器链连接(Regis ter Chain Connec tion)。(5)能 够驱动所有可能的互连,包括本地互连、列间、行间、寄存器链以及直接互连。(6)支持寄存器打包。(7)支持寄存器反馈。Cyclone II逻辑单元的结构如图2.7所示。ll-IJl -tLETlCrrj LAB同LAB同 寄存器打包

6、后的茅可编启图2.7 Cyclone II逻辑单元的结构每个逻辑单元(LE)都可以配置成D、T、JK或SR模式,每一个LE都有独 立的数据输入(dat al、data2、data3、dat a4 )、清除(labclrl、labclr2、DEV-CLRn)、 时钟(labclkl、labclk2、及时钟使能输入(labclkenal、labclkena2)。时钟 网络、GPIO (General Purpose Input/Output,通用输入/输出)及内部逻辑都 可以驱动寄存器的时钟及清除信号。内部逻辑及GPIO可以驱动时钟使能信号。 用于组合逻辑时,查找表旁路掉寄存器而直接驱动输出。每个

7、LE有三个输出,可以用来驱动行、列布线,直接连接布线和本地布线。 其中两个输出用来驱动行、列以及直接布线,一个输出用来驱动本地互连布线。 查找表输出和寄存器输出可以完全独立地分别驱动三个输出中的两个,即用查找 表驱动其中一个输出时,可以用寄存器的输出驱动另一个输出。由于这种做法可 以让查找表和寄存器各自独立完成互不相干的功能,因此有效提高了器件的利用 率。这种工作方式称作寄存器打包(Regis ter Packing)。在寄存器打包模式下 工作时,LAB同步加载信号无效。另外一种特殊的打包模式是把寄存器的输出反馈到同一逻辑单元的查找表 的输入,也就是说,寄存器与同一逻辑单元的查找表打包。这个逻

8、辑单元可以驱 动被寄存的或未被寄存的查找表输出。除上述的输入、输出之外,Cyclone II的逻辑单元还有一个进位链路输入 和一个进位链路输出,这种LAB内的进位链路可以使同一个LAB中的逻辑单元级 联起来。寄存器链路输出可以让同一个LAB中的查找表完成组合逻辑的任务,而 用这个LAB中的寄存器可以完成移位寄存器的功能。这样可以提高LAB间互连的 速度并节省布线资源。LE有两种工作模式:普通模式和算术模式。将LE的六个输入(四个数据输 入、进位输入和寄存器链输入)进行不同的处理可以实现不同的功能。LAB范围 的信号(时钟输入、异步清除、同步清除、同步加载及时钟使能等信号)在两种 工作模式下都是

9、有效的。Quartus II软件通过参数化模块库(Library of Parameterized Modules, LPM)自动选择LE的工作模式,用户也可根据自己的 应用来选择LE的工作模式,以提高设计的性能。LE的普通工作模式如图2.8所示,其适用于通用逻辑以及组合逻辑的场合。 在这种模式下,LE相当于一个4输入查找表,Quartus II编译器自动从data3 或进位输入(Cin)中选择一个作为4输入查找表的输入。图2.9 LE的算术工作模式LE的算术工作模式如图2.9所示,其适用于实现加法器、累加器、计数器 和比较器。算术工作模式下的LE实际上是一个2输入查找表。算术模式下工作 时,

10、查找表输出可以是带寄存器的输出,也可以是不带寄存器的输出。3、逻辑阵列块(LAB)每一个LAB包括16个LE、LAB控制信号(清除、时钟、时钟使能、复位等)、 LE进位链、寄存器进位链及LAB本地互连。LAB本地互连用以连接LAB内各个 LE。寄存器链把LAB内一个LE寄存器的输出与相邻LE寄存器的输入连在一起。 图2.10是Cyclone II系列的一个LAB的内部结构及可能的各种互连。列F|.连从相邻LAB - 块的即连从相邻-LAB来的打连捋向相邻LAE1的互连抬向相邻 -LAB 的叵连LAB 7、图2.10 LAB的结构LAB本地互连可以驱动本LAB的LE,行互连、列互连及本LAB的L

11、E的输出 可以驱动本地互连。相邻的LAB、锁相环PLL、M4K RAM块、乘法器可以通过直 接互连来驱动本地互连。直接互连减少了对列互连和行互连的占用,提高了使用 的灵活性。每个LE可通过本地互连和直接互连驱动48个LE。图2.11是LAB互 连的示意图。M4KRAM.展入式乘进 器或1OE输入的H接W连从冇侧的LAB、PLL,M4K RAM,嵌入式输HlfLA-DCl相邻 LABlKjfl.接 W连输出到右侧相邻 L点B的直接互连LAB图2.11 LAB互连示意图LAB的控制信号主要有:2个时钟、2个时钟使能、2个异步清除、1个同步 清除和1个同步加载。图2.12是LAB控制信号的示意图,其

12、最多有7个控制信 号同时可用。同步加载与寄存器打包不能同时使用。每个LAB最多可以有4个非 全局控制信号,其他的控制信号只有是全局控制信号的才可用。同步清除和同步加载信号是针对整个LAB范围而言的,即这两个信号对整个 LAB范围内的所有寄存器有效。每个LAB可以使用2个时钟信号和2个时钟使能 信号,时钟信号和时钟使能信号是同时使用的。例如,当一个LE选用了一个时 钟信号labclkl时,意味着它同时选择了 labclkenal。如图2.12所示,LAB行 时钟和LAB本地互连共同产生LAB的控制信号。本地比连lubdk Ihbclkcniil labclkJ lobdlabcJrlIflbck

13、Z图2.12 LAB控制信号示意图LAB的清除信号是针对寄存器的,LE可通过异步清除信号直接清除。每个 LAB最多支持2个异步清除信号:labclrl和labclr2LAB不支持异步加载功能。除上述的同步清除和异步清除控制之外,Cyclone II系列FPGA还支持芯片 范围的清除功能。DEV-CLRn可以清除FPGA上所有寄存器的值,而且其优先级高 于所有的控制信号。4、MultiTrack 互连Cyclone II系列FPGA内部M4K RAM、嵌入式乘法器、LE、IOE之间的互连 由釆用Direct Drive技术的MultiTrack互连结构完成。MultiTrack互连线由连续的不同

14、长度的性能经过优化的连线组成,用以进 行不同设计模块之间的通信。Direct Drive技术是专有的确定连线技术,它确 保任何功能无论在器件的什么位置都具有一致的布线。这项技术免除了由改变设 计引起的系统重优化过程,从而大大简化了模块设计的系统集成过程,使得设计 者可以自由添加、修改和移动设计的不同部分,而不会对设计的性能造成不利影 响。Cyclone II系列FPGA的MultiTrack互连由跨越固定距离的行互连(直接 连接、R4和R24)与列互连(寄存器链、C4和C6)组成。对在不同器件中实现 的布线,MultiTrack可以保证布线长度具有可预测性与重复性,从而可方便地 实现在不同密度

15、器件上的移植设计。Cyclone II系列FPGA内部各功能模块之间的互连途径见表2.3。表2.3 Cyclone II系列FPGA内部各功能模块之间的互连途径源 目 标寄存器链1 本地互连直接连接R4互连R24 互 连C4互连C16互连LEM4K RAM乘法器PLL列 IOE行IOE寄存 器链V本地 互连VVVVVV直接 连接VR4 互连VVVVR24 互连VVVVC4 互连VVVVVC16 互连VVVVLEVVVVVM4K RAMVVVV乘法 器VVVVPLLVVV列 IOEVV行IOEVVVV5、全局时钟网络及锁相环Cyclone II系列FPGA通过全局时钟网络和锁相环实现时钟管理oC

16、yclone II 系列FPGA最多可以有4个锁相环和16个全局时钟网络。每个全局时钟网络由独 立的时钟控制块来实现其时钟源的动态选择OPLL时钟输出、CLK引脚输入、DPCLK 引脚输入及内部逻辑都可以驱动全局时钟网络。不同Cyclone II器件的时钟资 源如表2.4所示。表2.4 Cyclone II器件的时钟资源器件PLL 数量CLK 引脚 数量DPCLK 引 脚数量全 局 时 钟 网 络 数 量器件PLL 数量CLK 引脚 数量DPCLK全 局 时 钟 网 络 数 量EP2C52888EP2C354162016EP2C82888EP2C504162016EP2C204162016EP

17、2C704162016Cyclone II系列中,EP2C20及以上FPGA的PLL、CLK引脚、DPCLK弓脚及 时钟控制块的分布如图2.13所示。FPGA每边有4个时钟控制块,在FPGA的4 个角的每一个角上各有两个DPCLK引脚,称作CDPCLK,这两个DPCLK引脚同时 只能有一个作为时钟输入,另一个作为GPIO使用。DPCLK1.l10DPCLK9.S图 2.13 EP2C20 及以上 FPGA 的 PLL、CLK 引脚、DPCLK引脚及时钟控制块的分布EP2C20以上的Cyclone II系列FPGA有16个时钟输入专用引脚,每边4个。 如果不作时钟输入使用,则可以通过MultiT

18、rack互连作为通用输入引脚,但只 能使用基于LE的寄存器,而不支持基于LOE的寄存器。EP2C20以上的Cyclone II系列FPGA共有20个双用途时钟输入引脚(左右 各4个、上下各2个以及芯片4个角的每个角上各2个)。CDPCLK引脚输入的时 钟信号先经过复用之后才进入时钟控制块,与其他的DPCLK相比,会产生额外的 延迟。在DPCLK的引脚输入和驱动输出之间有一个可编程延迟链,用于设定其传 播延时,可以用 Quartus II 软件中的“Input Delay from Dual-Purpose Clock Pin to Fan-Out Destinations设置延时。DPCLK可

19、以连接到全局时钟网络上 用作时钟、异步清除、预置、时钟使能信号,也可以用作类似于PCI接口中的 TRDY (Target Ready)、IRDY (Initiator Ready)和外部存储器接口中的 DQS 等协议控制信号。全局时钟网络可以为FPGA上的各种资源(如LE、IOE、嵌入式乘法器、M4K RAM)提供时钟源,也可以作为控制信号(如时钟、异步清除、预置、时钟使能 信号等),还可以用作类似于PCI接口中的TRDY、IRDY和外部存储器接口中的 DQS等协议控制信号。每一个全局时钟网络都有一个时钟控制块,用以动态选择该时钟网络的时钟 源以及使能或禁用该时钟网络。以下信号可以作为时钟控制

20、块的输入:与时钟控 制块在同一侧的4个时钟输入引脚,PLL的3个PLL时钟输出,与时钟控制块在 同一侧的4个DPCLK引脚(包括CDPCLK引脚)以及4个片内逻辑生成的信号。 但同时最多只能有2个时钟输入引脚、2个PLL时钟、1个DPCLK引脚和1个内 部信号输入。这6个输入中,2个PLL时钟和2个时钟输入引脚可以动态地选择, 以驱动全局时钟网络,而DPCLK引脚输入和内部信号输入只能静态地选择。时钟 控制块的原理如图2.14所示。图2.14中的CLKSWITCH信号可以在配置文件中设置,或者在使用手动PLL 转换特性时动态切换。CLKSELECT1.O由内部逻辑产生,当器件工作在用户模 式时

21、,可以用来动态选择时钟网络的时钟源。静态时钟的选择在配置文件中实现, 不能在用户模式下控制。在用户模式下,可以通过CLKENA动态地使能或禁止全 局时钟网络。图2.14时钟控制块的原理Cyclone II系列FPGA器件使用复用器将16个全局时钟网络组合成一个6 位总线,作为列IOE时钟、LAB行时钟和行IOE时钟,如图2.15所示。在LAB 层面上,再用复用器将6个LAB行时钟分配给该LAB中的LE寄存器。LAB行时 钟可以为LAB、M4K RAM、嵌入式乘法器和行I/O提供时钟。列OE 时丼OCLK5.U来盲全局时钟岡络的Ckckfl 5屈 LAB 厅时 ILABCLK 5. Dl时mOC

22、LK5.0图2.15 EP2C20以上器件的时钟分配Cyclone II系列FPGA的PLL为器件提供通用时钟,它具有以下特性:(1)输入时钟的倍频和分频。(2)时钟移相。(3)可编程的占空比。(4) 三个内部时钟输出。(5)个专用的外部时钟输入。(6)支持差分时钟输出。(7) 支持手动时钟切换。(8)支持三种差分时钟反馈模式。(9)锁定指示输出。(10) 具有专门的控制信号。图2.16 PLL的结构EP2C20以上的Cyclone II系列FPGA器件都有4个PLLPLL的结构如图2.16所示。PLL主要完成压控振荡器VCO的输出频率(VCO)与输入参考信号频IN经m分频后进入鉴频鉴相器PF

23、D,经PLL锁定一般k取1,也可以设置为2,当取1时,有fc。in x n m率及相位的同步。输入频率后,PFD的两个输入具有相同的频率,即IN = VCO m n x kPLLVCO1000MHz,则分辨率为 1000MHz /8_125ps输出全局时钟网络或外部时钟电路的时钟频率为=in x nm x c 。m和c的取值范围为132,n的取值范围为14。Cyclone II系列FPGA的PLL具有可编程的时钟移相能力,移相的步长最小 45o为,即移相的分辨率是压控振荡器VCO的周期除以8,如果VCO的频率为1PL的输出不仅可以驱动OU局时钟,其c2输出还可以驱动专用的PLL输出 引脚一。P

24、LL的输出频率由下式给出:in n x c其中,c分别为cO、cl和c2三个计数器的设定值。6、嵌入式存储器Cyclone II系列FPGA的存储器由多列M4K RAM块组成。M4K RAM可以灵活 地配置成各种工作模式,如真双口 RAM、简单双口 RAM、单口 RAM、ROM或者FIFO, 可以带校验位,也可以不带校验位。EP2C35有105个M4KRAM块,共483840位。 M4K RAM的特性如表2.5所示。表2.5 M4K RAM的特性最大性能250MHz包含校验位在内的 总RAM位4608支持的配置4Kxl; 2Kx2; 1Kx4; 512x8; 512x9; 256x 16; 2

25、56x 18; 128x32 (真双口模式下无效);128x36 (真双口模式下无 效)校验位每个字节一个校验位,以保证数据的完整性字节使能当写端口数据宽度为1、2、4、8、9、16、18、32或36位 时,M4K RAM块支持字节写入。字节使能将输入数据屏蔽 为特定的字节宽度,未被写入的字节则保持原有内容不变打包模式如果两个单口存储器块的尺寸都小于或等于M4K RAM块尺 寸的半且都配置成为单时钟模式,则这两个单口存储器 块可以打包成一个M4K RAM块地址时钟使能M4K RAM块支持时钟使能,在时钟使能信号有效之前,可 以一直保持之前的地址值,这种特性可以用来处理缓冲应 用中的数据丢失存储

26、器初始化文件(.mif)当M4K RAM块被配置成RAM或ROM时,可以使用存储器初 始化文件初始化存储器的内容加电条件加电时M4K RAM块输出自动清除寄存器清除只有输出寄存器可以清除写入时同端口读新数据在时钟上升沿有效写入时混合端口读旧数据在时钟上升沿有效可以把M4K RAM块配置成各种模式的存储器,如表2.6所示。M4K RAM块支 持4种时钟模式,表2.7列出了不同的时钟模式。表2.8列出了不同存储器模式 下能够使用的时钟模式。表2.6 M4K RAM块的存储器模式存储器模式说明单口存储器当不需要同时读/写时,M4KRAM块可以配置成单口存储器模式简单双口存储 器简单双口存储器模式支持

27、对存储器的同时读/写真双口存储器真双口存储器模式支持任何形式的双口存储器操作:同时进行 两个读、两个写或工作在不同时钟频率的一个读一个写操作混合宽度的简 单双口存储器混合宽度的真双口存储器模式是允许读/写端口宽度不同的简 单双口存储器混合宽度的真 双口存储器混合宽度的简单双口存储器模式是允许读/写端口宽度不同的 真双口存储器嵌入式移位寄 存器用M4KRAM块实现移位寄存器,每个时钟的下降沿写入,上升 沿读出ROMM4K RAM块支持ROM模式,ROM中的内容由.mif文件初始化FIFO缓冲器用M4K RAM块可以实现单时钟或双时钟的FIFO,但不允许对空 FIFO进行同时读/写表2.7 M4K

28、 RAM块的时钟模式时钟模式说明独立时钟 模式这种模式下,M4K RAM块的A 口和B 口分别采用不同的时钟,时钟A 控制A 口所有的寄存器,时钟B控制B 口的所有寄存器输入/输 出时钟模 式两个时钟,一个控制所有的控制输入奇存器,包括输入数据、wren 以及地址;而另外一个控制M4K RAM块的所有控制输出寄存器读/写时 钟模式可以有两个时钟,与时钟控制数据输入、wraddress和wren读时钟 控制数据输出、rdaddress和rden单时钟模 式用一个时钟和一个时钟使能来控制所有的寄存器,这种模式不支持 异步清除表2.8 M4K RAM块在不同存储器模式下可以使用的时钟模式时钟模式真双

29、口模式简单双口模式单口模式独立时钟模式V输入/输出时钟模 式VVV读/写时钟模式V单时钟模式VVV来自相邻LAB块的直接互连、R4互连和C4互连都可以驱动M4K RAM的本地 互连,最多可达16根线的M4K RAM块的数据输出可以直接驱动R4互连、C4互 连以及左右相邻的LAB直接互连。LAB行时钟提供M4K RAM块的时钟,M4K RAM 块的本地互连将来自M4K相邻的LAB块的直接互连、R4互连和C4互连的信号转 换为地址信号与数据输入信号。图2.17所示为M4K RAM块的布线。嵌入式乘法器为Cyclone II系列FPGA提供了数字信号处理(Digital Signal Process

30、ing, DSP)的能力,可以用来实现快速傅里叶变换(FFT)、离散余弦变 换(DCT)及有限脉冲响应(FIR)等数字信号处理,使Cyclone II系列FPGA 可以高效地用于音频/视频信号处理。Cyclone II系列FPGA的嵌入式乘法器可 以配置成9x9或18x18的乘法器进行工作,在这两种工作模式下,如果同时使用 输入/输出寄存器,则最高性能可达到250MHz。各种器件的乘法器资源见表2.9。表2.9 Cyclone II系列乘法器资源器件嵌入式乘 法器列嵌入式乘 法器数量可以使用的9x9的嵌 入式乘法器数量可以使用的18x18的嵌 入式乘法器数量EP2C51132613EP2C81

31、183618EP2C201265226EP2C351357035EP2C5028617286EP2C703150300口口人 、/ -150嵌入式乘法器由两个输入寄存器、一个乘法单兀、一个输出寄存器以及相关 的控制信号组成,其内部结构如图2.18所示。如表2.9所示,嵌入式乘法器按 列排列,根据器件的不同,可以是1 3列。嵌入式乘法器的高度与LAB行的高度一样。嵌入式乘法器在Cyclone II系列FPGA中的位置如图2.19所示。图2.19嵌入式乘法器在Cyclone II中的位置乘法器的接口布线如图2.20所示。来自相邻LAB块的直接互连、R4互连和 C4互连都可以驱动乘法器的行接口互连,

32、乘法器可以通过行接口互连与左右相 邻的LAB通信。左右LAB块最多可以各有16根信号线与乘法器的行接口互连连 接。乘法器的行接口互连提供乘法器的输入,乘法器可以直接输出到R4互连、 C4互连或左右LAB的本地互连。爺出宜相邯LAR戏:相邻LABLABt 互建区黑自相邦圧别倉捜连接前互樓连按厅樓11快族入式乘法蛊3灯冇36 LAB块h连04銘Cunlnd ,?5.0图2.20乘法器的接口布线乘法器有两种工作模式:9x9模式和18x18模式。图2.21是乘法器的18位 工作模式,此时乘法器配置成一个18x18的乘法器。这种模式下的两个输入操作 数最多可以是18位,它们可以是符号数,也可以是无符号数

33、,输入/输出都可以 寄存。9x9模式下,一个嵌入式乘法器块可以配置成两个9x9的乘法器,这种模式 下每个乘法器的两个输入操作数最多可以是9位,可以是符号数,也可以是无符 号数,输入/输出都可以寄存。每个乘法器只有一个signa和一个signb,当一 个乘法器用作两个9x9的乘法器时,输入数据A的两个输入符号必须相同,输入 数据B的两个输入也必须具有相同的符号表示。图2.22是嵌入式乘法器的9位 工作模式。IhrA AI7.OiblrlllXLHg图2.21乘法器的18位工作模式图2.22乘法器的9位工作模式Quartus II 软件通过宏功能模块(Mega function)的 MegaWiz

34、ard Plug-In Manager对乘法器的工作模式和参数进行配置。Altera提供了使用乘法器的两种 方法:例化和推断。这两种方法都是通过对1pm_mult (相乘)、altmult_add (乘 加)、altmult_accum (相乘累加)等三个宏功能模块的调用来实现的。8、IOE的结构及特性Cyclone II系列FPGA支持多种单端I/O标准,这些标准包括LVTTL、LVCMOS、 SSTL-2、 SSTL-18、 HSTL-18、 HSTL-15、 PCI 和 PCI-X。当FPGA与其他高级存储器件如双倍数据速率存储器(DDR和DDR2)、SDRAM 和QDRIISRAM等器

35、件一起工作时,单端I/O标准是关键因素。表2.10列出了 Cyclone II器件支持的单端I/O标准及其目标性能。表2.10 Cyclone II器件支持的单端I/O标准及其目标性能I/O标准目标性能/MHz典型应用3.3V/2.5V/1.8V LVTTL167通用3.3V/2.5V/1.8V/1.5V LVCMOS167通用3.3V PCI66个人电脑(PC),嵌入式应用3.3V PCI-X100PC,嵌入式应用2.5V/1.8V SSTL Class I167存储器2.5V/1.8V SSTL Class II133/125存储器1.8V/1.5V HSTL Class I167存储器1

36、.8V/1.5V HSTL Class II100存储器与单端I/O标准相比,Cyclone II器件的差分信号能提供更好的噪声容限, 产生的电磁干扰(EMI)更低,功耗也更低。表2.11列出了 Cyclone II器件支 持的差分I/O标准及其目标性能。表2.11 Cyclone II器件支持的差分I/O标准及其目标性能I/O标准目标性能典型应用LVDS接收端805Mb/s,发送端622Mb/s芯片到芯片接口应用,背板驱动Mini-LVDS170Mb/s通用RSDS170Mb/s通用LVPECL150MHz只用于时钟输入差分HSTL167MHz存储器差分SSTL167MHz存储器图2.23所

37、示为Cyclone II系列FPGA器件的LVDS接口,图2.24所示为 Cyclone II 系列 FGPA 的 RSDS 和 mini-LVDS 接口。图 2.23 Cyclone II 系列 FPGA 器件的 LVDS 接口图 2.24 Cyclone II 系列 FGPA 的 RSDS 和 mini-LVDS 接口。在FPGA市场上,Cyclone II器件扩展了 FPGA在低成本、大批量领域中的 应用。FPGA如今不再仅限于外围应用,也可以在系统中执行很多关键性的处理 任务。随着FPGA越来越多地应用于系统的数据路径,当系统存储需求超过片内 丰富的存储器资源时,FPGA必须具有与外部

38、存储器件连接的接口。Altera通过和业界领先的存储器供应商合作,确保了用户能够将最新的存 储器器件连接至Cyclone II系列FPGA。Cyclone II器件被设计成为能够通过一 个专用的接口与各种标准的存储器进行通信,保证快速可靠的数据传输,传输速 率最高达到668Mb/s。表2.12总结了 Cyclone II器件支持的外部存储器接口。表2.12 Cyclone II器件支持的外部存储器接口存储技术I/O标准最大总 线宽 /bi t最大时钟 速度/MHz最大数据 速率/(Mb/s)SDR SDRAM3.3V LVTTL72167167DDR SDRAM2.5V SSTL Class I, II72167334DDR2 SDRAM1.8V SSTL Class I, II72167334QDR II SRAM1.8V HSTL , Class I ,III36167668

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。