低温共烧多层陶瓷电

低温共烧多层陶瓷电

《低温共烧多层陶瓷电》由会员分享,可在线阅读,更多相关《低温共烧多层陶瓷电(16页珍藏版)》请在装配图网上搜索。

1、中国电子科技集团公司第四十三研究所技术文件低温共烧多层陶瓷电路设计规范一、 介绍本设计规范是根据LTCC生瓷带供应商提供的设计规范制定的,适用于军用及民用LTCC电路模块、微波电路模块的基本设计。此文件所包含的信息,接受者没有四十三所的同意不得向第三者提供。这份文件定义了标准的或最大的工艺叁数,在这份文件中的数据并不是 LTCC 的设计极限。为了提高电路的性能和降低成本以及工艺技术的提升会随时对本文件进行修改。如:工艺技术的进化;新材料的发展;客户的新需要;来自客户经验的反馈;根据特定的需要, 经技术人员认可也可以超越该规范的限制。请经常和连络我们的技术部门,获取更多的信息和建议。二、引用文件

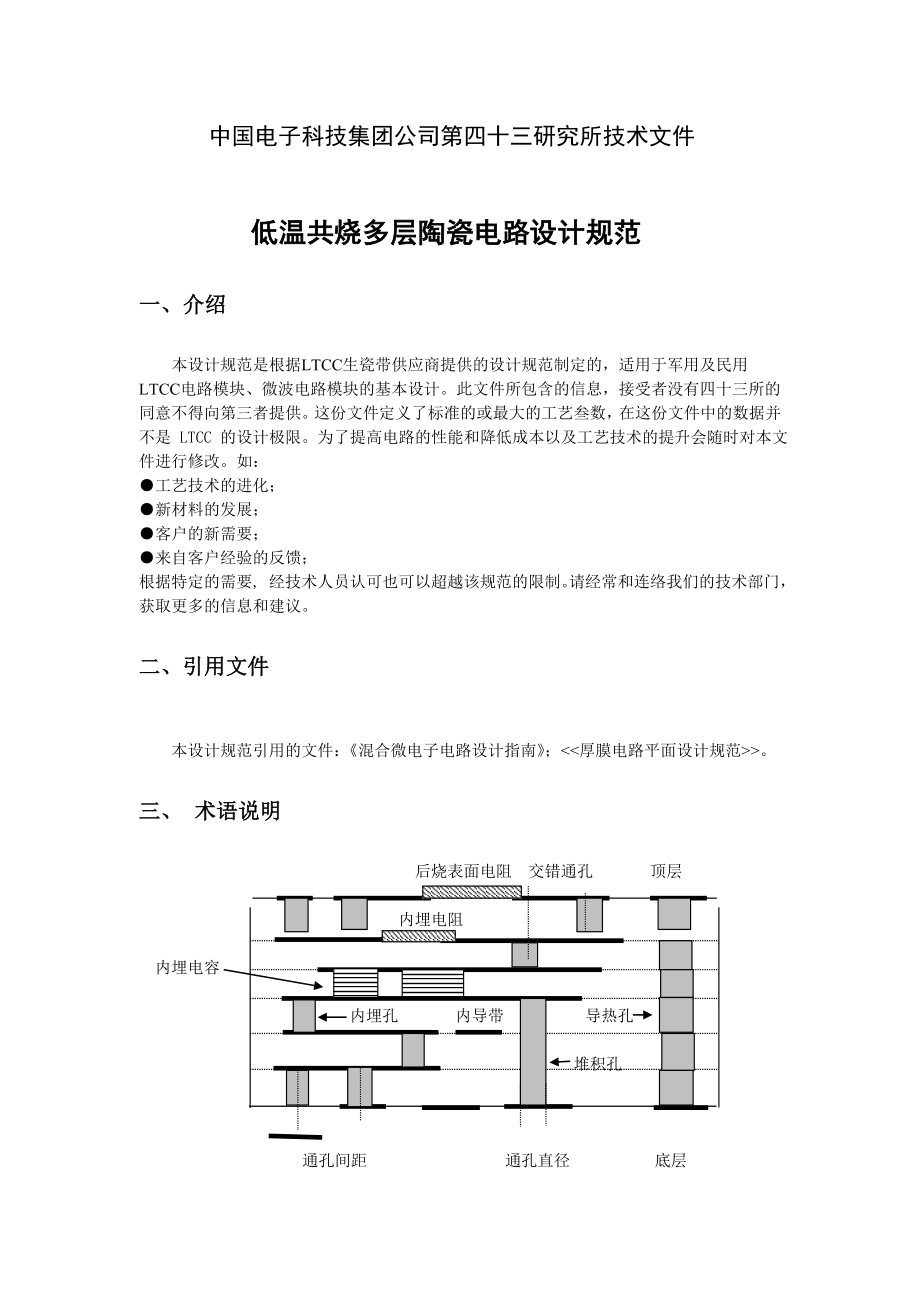

2、本设计规范引用的文件:混合微电子电路设计指南;。 三、 术语说明 后烧表面电阻 交错通孔 顶层内埋电阻内埋电容内埋孔 内导带导热孔堆积孔通孔间距 通孔直径底层 四、 材料系统目前生产线上使用的LTCC材料组要有DuPont 951、HL2000。用于高频电路的低损耗微波LTCC介质带材料:Ferro A6 、DP943。导体材料根据客户需要采用金系统和混合系统(外层是可以焊接的Pd/Ag导体及可丝焊的金导体,内层是Ag导体)。LTCC生瓷带介质材料特性见表1表1、生瓷带介质材料数据性质DP951DP943Ferro A6S/M厚度1)951 C2 50 um951PT 114 um951P2

3、165 um951PX 254um943C2 50 um943P5 127 um943PX 254um0.094、0.187烧结收缩率(X、Y)12.70.3%9.50.3%15.50.3%烧结收缩率(Z)150.5%10.30.5%250.3%介电常数7.8(10MHz) 7.4(15G)5.9(10MHz)介质损耗0.2%(10MHz)0.09%0.15%(10MHz)绝缘电阻1012(100VDC)1012(100VDC)1014(100VDC)击穿电压1000V/25um1000V/25um1000V/25um热导率3W/mk4.4W/mk2W/mk热胀系数5.8ppm/K6 ppm/

4、K7.8ppm/K烧结密度3.1g/23.2g/22.5g/2抗折强度320MPa230 MPa130MPa表2、导体材料性能导体特性陶瓷材料系统Du Pont 951陶瓷材料系统Ferro A6 S/M导体类型内层 Ag, Au外层Ag, Au, PdAg 内层 Ag, Au外层Ag, Au, PdAg顶层导体膜厚(m) 10 310 3内层导体膜厚(m)7 to 15 27 to 15 2电阻 m / 顶层(10 m)Au 4Ag 3AgPd 30Au 4Ag 3AgPd 30电阻 m / 内层Au 4Ag 3Au 4Ag 3顶层导体粗糙度 (Rq m RMS) (后烧)Au: 0.8Ag

5、: 0.9五、 电路布线版图布局目前我们二种布图尺寸,见下图。一种为140140mm(可用面积)。170mm瓷片尺寸 140mm 对位标志 140 mm 切割线 可用面积 电路 图2、6Inch6Inch基片布图尺寸 在电路布图时,各层的电路版图一定要设计上对位标记和对位孔,对位标记和对位孔的物理位置一定要重合,表层版图要设计上电路的切割线,但不要边框。在瓷片的可用面积范围内分布多块电路。注:以上尺寸为烧结前尺寸。六、基板尺寸及误差基板尺寸最大可达125125mm2,基板尺寸误差一般0.5%。烧结后基板电路图形收缩误差0.3%。 最小的基板厚度为500um,厚度误差为0.6%。七、通孔7.1

6、通孔尺寸通孔尺寸为100 um、200um、250um、300um,采用高速转床或冲床在生瓷带上形成。烧结后通孔尺寸为97um、180um、220um、260um。通孔尺寸推荐与生瓷带厚度接近,推荐在各层中使用一种通孔尺寸,两种通孔尺寸在不同层中也是容许的。7.2 通孔覆盖区连接直径小于250um通孔的导带,应有一个圆形或方形通孔覆盖区,通常是:直径比通孔直径大50um,最优100um。后烧结表面导体通孔覆盖区直径要400um。7.3 通孔间距最小通孔节距(中心距),同一层内应为2.5通孔直径,两层间交错通孔错位为2通孔直径,最小通孔中心,距基板边沿距离应为3通孔直径。 25via 2via

7、3via7.4 堆积孔堆积通孔通过各层是可以接受的。但堆积通孔会导致表面通孔金属的凸起,我们推荐采用交错通孔以避免这种情况,最好是堆积通孔不要超过两层。在需要密封焊的地方,最上面两层最好采用交错通孔。7.5 热通孔热通孔直径我们推荐951AT为200um、951A2为250um、951AX为300um(为烧结前尺寸)。热通孔最小中心距为3Via,最大热通孔阵列6.56.5,最小热通孔阵列到基板边缘距离为4。7.4 RF 通孔设计需要高频线和受约束的阻抗线可能需要埋置同轴型屏闭,通过经由受约束线两边平行放置穿越外面的通孔来实现。射频通孔间距可以小到50um(在不同层上平行放置),只要它们是相互连

8、同的。射频通孔也可以是堆积的,只要通孔的中心距大于2.5倍的通孔,见下图。 RF 通孔顶视图八、导体 F E C B A D G H8.1 线宽、线间距项目标准高密度通孔覆盖区直径E(um)250100线孔距C(um)200100导体间距B(um)15075导体线宽A(um)15075线到基板边缘距离D(um)300200焊接框区到基板边缘距离(um)150100SMD焊区到通孔覆盖区距离F(um)200100SMD焊区到导带距离(um)200100SMD焊区到基板边缘距离H(um)500300顶层导体线宽容差(m)15m内导体线宽容差(um)15m8.2 地和电源 250um 300um 5

9、50um B 地和电源应尽可能地采用删格状结构,导体覆盖面积应小于50%,最佳是采用250um-400um线宽,550um间距。经技术人员认可大面积电源和地也是可以的。外层接地和电源面可采用大面积块状结构(后烧结)。相邻层删格面应有一定的位移,保证基板厚度均匀一致。局部地方可使用块状地和电源,来提高电路的RF性能。连接到删格上的通孔,其覆盖区可采用方行结构,这样可使电流同时流到几个删格线上。过孔到删格线最小距离为300um(B)。8.3 电阻 电阻可制作下列方阻 表2、表面电阻方阻温度系数稳定性精度(调阻)精度(不调阻)20200ppm0.5%1 %20 %100100ppm0.5%1 %20

10、 %1K100ppm0.5%1 %20 %10K100ppm0.5%1 %20 %100K100ppm0.5%1 %20 %1M100ppm0.5%1 %20 %表2、内埋电阻方阻温度系数稳定性精度100200ppm0.5%30 %1K200ppm0.5%30 %10K200ppm0.5%30 % 表准400um 搭界表准250um 最小250um 端头 宽度 最小250um 长度 探针PAD 最优通孔位置 最小电阻尺寸()0.80.8电阻图形调阻刀口8.4 埋置电容LTCC中可以采用不同的技术来制作电容,最常用的技术是利用陶瓷带本身来制作电容, 其=7.8材料,烧结厚度0.89mm,可以获得

11、0.0005pF/mil2的电容密度。电容容差可以从瓷带的厚度变化算得,下表给出电容大小和计算的电容值例子,没有考虑边缘效应,它增加有效电容。表2、K=7.8瓷带电容(t3.5mil)C(Pf)方形电极长度(inch)10.04520.06330.07740.08950.100100.141200.200300.245400.283500.316另外一种技术是在生瓷带上印刷介质浆料可获得大容量的电容。 8.5 埋置电感ItemStdAdv.a Line Width m10075b Line Spacingm15075c Line to Substrate Edgem200150d Via Ho

12、le Diameterm100e Via Hole Cover Diameterm250100f Via Cover to Substrate Edge m400300九、空腔空腔是在迭压、烧结前在生瓷片上冲制而成,任何空腔设计在接受之前应审查。 B E F D A C空腔底层最小烧结厚度为380um,最优为430um。空腔壁的宽度应大于3.0(B)。通孔边缘到腔壁的距离最小应为2.5通孔直径。(C)空腔底导带到空腔壁距离最小应为200um(D)。内埋或表面导体到腔壁最小距离应为250um(E)。丝焊台最小宽度为0.8(F)。十、封装形式10.1 卡式引线间距为2.54mm和1.27mm的卡式

13、引线通常使用。为表面安装和过孔安装应用,从卡式引线制造商可获得不同引线结构。卡式引线焊区印刷在基板的顶层和底面。 0.125mm 0.125mmmin0.5mm min0.5mm 1.27mm 2.54mm10.2 BGA BGA可以用直径0.89mm的Pb90/Sn10焊球以Sn96/Ag4焊料焊接到基板背面,焊接区直径为0.86mm。X、Y方向间距为1.5mm。 1.5mm 0.86mm 通孔位置,典型位于中心 10.3塑料封装10.4 金属外壳封装 封装形式参见厚膜混合集成电路封装。十一、丝焊区丝焊区采用印刷金浆,满足铝丝或金丝焊接。布图结构应如下图。项目标准高级Am200150Bm35

14、0250Cm200150Dm200150埋置芯片倒扣焊芯片Item.StdAdva Pad Diameter m180150b Pad Pitch m240200c Via Diameter m100十二、密封焊 对于芯片元件的密封焊接,金属框架可以用Au80/Sn20焊料焊接到基板上。硬焊导体有两种,第一种是为了附着,第二种是为了焊接。硬焊导体应比框架边缘宽1mm。焊接层导体应比附着层导体宽100um。基板最小厚度应为0.8mm。密封焊区顶层以下(包括顶层)两层不应有布线导体。 盖板框 导体倒角根据盖板 框而定 密封焊导体图形十三、片式阻容元件及芯片焊(粘)接区的设计片式阻容元件及芯片焊(粘

15、)接区的设计,参见厚膜电路平面设计规范(43所1996-06-20发布DS5-002)。十四、设计传递14.1 设计注意事项所有的设计必须使用同一种设计结构。所有的的对位标记和切割线宽150um。所有设计具有相同的原点,170170mm在中心。14.2 各层命名所有层推荐用图10命名规则来命名,层数由顶层到底层数字为1、2、3 L1ab 基板顶层 L1aa L1a L1 Via1 L2 Via2 L3 Via3 。 。 。 L6 Via6 L7 Via7 L8 Via8 L8b L8ba 基板底面 L8bb 各层命名规则在各文件后应说明用途:通孔(Via1,2,3)内层导带(L2,3)内层不同

16、金属导带(Lna, PdAg-bond Au)顶层各金属化导体(Ag,PdAg,PtAu,PtPdAg,Au等)。顶层电阻(各方阻)顶层包封顶层介质底面各金属化导体(Ag,PdAg,PtAu,PtPdAg,Au等)底层电阻(各方阻)底层包封底层介质14.3 需要的资料14.3.1每层通孔的数据文件170170mm 2,3或2,4格式,Leading14.3.2各层图形文件:格式:.ACAD .DWG UP TO VERSION 2000 .DXF UP TO 2000.CAM350 UP TO V.6.GERBERPROTEL99 OR PROTEL SE文件采用英制单位。提供一个文本文件,包

17、括联系资料、数据格式、各层电路通孔文件列表,通孔直径、每层通孔数量。示范file: readme.txt Designer: phone: e-mail: List of files: L1ab.gbr, L1aa.gbr, L1a.gbr, L1.gbr, L2.gbr, L3.gbr. via1.dri, via2.dri, via3.dri, .Conductor Layers:Format: GerberRS-274XUnits: MetricType: AbsoluteDigits: Integer:3 Decimal:3Zero suppression: noneVia Layer

18、s:Format: GerberRS-274XUnits: MetricType: AbsoluteDigits: Integer:3 Decimal:3Zero suppression: none Via Layer Tool size Via count Via1.dri 0.2 210 Via2.dri 0.2 712Via3.dri 0.2 712Via4.dri 0.2 1212Via5.dri 0.2 521Via6.dri 0.25 416Via7.dri 0.25 35814.3.3网络表文件格式:.CAM350 UP TO V.6MENTOR(最优).GERBER.RS274

19、 WITH APERTURE FILE.RS274X (PREFERRED)网络文件要包括元件编号和管脚号见下图 13 12 11 10 9 1 8 U1 7 2 6 3 4 5网络列表格式:CAM350 (PREFERRED).MENTOR(PREFERRED).EXCEL.MS WORD.TXT $Net1U8-1U8-23 R5-1 JR -134$Net2U12-71 U5-171 U5-169 U5-173$Net3 U5-158U12-182$Net4 U12-184U5186$Net5 U5U5-188 U5U5-194 U12U12-103 U12U12-115$Net6 U1

20、2U12-160U5-196JR -155$Net7 U5-192 U5U5-198 U5-200$Net8 U12-162JR -154U5-202$Net9 JT -189U12-13 JT 197$Net10 U5-208 U12-14$Net11U5-209U12-153 U10-4十五、注意事项13.1 线路设计人员应按照本设计规范进行平面设计,所有平面版图须按规定的程序审核。13.2 线路审核人员须核校平面布线与电路设计图是否一致,确保电路连接关系正确。13.3 工艺技术人员应认真审核导体、通孔、通孔覆盖区等设计是否满足本设计规范要求。13.4 要保证本规范推荐与优选的版图尺寸数据与基板尺寸数据相匹配。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。