第五部分时序逻辑电路教学课件

第五部分时序逻辑电路教学课件

《第五部分时序逻辑电路教学课件》由会员分享,可在线阅读,更多相关《第五部分时序逻辑电路教学课件(105页珍藏版)》请在装配图网上搜索。

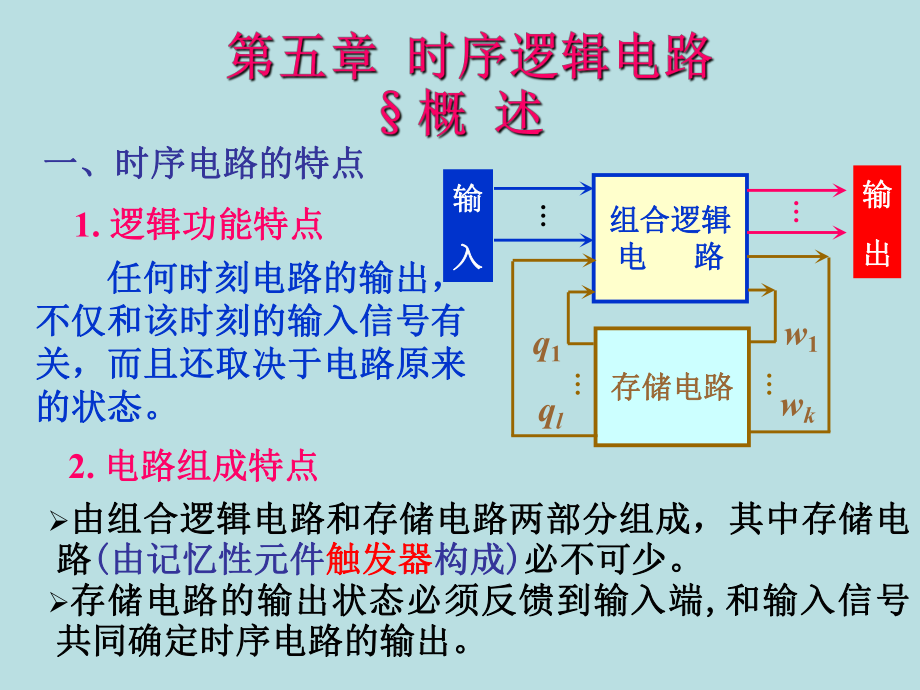

1、一、时序电路的特点一、时序电路的特点1.逻辑功能特点逻辑功能特点 任何时刻电路的输出,任何时刻电路的输出,不仅和该时刻的输入信号有不仅和该时刻的输入信号有关,而且还取决于电路原来关,而且还取决于电路原来的状态。的状态。2.电路组成特点电路组成特点组合逻辑组合逻辑电电 路路存储电路存储电路x1xiy1yjw1wkq1ql输输入入输输出出由组合逻辑电路和存储电路两部分组成,其中存储电由组合逻辑电路和存储电路两部分组成,其中存储电路路(由记忆性元件由记忆性元件触发器触发器构成构成)必不可少。必不可少。存储电路的输出状态必须反馈到输入端存储电路的输出状态必须反馈到输入端,和输入信号和输入信号共同确定时

2、序电路的输出。共同确定时序电路的输出。二、时序电路逻辑功能表示方法二、时序电路逻辑功能表示方法1.逻辑表达式逻辑表达式(1)输出方程输出方程)(),()(nnntQtXFtY(3)状态方程状态方程)(),()(1nnntQtWHtQ (2)驱动方程驱动方程)(),()(nnntQtXGtW 2.状态表、卡诺图、状态图和时序图状态表、卡诺图、状态图和时序图组合逻辑组合逻辑电电 路路存储电路存储电路x1xiy1yjw1wkq1qlJK 触发器触发器(也是时序电路)(也是时序电路)x1y1y2JKQ1Q1x21J1KC1CPw1w2q2q1三、时序逻辑电路分类三、时序逻辑电路分类1.按逻辑功能划分:

3、按逻辑功能划分:计数器、寄存器、读计数器、寄存器、读/写存储器、写存储器、顺序脉冲发生器等。顺序脉冲发生器等。2.按时钟控制方式划分:按时钟控制方式划分:同步时序电路同步时序电路电路中各个触发器共用一个时钟电路中各个触发器共用一个时钟 CP,要更新状态的触发器同时翻转。要更新状态的触发器同时翻转。异步时序电路异步时序电路电路中所有触发器没有共用一个电路中所有触发器没有共用一个 CP。3.按输出信号的特性划分:按输出信号的特性划分:)()(nntQFtY)(),()(nnntQtXFtY 存储存储电路电路Y(tn)输出输出WQX(tn)输入输入组合组合电路电路CPY(tn)输出输出CPX(tn)

4、输入输入存储存储电路电路组合组合电路电路组合组合电路电路Q(tn)W(tn)5.1.1 时序电路的基本分析方法时序电路的基本分析方法一、一、分析的一般步骤分析的一般步骤时序电路时序电路时钟方程时钟方程驱动方程驱动方程状态图状态图时序图时序图CP触触发发沿沿特性方特性方程程输出方程输出方程状态方程状态方程计算计算,列状态表列状态表二、二、分析举例分析举例时钟方程时钟方程(可略)(可略)CPCPCPCP 210输出方程输出方程nnnQQQY012 驱动方程驱动方程nnQK,QJ2020 nnQK,QJ0101 nnQK,QJ1212 状态方程状态方程特性方程特性方程nnnnnnQQQQQQ2020

5、210 nnnnnnQQQQQQ0101011 nnnnnnQQQQQQ1212112 【例例 5.1.1】解解 1J1KC10Q0Q1J1KC11J1KC11Q2Q1Q2Q&FF1FF0FF2CPY1nnnQJQKQnnQQ210 nnQQ011 nnQQ112 nnnQQQY012 现现 态态 次次 态态 输输 出出 Q2 Q1 Q0 Q2 Q1 Q0 Y0 0 110 1 111 0 111 1 100 0 010 1 011n+1 n+1 n+1nnn0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 0 01 1 11 1 01CP Q2 Q1 Q0 Y0123

6、45010 0 010 0 110 1 111 1 111 1 0101 0 00 1 011 0 11CP Q2 Q1 Q0 Y012345010 0 010 0 110 1 111 1 111 1 0101 0 00 1 011 0 11000001/1011/1111/1110/1100/1/0有效状态和有效循环有效状态和有效循环010101/1/1无效状态和无效循环无效状态和无效循环能自启动:能自启动:存在无效状态,但没有形成循环存在无效状态,但没有形成循环不能自启动:不能自启动:无效状态形成循环无效状态形成循环所以,该电路不能自启动所以,该电路不能自启动能否自启动能否自启动?0000

7、01/1011/1111/1110/1100/1/01 2 3 4 5 6CPCP下降沿触发下降沿触发Q2Q1Q0000001011111110100000Y 5.1.2 时序电路的基本设计方法时序电路的基本设计方法 根据给定的逻辑功能,确定输入变量和输出变量根据给定的逻辑功能,确定输入变量和输出变量及电路的状态数,并用相应的字母表示及电路的状态数,并用相应的字母表示 定义输入、输出变量和电路的状态,并对电路的定义输入、输出变量和电路的状态,并对电路的状态进行编号状态进行编号 画出原始的状态图或列出原始的状态表画出原始的状态图或列出原始的状态表 时序电路的设计是根据已知逻辑功能,设计出时序电路

8、的设计是根据已知逻辑功能,设计出能够实现该逻辑功能的最简单的电路。能够实现该逻辑功能的最简单的电路。【设计步骤】【设计步骤】1)进行逻辑抽象,得出原始状态图进行逻辑抽象,得出原始状态图2)状态化简:)状态化简:合并等价状态合并等价状态3)状态分配)状态分配:据电路的状态数:据电路的状态数M确定所用触发器数确定所用触发器数目目n所需满足的式子:所需满足的式子:22n1-n M4)确定触发器的类型,并求出电路的状态方程、驱动)确定触发器的类型,并求出电路的状态方程、驱动方程和输出方程:方程和输出方程:确定触发器类型确定触发器类型(JK或或D)后,根据状后,根据状态图求出状态方程和输出方程,进而求出

9、驱动方程态图求出状态方程和输出方程,进而求出驱动方程5)画逻辑图)画逻辑图:根据驱动方程和输出方程根据驱动方程和输出方程6)判断电路能否自启动)判断电路能否自启动然后给电路的每种状态分配与之对应的触发器状态组合然后给电路的每种状态分配与之对应的触发器状态组合设计一般步骤:设计一般步骤:时序逻辑时序逻辑问题问题逻辑逻辑抽象抽象状态图状态图(表)(表)状态状态化简化简最简图最简图(表)(表)状态方程状态方程求出求出驱动方程驱动方程选定触发选定触发器的类型器的类型逻辑逻辑电路图电路图检查能否检查能否自启动自启动2.设计举例设计举例按如下状态图设计时序电路。按如下状态图设计时序电路。000/0/0/0

10、/0/0001010011100101/1nnnQQQ012 解解 已给出最简状态图,若用同步方式:已给出最简状态图,若用同步方式:00 01 11 1001 nQ2nnQQ01Y000 001 02QQY 为方便,略去为方便,略去右上角右上角 标标n。00 01 11 1001 nQ2nnQQ0110 nQ101010 010QQn 11 nQ0100101211QQQQQQn 12 nQ0011020112QQQQQn 【例例 5.1.2】010QQn 0101211QQQQQQn 020112QQQQQn 选用选用 JK 触发器触发器100 KJ01021,QKQQJ 约束项约束项022

11、201)(QQQQQQ 02201201QQQQQQQQ 02201QQQQQ CP1KC1FF1&1JY1J1KC1FF01KC1FF2&1J1&110111000能能自启动自启动/0/102012 QK,QQJ 1nnnQJQKQ1/1【例例 5.1.3】设计设计 一个串行数据检测电路,要求输入一个串行数据检测电路,要求输入3 或或 3 个以上数据个以上数据1时输出为时输出为 1,否则为,否则为 0。解解 S0 原始状态原始状态(0)S1 输入输入1个个1S2 连续输入连续输入 2 个个 1S3 连续输入连续输入 3 或或 3 个以上个以上 1S0S1S2S3X 输入数据输入数据Y 输出数

12、据输出数据0/01/00/01/00/00/01/1S0S1S20/01/00/01/00/01/10/00/0S0S1S20/01/00/01/00/01/1M=3,取取 n=2S0=00S1=01S2=110001110/01/00/01/00/01/1选选 JK()触发器触发器,同步同步方式方式Q1nQ0nX0100 01 11 10Y000001 nXQY1 Q11nnXQQ011 Q01XQn 10nnXQQ011 nnnnQXQQXQ1010 nnQXQ01 约束项约束项nnnQXQXQ101 XQn 10nnQXXQ00 nXQJ01 XK 1XJ 0XK 01nYXQ&CPX1

13、Y1J1KC1FF0Q0无效状态无效状态 10000010000/01111 111/1能自启动能自启动Q11KC1FF1&1J5.2.1 计数器的特点和分类计数器的特点和分类一、计数器的功能及应用一、计数器的功能及应用1.功能:功能:对时钟脉冲对时钟脉冲 CP 计数。计数。2.应用:应用:分频、定时、产生节拍脉冲和脉冲序列、分频、定时、产生节拍脉冲和脉冲序列、进行数字运算等。进行数字运算等。二、计数器的特点二、计数器的特点1.输入信号:输入信号:计数脉冲计数脉冲 CPMoore 型型2.主要组成单元:主要组成单元:时钟触发器时钟触发器三、三、计数器的分类计数器的分类按数制分:按数制分:二进制

14、二进制(2n进制进制)计数器计数器十进制计数器十进制计数器N 进制进制(任意进制任意进制)计数器计数器按计数按计数方式分:方式分:加法计数器加法计数器减法计数器减法计数器可逆计数可逆计数(Up-Down Counter)按触发器翻转按触发器翻转是否同步分:是否同步分:同步计数器同步计数器(Synchronous )异步计数器异步计数器(Asynchronous )按开关按开关元件分:元件分:TTL 计数器计数器CMOS 计数器计数器一、二进制同步计数器一、二进制同步计数器1.3位位二进制同步加法计数器二进制同步加法计数器(1)结构示意框图与状态图结构示意框图与状态图3位二进制同步位二进制同步加

15、法计数器加法计数器CP C输入计数脉冲输入计数脉冲送给高位的进位信号送给高位的进位信号000001/0010/0011/0100/0101/0110/0111/0/1排列:排列:Q2n Q1n Q0nff/2f/4f/8 CP Q0Q1Q2100010110001101011111Z12345678f/8所以,计数器也称为分频器所以,计数器也称为分频器FF2、FF1、FF0Q2、Q1、Q0设计方法一:设计方法一:按前述设计步骤按前述设计步骤(2)(3)(4)(P297 299)(具体过程略)可得:(具体过程略)可得:(2)分析和选择触发器分析和选择触发器C=Q2n Q1n Q0nJ0=K0=1

16、J1=K1=Q0J2=K2=Q1Q0FF2、FF1、FF0Q2、Q1、Q0设计方法一:设计方法一:按前述设计步骤按前述设计步骤(2)(3)(4)(P297 299)(具体过程略)可得:(具体过程略)可得:(2)分析和选择触发器分析和选择触发器C=Q2n Q1n Q0nJ0=K0=1J1=K1=Q0J2=K2=Q1Q0J0=K0=1J1=K1=Q0J2=K2=Q1Q0CP1J1KC1FF011J1KC1FF11J1KC1FF2&CQ0Q1Q2Q0Q1Q2串行进位串行进位触发器触发器负载均匀负载均匀CP1J1KC1FF011J1KC1FF11J1KC1FF2&CQ0Q1Q2Q0Q1Q2并行进位并行

17、进位低位触发低位触发器负载重器负载重用用T 触发器触发器(由由JK触发器转换而成触发器转换而成)构成的逻辑电路图构成的逻辑电路图设计方法二:设计方法二:按计数规律进行级联按计数规律进行级联 CPQ2 Q1 Q0C0123456780 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 10 0 0000000010C=Q2n Q1n Q0n来一个来一个CP翻转一次翻转一次J0=K0=1当当Q0=1,CP到来即翻转到来即翻转J1=K1=Q0当当Q1Q0=1,CP到来即翻转到来即翻转J2=K2=Q1Q0=T0=T1=T2(5)n 位二进制同步加法计数器级联规律:位二进制同步加

18、法计数器级联规律:-100121 ijnjnnniniiQQQQQT(6)用用T 型触发器构成的逻辑电路图型触发器构成的逻辑电路图(将将Ti归入时钟方程归入时钟方程)CP1J1KC1FF011J1KC1FF11J1KC1FF2&CQ0Q1Q2Q0Q1Q21&1&-112100 innnnniiijjTQ QQ QQ-10 iniijjCPCP TCPQT0=1T1=Q0nT2=Q1n Q0n(7)计数器计数器计数容量计数容量、长度长度或或模模的概念的概念 即为计数器能够记忆输入脉冲的数目,也即电路即为计数器能够记忆输入脉冲的数目,也即电路的有效状态数的有效状态数。3 位二进制同步加法计数器:位

19、二进制同步加法计数器:823 M00001111/14 位二进制同步加法计数器:位二进制同步加法计数器:000111/11624 Mn 位二进制同步加法计数器:位二进制同步加法计数器:nM2 B=Q2n Q1n Q0nBorrow若用若用T 触发器:触发器:2.二进制同步减法计数器二进制同步减法计数器CPQ2Q1Q0B012345670 0 01 1 11 1 01 0 11 0 00 1 10 1 00 0 110000000012FF FF FF、012 QQQ、向高位发出的借位信号向高位发出的借位信号T0=1T1=Q0nT2=Q1n Q0n级联规律:级联规律:1-00121 ijnjnn

20、niniiQQQQQTCP1J1KC1FF011J1KC1FF11J1KC1FF1&BQ0Q1Q2Q0Q1Q23.3 位位二进制同步可逆计数器二进制同步可逆计数器(1)单时钟输入二进制同步可逆计数器单时钟输入二进制同步可逆计数器加加/减减控制端控制端 0/DU加计数加计数T0=1、T1=Q0n、T2=Q1nQ0n/012nnnQQQBC 1/DU减计数减计数T0=1、T1=Q0n、T2=Q1nQ0nnnnQQQBC012/CPQ01J1KC1FF01Q0Q21J1KC1FF2Q2Q11J1KC1FF1Q1U/D 1&1&1&1C/B(2)双时钟输入二进制同步可逆计数器双时钟输入二进制同步可逆计

21、数器加计数脉冲加计数脉冲减计数脉冲减计数脉冲CP0=CPU+CPD CP1=CPU Q0n+CPD Q0n CP2=CPU Q1n Q0n+CPD Q1n Q0nCPU 和和CPD 互斥互斥CPU=CP,CPD=0CPD=CP,CPU=0CPUQ01J1KC1FF01Q0Q21J1KC1FF21Q2Q11J1KC1FF11Q11&1&1CPD4.集成二进制同步计数器集成二进制同步计数器(1)集成集成 4 位二进制同步加法计数器位二进制同步加法计数器1 2 3 4 5 6 7 816 15 14 13 12 11 10 9VCC CO Q0 Q1 Q2 Q3 CTT LDCR CP D0 D1

22、D2 D3 CTP 地地引脚排列图引脚排列图逻辑功能示意图逻辑功能示意图Q0 Q1 Q2 Q3CTTLDCOCPCTPCR D0 D1 D2 D30 0 0 00 0 1 1 0 0 1 11)74LS161 和和 74LS16374161的状态表的状态表 输输 入入 输输 出出 注注CR LD CTP CTT CP D3 D2 D1 D0Q3n+1 Q2n+1 Q1n+1 Q0n+1CO 0 1 0 d3 d2 d1d0 1 1 1 1 1 1 0 1 1 0 0 0 0 0 0 d3 d2 d1 d0 计计 数数 保保 持持 保保 持持 0清零清零置数置数CR=1,LD=1,CP,CTP=

23、CTT=1二进制同步加法计数二进制同步加法计数CTPCTT=0CR=1,LD=1,保持保持若若 CTT=0CO=0若若 CTT=1nnnnQQQQCO0123 74163 3210nnnnTCOCT Q Q Q QCR=0Q3 Q0=0000同步同步并行置数并行置数CR=1,LD=0,CP 异步异步清零清零Q3 Q0=D3 D0 同步同步清零清零2)CC4520VDD 2CR 2Q32Q22Q12Q02EN2CP1CP1EN1Q0 1Q1 1Q1Q31CR VSS1 2 3 4 5 6 7 816 15 14 13 12 11 10 9Q0 Q1 Q2 Q3EN CP CR21EN使能端使能端

24、(也可作也可作计数脉冲输入计数脉冲输入)CP计数脉冲输入计数脉冲输入(也可作也可作使能端使能端)CR异步清零异步清零 输输 入入 输输 出出CR EN CPQ3n+1 Q2n+1 Q1n+1 Q0n+1 1 0 1 0 0 0 0 0 1 0 0 0 0加加 计计 数数加加 计计 数数 保保 持持 保保 持持 (2)集成集成 4 位二进制同步可逆计数器位二进制同步可逆计数器1)74191(单时钟)(单时钟)Q0 Q1 Q2 Q3U/DLDCO/BOCPCTD0 D1 D2 D3RC1 2 3 4 5 6 7 816 15 14 13 12 11 10 9D1 Q1 Q0 CT U/D Q2 Q

25、3 地地VCC D0 CP RC CO/BO LD D2 D3LD CT U/D CP D3 D2 D1 D0Q3n+1 Q2n+1 Q1n+1 Q0n+1 0 d3 d2 d1 d0 1 0 0 1 0 1 1 1 d3 d2 d1 d0加加 法法 计计 数数 减减 法法 计计 数数 保保 持持 1 2 3 4 5 6 7 816 15 14 13 12 11 10 9D1 Q1 Q0 CPD CPU Q2 Q3 地地VCC D0 CR BO CO LD D2 D32)74193(双时钟双时钟)COQ0 Q1 Q2 Q3LDCPUCRD0 D1 D2 D3BOCPDCR LD CPU CPD

26、 D3 D2 D1 D0Q3n+1 Q2n+1 Q1n+1 Q0n+1注注 1 0 0 d3 d2 d1 d0 0 1 1 0 1 1 0 1 1 1 0 0 0 0 d3 d2 d1 d0 加加 法法 计计 数数 减减 法法 计计 数数 保保 持持异步清零异步清零异步置数异步置数BO=CO=11.二进制异步加法计数器二进制异步加法计数器CPQ0Q1Q2CP0=CPCP1=Q0CP2=Q1用用T 触发器触发器(J=K=1)下降沿下降沿触发触发C=Q2n Q1n Q0n并行进位并行进位若采用若采用上升沿上升沿触发的触发的 T 触发器触发器CP0=CPCP1=Q0CP2=Q110001011000

27、11010111111Q01J1KC1FF0Q0Q11J1KC1FF1Q11Q21J1KC1FF2Q21CCP&【思考】若改用【思考】若改用上升沿上升沿触发的触发的 D 触发器触发器?Q0Q1FF1FF2C11DC11DQ2FF0C11DQ1Q2&Q0Q0Q1FF1FF2C11DC11DQ2FF0C11DQ1Q2&Q0D 触发器构成的触发器构成的 T 触发器触发器(D=Q),下降沿下降沿触发触发2.二进制异步减法计数器二进制异步减法计数器CPQ2Q1Q00123456780 0 01 1 11 1 01 0 11 0 00 1 10 1 00 0 10 0 0用用T 触发器触发器(J=K=1)

28、上升沿上升沿触发触发CP0=CPCP1=Q0CP2=Q1B=Q2n Q1n Q0n二进制异步计数器级间连接规律二进制异步计数器级间连接规律计数规律计数规律T 触发器的触发沿触发器的触发沿上升沿上升沿下降沿下降沿加法计数加法计数CPi=Qi-1CPi=Qi-1减法计数减法计数CPi=Qi-1CPi=Qi-11Q01J1KC1FF0Q0Q11J1KC1FF1Q11Q21J1KC1FF2Q21BCP&1 2 3 4 5 6 714 13 12 11 10 9 8CT/LD Q2 D2 D0 Q0 CP1 地地VCC CR Q3 D3 D1 Q1 CP0Q0 Q1 Q2 Q3CRCP1D0 D1 D2

29、 D3CP0CT/LD3.集成二进制异步计数器集成二进制异步计数器74197、74LS197计数计数/置数置数 CR CT/LD CP D3 D2 D1 D0Q3n+1 Q2n+1 Q1n+1 Q0n+1注注 0 1 0 d3 d2 d1 d0 1 1 0 0 0 0 d3 d2 d1 d0计计 数数异步清零异步清零异步置数异步置数M=2、8、16Q1Q1Q21J1KC1FF2Q21Q31J1KC1FF3Q3111J1KC1FF1CP1CP011J1KC1FF0Q0Q0二二-八八-十六进制计数器的实现十六进制计数器的实现M=2CPCP 0计数输出:计数输出:0QM=8CPCP 1计数输出:计数

30、输出:1 23 QQQM=16010,QCPCPCP 计数输出:计数输出:0 1 23QQQQ其它:其它:74177、74LS177、74293、74LS293 等等(8421BCD 码)码)1.十进制同步加法计数器十进制同步加法计数器0123QQQQ00000001/00010/00011/00100/00101/00110/0011110001001/0/0/0/1状态图状态图时钟方程时钟方程输出方程输出方程00000000Q3nQ2nQ1nQ0n00 01 11 10 10 0001 11 10C0123CPCPCPCPCPnnQQC03 Q1nQ0nQ3nQ2n 00 01 11 10

31、0001 11 10Q3n+1 Q2n+1 Q1n+1 Q0n+1 0 0 0 10 1 0 11 0 0 1 0 0 0 00 0 1 00 1 1 00 1 0 01 0 0 00 0 1 10 1 1 1 nnQQ010 nnnnnnQQQQQQ0101311 nnnnnnnnQQQQQQQQ021201212 nnnnnnQQQQQQ0301213 状态方程状态方程选择选择下降沿下降沿、JK 触发器触发器驱动方程驱动方程J0=K0=1,J1=Q3nQ0n,K1=Q0J2=K2=Q1nQ0nJ3=Q2nQ1nQ0n,K3=Q0n 逻辑图逻辑图检查能否自启动检查能否自启动将无效状态将无效状

32、态1010 1111代入状态方程:代入状态方程:1010 1011 01001110 1111 10001100 1011 0100该电路能自启动该电路能自启动30nnCQ QCP1KC1FF2&1JC1J1KC1FF01KC1FF3&1J1&Q1Q01KC1FF1&1J&Q2Q3Q32.十进制同步减法计数器十进制同步减法计数器(P321-323)00001001/11000/00111/00110/00101/00100/0001100100001/0/0/0/0()3.十进制同步可逆计数器十进制同步可逆计数器(P323-324)()4.集成十进制同步计数器集成十进制同步计数器()74160

33、、741621 2 3 4 5 6 7 816 15 14 13 12 11 10 9VCC CO Q0 Q1 Q2 Q3 CTT LDCR CP D0 D1 D2 D3 CTP 地地74160引脚、状态图与引脚、状态图与74161(二进制同步计数器二进制同步计数器)相同相同(1)集成十进制同步加法计数器集成十进制同步加法计数器CR LD CTP CTT CP D3 D2 D1 D0Q3n+1 Q2n+1 Q1n+1 Q0n+1CO 0 1 0 d3 d2 d1 d0 1 1 1 1 1 1 0 1 1 0 0 0 0 0 0 d3 d2 d1 d0计计 数数 保保 持持 保保 持持 0清零清

34、零置数置数74162与与74160区别:区别:74162同步清零同步清零74160异步清零异步清零(2)集成十进制同步可逆计数器集成十进制同步可逆计数器()1)74190 (单时钟单时钟)1 2 3 4 5 6 7 816 15 14 13 12 11 10 9D1 Q1 Q0 CT U/D Q2 Q3 地地VCC D0 CP RC CO/BO LD D2 D3LD CT U/D CP D3 D2 D1 D0Q3n+1 Q2n+1 Q1n+1 Q0n+1 0 d3 d2 d1 d0 1 0 0 1 0 1 1 1 d3 d2 d1 d0加加 法法 计计 数数 减减 法法 计计 数数 保保 持持

35、 74190 与与74191(单时单时钟钟二进制二进制同步可逆计数同步可逆计数器)功能类似器)功能类似2)74192(双时钟双时钟)()1 2 3 4 5 6 7 816 15 14 13 12 11 10 9D1 Q1 Q0 CPD CPU Q2 Q3 地地VCC D0 CR BO CO LD D2 D3CR LD CPU CPD D3 D2 D1 D0Q3n+1 Q2n+1 Q1n+1 Q0n+1 1 0 0 d3 d2 d1 d0 0 1 1 0 1 1 0 1 1 1 0 0 0 0 d3 d2 d1 d0 加加 法法 计计 数数 减减 法法 计计 数数 保保 持持 74192 与与7

36、4193(双时双时钟钟二进制二进制同步可逆计数同步可逆计数器)功能类似器)功能类似R0AR0B S9AS9B CP Q3n+1 Q2n+1 Q1n+1 Q0n+1注注 1 0 0 1 0 0 0 0 0 0 1 0 0 1 计计 数数 异步清零异步清零异步置异步置9M=2、5、103.集成十进制异步计数器集成十进制异步计数器 742901.2.十进制异步加法计数器和减法计数器十进制异步加法计数器和减法计数器(课后自学课后自学)S9A S9BQ0 Q1 Q2 Q3R0A R0BM1=2 M2=5CP0CP1内部结构内部结构M=2CPCP 00QM=8CPCP 11 23 QQQM=16010,Q

37、CPCPCP 0 1 23QQQQ方法方法用触发器和门电路设计用触发器和门电路设计用集成计数器构成用集成计数器构成)102(4 MM或或清零端清零端置数端置数端(同步、异步同步、异步)一、利用一、利用同步同步清零或置数端获得清零或置数端获得 N 进制计数进制计数当当 M 进制计数到进制计数到 SN 1 后使计数回到后使计数回到 S0 状态状态2.求归零逻辑表达式求归零逻辑表达式1.写出状态写出状态 SN 1 的二进制代码的二进制代码3.画连线图画连线图【例例5.2.1】用用4位二进制位二进制同步同步计数器计数器 74163 构成构成12进制进制 计数器计数器解:解:1.013QQQCR 111

38、SSN 013QQQLD 或或=10112.归零表达式:归零表达式:3.连线图连线图Q0 Q1 Q2 Q3CTTLDCOCPCTPD0 D1 D2 D3CR1&同步清零同步清零同步置零同步置零二、利用二、利用异步异步清零或置数端获得清零或置数端获得 N 进制计数进制计数 当计数到当计数到 SN 时,立即产生清零或置数信号,时,立即产生清零或置数信号,使返回使返回 S0 状态。状态。(SN瞬间即逝)瞬间即逝)1.写出状态写出状态 SN 的二进制代码的二进制代码2.求归零逻辑表达式求归零逻辑表达式3.画连线图画连线图【例例5.2.2】用二进制用二进制异步异步计数器计数器74197构成构成12进制计

39、数进制计数器器110012 S23QQCR 23QQLD 或或Q0 Q1 Q2 Q3CP0D0 D1 D2 D3CRCP1LDCT/&状态状态S12的作用:的作用:产生归零信号产生归零信号异步清零异步清零异步置零异步置零三、三、计数容量的扩展计数容量的扩展1.集成计数器的级联集成计数器的级联 Q0 Q1 Q2 Q3CTTLDCOCP CTP D0 D1 D2 D3CRQ4 Q5 Q6 Q7Q0 Q1 Q2 Q3CTTLDCOCP CTP D0 D1 D2 D3CRQ0 Q1 Q2 Q3CP11111CO016 16=256 Q0 Q1 Q2 Q3S9A S9B R0B R0ACP0CP1 Q0

40、 Q1 Q2 Q3S9A S9B R0B R0ACP0CP1Q0 Q1 Q2 Q3Q0 Q1 Q2 Q31 2 4 810 20 40 8010 10=1002.利用级联获得大容量利用级联获得大容量 N 进制计数器进制计数器1)级联级联 N1 和和 N2 进制计数器,容量扩展为进制计数器,容量扩展为 N1 N2N1进制进制计数器计数器N2进制进制计数器计数器CP进位进位CCP【例】例】Q0 Q1 Q2 Q3S9A S9B R0B R0ACP0CP1 Q0 Q1 Q2 Q3S9A S9B R0B R0ACP0CP1Q0 Q1 Q2 Q3Q0 Q1 Q2 Q3N1=10N2=62)用用归零法归零法

41、或或置数法置数法获得大容量的获得大容量的 N 进制计数器进制计数器 例例 试分别用试分别用2 片片74163 构成构成N=180计数器。计数器。用用 产生产生信号:信号:117910110011 NSS先用两片先用两片74163构成构成 256 进制计数器进制计数器,再用同步清零法再用同步清零法11&Q0 Q1 Q2 Q3CTTLDCOCPCTPD0 D1 D2 D3CRQ4 Q5 Q6 Q7Q0 Q1 Q2 Q3CTTLDCOCPCTPD0 D1 D2 D3CRQ0 Q1 Q2 Q3CP1CO01.清零清零(或置数或置数)端计数终值为端计数终值为 清零清零(或置数或置数)端计数终值为端计数终

42、值为 2.用集成用集成 计数器扩展容量后,计数器扩展容量后,终值终值 SN(或或 SN1)是是;用集成用集成计数器扩展容量后,计数器扩展容量后,终值终值 SN(或或SN1)的代码由个位、十位、的代码由个位、十位、百位的百位的对应的对应的 构成。构成。5.3 5.3.1 寄存器的主要特点和分类寄存器的主要特点和分类一、一、概念和特点概念和特点1.概念概念寄存:寄存:把二进制数据或代码暂时存储起来。把二进制数据或代码暂时存储起来。寄存器:寄存器:具有寄存功能的电路。具有寄存功能的电路。2.特点特点 主要由触发器构成主要由触发器构成,一般不对存储内容一般不对存储内容进行处理。进行处理。并行并行输入输

43、入并行并行输出输出FF0 FF1 FFn1D0 D1 Dn1 Q0 Q1 Qn1 串行串行输入输入串行串行输出输出二、二、分类分类1.按按功能功能分分基本寄存器基本寄存器移位寄存器移位寄存器(并入并出并入并出)(并入并出、并入串出、并入并出、并入串出、串入并出、串入串出串入并出、串入串出)2.按按开关元件开关元件分分TTL 寄存器寄存器CMOS 寄存器寄存器基本寄存器基本寄存器移位寄存器移位寄存器多位多位 D 型触发器型触发器锁存器锁存器寄存器阵列寄存器阵列单向移位寄存器单向移位寄存器双向移位寄存器双向移位寄存器基本寄存器基本寄存器移位寄存器移位寄存器(多位多位 D 型触发器型触发器)(同同

44、TTL)5.3.2 基本寄存器基本寄存器 一个触发器可以存储一个触发器可以存储 位二进制信号;寄存位二进制信号;寄存 n 位位二进制数码,需要二进制数码,需要 个触发器。个触发器。1 n一、一、4 边沿边沿 D 触发器触发器(74175、74LS175)C11DD0Q0Q0RDC11DD1Q1Q1C11DD2Q2Q2C11DD3Q3Q3RDRDRDFF0FF1FF2FF311CR异步清零异步清零00000同步送数同步送数1d0d1d2d3 特点:特点:并入并出,结构简单,抗干扰能力强。并入并出,结构简单,抗干扰能力强。二二、双、双 4 位锁存器位锁存器(74116)(一一)引脚排列图和逻辑功能

45、示意图引脚排列图和逻辑功能示意图Q0 Q1 Q2 Q3CRLEAD0 D1 D2 D3LEB21异步清零异步清零送数送数控制控制数码并行输入数码并行输入数码并行输出数码并行输出(二二)逻辑功能逻辑功能清零清零0 CR送数送数00000123 QQQQ1 CR0BA LELE01230123ddddQQQQ 保持保持1 CR1BA LELE不变不变0123QQQQ三、三、4 4 寄存器阵列寄存器阵列(74170、74LS170)(一一)引脚排列图和逻辑功能示意图引脚排列图和逻辑功能示意图Q0 Q1 Q2 Q3ENRD0 D1 D2 D3ENWAW0AW1AR0AR1并行数码输入并行数码输入数数

46、码码 输输 出出AW0、AW1 写入地址码写入地址码AR0、AR1 读出地址码读出地址码ENW 写入时钟脉冲写入时钟脉冲ENR 读出时钟脉冲读出时钟脉冲1 2 3 4 5 6 7 816 15 14 13 12 11 10 974170VCC D0 AW0 AW1 ENWENR Q0 Q1D1 D2 D3 AR1 AR0 Q3 Q2 地地(二二)逻辑功能逻辑功能16个个D锁存器锁存器 构成存储矩阵构成存储矩阵能存放能存放4个字个字:W0、W1、W2、W3Q0 Q1 Q2 Q3ENRD0 D1 D2 D3ENWAW0AW1AR0AR1FF00FF10FF20FF30FF01FF11FF21FF3

47、1FF02FF12FF22FF32FF03FF13FF23FF330 0 0 10 0 0 1010 0 1 00 0 1 0100 1 0 00 1 0 0111 0 0 01 0 0 000 0 0 0 101 0 0 1 010 0 1 0 011 1 0 0 0特点特点:能同时进行读写能同时进行读写;集电极开路输出集电极开路输出每个字有每个字有4位:位:3330232013100300QQQQQQQQ、5.3.3 移位寄存器移位寄存器一、单向移位寄存器一、单向移位寄存器右移寄存器右移寄存器Q0Q1Q2Q3C11DFF0C11DFF1C11DFF2C11DFF3时钟方程时钟方程CPCPC

48、PCPCP 3210驱动方程驱动方程nnniQDQDQDDD2312010 、状态方程状态方程nnnnnninQQQQQQDQ21311201110,Di000000001011100000000111100000001011000001101100000101000001000000100000右移右移输入输入右移右移输出输出左移寄存器左移寄存器Di左移左移输入输入左移左移输出输出驱动方程驱动方程innnDDQDQDQD 3322110、状态方程状态方程innnnnnnDQQQQQQQ 13312211110,主要特点:主要特点:1.输入数码在输入数码在 CP 控制下,依次右移或左移控制下,

49、依次右移或左移 2.寄存寄存 n 位二进制数码。位二进制数码。n 个个CP完成完成串行输入串行输入,并可,并可从从Q0 Q3 端获得端获得并行并行输出,再经输出,再经 n 个个CP又获得又获得串行输出串行输出3.若串行数据输入端为若串行数据输入端为 0,则,则 n 个个CP后寄存器被清零后寄存器被清零Q3Q0Q1Q2C11DFF0C11DFF1C11DFF2C11DFF3二、双向移位寄存器二、双向移位寄存器(自学自学)三、集成移位寄存器三、集成移位寄存器1.8 位单向移位寄存器位单向移位寄存器 74164DSA DSB Q0 Q1 Q2 Q3 地地1 2 3 4 5 6 714 13 12 1

50、1 10 9 8VCC Q7 Q6 Q5 Q4 CR CPQ7Q6Q5Q4Q3Q2Q1Q0CP CRDSA DSB异步异步清零清零0 0 0 0 0 0 0 0保持保持不变不变2.4 位双向移位寄存器位双向移位寄存器 74LS194(略略)710SBSAQQQDDDS 送数送数真值表见表真值表见表5.3.7(P354)5.3.4 移位寄存器型计数器移位寄存器型计数器结结构构示示意意图图Q0Q1Qn1C11DFF0C11DFF1C11DFFn1反馈逻辑电路反馈逻辑电路Dn1D0D1),(nnnnQQQFD1100 特点:特点:电路结构简单,计数顺序一般为非自然态序,电路结构简单,计数顺序一般为非

51、自然态序,用途极为广泛。用途极为广泛。一、环形计数器一、环形计数器1.电路组成电路组成Q0Q1Q2Q3C11DFF0C11DFF1C11DFF2C11DFF32.工作原理工作原理03nDQ1000010000100001有效循环有效循环000011110101101011000110001110011101111001111011无无效效循循环环故不能自启动故不能自启动故也称自循环的移位寄存器故也称自循环的移位寄存器3.能自启动的环型计数器能自启动的环型计数器Q0Q1Q2Q3C11DFF0C11DFF1C11DFF2C11DFF3&Q0Q1Q2Q32100QQQD 01QD 12QD 23QD

52、 10 nQ11 nQ12 nQ13 nQ1110011100111111110111000110100000010100001000001001101001011011二、扭环形计数器二、扭环形计数器Q0Q1Q2Q3C11DFF0C11DFF1C11DFF2C11DFF303nDQ有效循环有效循环无效循环无效循环克服自启动电路:克服自启动电路:P360 图图5.3.16三、最大长度移位寄存器型计数器三、最大长度移位寄存器型计数器(略略)不能自启动不能自启动5.3.5 读读/写存储器写存储器 RAM(Random Access Memory)【半导体存储器的概念】【半导体存储器的概念】存放存放

53、1位位二进制信息二进制信息(即即位位)。触发器触发器 存放存放1组组二进制信息二进制信息(即即字字)。寄存器寄存器 存储信息比寄存器存储信息比寄存器大得多大得多。存储器存储器【存储器的分类】【存储器的分类】u 按制造工艺分按制造工艺分双极型:速度快、功耗大、价格高双极型:速度快、功耗大、价格高MOS型:集成度高、功耗低、价格低型:集成度高、功耗低、价格低u 按存储功能分按存储功能分顺序存取存储器顺序存取存储器 SAM(Sequential)随机存取存储器随机存取存储器 RAM只读存储器只读存储器 ROM补充补充5.3.5 读读/写存储器写存储器 RAM存储单元存储单元 存放一位二进制数的基本单

54、元存放一位二进制数的基本单元(即即位位)。存储容量存储容量 存储器含存储单元的总个存储器含存储单元的总个(位位)数。数。存储容量存储容量=字数(字数(word)位数(位数(bit)地址地址 存储器中每一个字的编号存储器中每一个字的编号256 1,256 4 一共有一共有 256 个字,需要个字,需要 256 个地址个地址1024 4,1024 8 一共有一共有 1024 个字,需要个字,需要 1024 个地址个地址地址译码地址译码 用译码器赋予每一个字一个地址用译码器赋予每一个字一个地址N 个地址输入,能产生个地址输入,能产生 2N 个地址个地址一元地址译码一元地址译码(单向译码、基本译码、字

55、译码单向译码、基本译码、字译码)二元地址译码二元地址译码(双向译码双向译码)行译码、列译码行译码、列译码字数一般以字数一般以 1024即即(K)为单位为单位一、一、RAM 的结构的结构存储矩阵存储矩阵读读/写写控制器控制器地地址址译译码码器器地地址址码码输输入入片选片选读读/写写控制控制输入输入/输出输出CS R /W I /O 【补充】【补充】对对 256 4 存储矩阵进行地址译码存储矩阵进行地址译码一元地址译码一元地址译码D3D2D1D0W0W1W255译译码码器器0 0 1 11 0 1 00 1 1 1A0A1A710.0W11 0 1 0缺点缺点:8 位地址输入的译码位地址输入的译码

56、器器,需要需要 28 条条(256)输出线。输出线。1 0 1 0二元地址译码二元地址译码Y0Y1 Y15A0A1A2A3X0X1X15行行译译码码器器A4 A5 A6 A7列译码器列译码器Dout 8 位地址输入的地址位地址输入的地址译码器译码器,只有只有 32条输出线。条输出线。25(32)根行选择线根行选择线10 根地址线根地址线 2n(1024)个地址个地址25(32)根列选择线根列选择线1024 个字排列成个字排列成 32 32 矩阵矩阵当当 X0 =1,Y0 =1 时,时,对对 0-0 单元单元读读(写写)当当X31 =1,Y31=1时,时,对对 31-31 单元单元读读(写写)例

57、例 1024 1 存储器矩阵存储器矩阵二、二、RAM的存储单元的存储单元1.静态存储单元静态存储单元基本工作原理:基本工作原理:DDSRQQ位位线线B位位线线B 门控管门控管,受控于受控于Xi控制触发器与位线的连通控制触发器与位线的连通截止截止截止截止 导通导通导通导通截止截止截止截止 01导通导通导通导通读操作时读操作时:QD QD 写操作时写操作时:QDQD 门控管门控管,受控于受控于Yi控制位线与数据线的连通控制位线与数据线的连通1MOS管为管为简化画法简化画法六管六管 CMOS 存储单元存储单元VDDDDNP特点:特点:PMOS 作作 NMOS负载,功耗极小,可负载,功耗极小,可在交流

58、电源断电后,在交流电源断电后,靠电池保持存储数据。靠电池保持存储数据。2.动态动态MOS存储单元存储单元单管单管MOS存储单元存储单元T1CB位位线线字线字线C1X写操作写操作:字线为高电平字线为高电平 T1 导通导通若位线为高电平若位线为高电平(1),则,则C1充电充电若位线为低电平若位线为低电平(0),则,则C1放电放电字线为高电平字线为高电平 T1 导通导通若若U1=“1”,则则C1向向CB放电使放电使UB=“1”若若U1=“0”,则则UB=“0”门控管门控管因读时,因读时,C1上电荷要损失,故每次读出后需进行上电荷要损失,故每次读出后需进行“刷刷新新”CBC1,读操作后,读操作后,很小

59、很小 需要高灵敏度读出器。需要高灵敏度读出器。111BBCUUCC三、三、RAM 容量的扩展容量的扩展I/O(0)A0A1 A9R/WCSI/O(1)A0A1A9 R/WCSI/O(7)A0A1A9 R/WCSA0A1.A9CSR/WI0I1I7D0 D7O0O1O7D0 D7N=目标存储器容量目标存储器容量已有存储器容量已有存储器容量需要片数需要片数N=8【例】【例】用用10241位位RAM构成构成10248位位RAM【方法】所有输入信号都并联(地址信号、片选信号【方法】所有输入信号都并联(地址信号、片选信号和读写信号)。输出并列。和读写信号)。输出并列。1.位扩展位扩展 2.字扩展字扩展N

60、=目标存储器容量目标存储器容量已有存储器容量已有存储器容量需要片数需要片数N=4【例】【例】用用2568位位RAM组成组成10248位存储器。位存储器。【方法】片内地址信号并联;多余地址端通过译【方法】片内地址信号并联;多余地址端通过译码器接至各片的片选端;码器接至各片的片选端;I/O同名端并联。同名端并联。四、四、RAM 芯片举例芯片举例123456789101112242322212019181716151413A7A6A5A4A3A2A1 A0D0D1D2GNDVDDA8A9WEOEA10CS D7D6D5D4D3片片 选选输出使能输出使能写入控制写入控制输入输入工作方式工作方式I/OC

61、S OE WE A0 A10D0 D71 0 0 1 稳定稳定0 0 稳定稳定低功耗维持低功耗维持读读写写高阻态高阻态输出输出输入输入容量:容量:2K 8位位地址线:地址线:11根根顺序脉冲顺序脉冲分类分类计数型计数型移位型移位型1.由四进制计数器由四进制计数器(JK 触发器触发器)和译码器构成和译码器构成Y0CP1J1KC10Q0QFF01J1KC11Q1QFF1&11RDRD1CR&Y1Y2Y3nnQQ01nnQQ01nnQQ01nnQQ01nnQQ010 nnnnnnnQQQQQQQ10101011 CPQ0Q1Y0Y1Y2Y32.由由 D 触发器和译码器构成触发器和译码器构成C11DQ

62、0Q0RDC11DQ1Q1FF0FF1=1CRRD111Y0&Y1Y2Y3nnQDQ0010 nnnQQDQ10111 结果与前相同结果与前相同防防止止竞竞争争冒冒险险nnnnQQQQ21010 nnQQ011 nnQQ112 nnQQ213 C11DQ0C11DQ1C11DQ2C11DQ3FF0FF1FF2FF3CRRRRR1状态图同环型计数器,能自启动,状态图同环型计数器,能自启动,只有只有 4 个有效状态,不需译码器。个有效状态,不需译码器。(一一)由环型计数器构成由环型计数器构成CPQ0Q1Q2Q3(二二)由扭环型计数器构成由扭环型计数器构成(略)(略)D0D1D2D3LDCRCTTC

63、TPQ0Q1Q2Q3CO74LS16374LS138STASTBSTCY0Y1Y2Y3Y4Y5Y6Y71D2D3D4D5D6D7D8DCP174LS374EN1Q2Q3Q4Q5Q6Q7Q8QCBA二进制二进制计数器计数器3-8线线译码器译码器缓冲缓冲寄存器寄存器CPQ0Q1Q2Y0Y1Y2Y3Y4Y5Y6Y7计数器、译码器的时序图计数器、译码器的时序图(Programmable Logic Device)一、一、PLD的基本结构和分类的基本结构和分类1.基本结构基本结构输输入入电电路路与与门门阵阵列列或或门门阵阵列列输输出出电电路路输输入入或项或项输入项输入项积项积项输输出出1AAAAAAPL

64、D的输入缓冲电路的输入缓冲电路2.分类分类(1)按可编程情况分按可编程情况分分分 类类与阵列与阵列或阵列或阵列输出电路输出电路出现年代出现年代PROM固定固定可编程可编程固定固定70年代初年代初PLA可编程可编程可编程可编程固定固定70年代中年代中PAL可编程可编程固定固定固定固定70年代末年代末GAL可编程可编程固定固定可组态可组态80年代初年代初 PROM 可编程只读存储器可编程只读存储器I2 I1 I0O2 O1 O 0与与阵列阵列(固定固定)或或阵列阵列(可编程可编程)缺点:缺点:只能实现标准只能实现标准 与或式与或式 芯片面积大芯片面积大 利用率低利用率低,不经济不经济用途:用途:存

65、储器存储器 函数表函数表 显示译码电路显示译码电路(Programmable Read Only Memory)PLA 可编程逻辑阵列可编程逻辑阵列I2 I1 I0O2 O1 O 0与与阵列阵列(可编程可编程)或或阵列阵列(可编程可编程)优点:优点:与阵列、或阵列与阵列、或阵列 都可编程都可编程 能实现最简与或式能实现最简与或式 缺点:缺点:价格较高价格较高 门的利用率不高门的利用率不高(Programmable Logic Array)PAL 可编程阵列逻辑可编程阵列逻辑I2 I1 I0O2 O1 O 0与与阵列阵列(可编程可编程)或或阵列阵列(固定固定)优点:优点:速度高速度高 价格低价格

66、低 采用编程器现场采用编程器现场 编程编程 缺点:缺点:输出方式固定输出方式固定 一次编程一次编程(Programmable Array Logic)GAL 通用阵列逻辑通用阵列逻辑I2 I1 I0O2 O1 O 0与与阵列阵列(可编程可编程)或或阵列阵列(固定固定)优点:优点:具有具有 PAL 的功能的功能 采用逻辑宏单元采用逻辑宏单元 使输出自行组态使输出自行组态 功能更强,使用功能更强,使用 灵活,应用广泛灵活,应用广泛 (Generic Array Logic)(2)按可编程和改写方法分按可编程和改写方法分PLD编程方式编程方式改写方法改写方法特点、用途特点、用途第一代第一代一次性掩模一次性掩模(厂家)(厂家)不能改写不能改写固定程序、数据、函固定程序、数据、函数表、字符发生器数表、字符发生器第二代第二代编程器编程器(用户用户)紫外光擦除紫外光擦除 先擦除,后编程先擦除,后编程第三代第三代编程器编程器(用户用户)电擦除电擦除擦除、编程同时进行擦除、编程同时进行第四代第四代在系统可编程在系统可编程软件软件直接在目标系统或线直接在目标系统或线路板上编程路板上编程(3)按组合、时序分

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。