数字系统设计试卷:2011年_数字系统设计试题20A卷

数字系统设计试卷:2011年_数字系统设计试题20A卷

《数字系统设计试卷:2011年_数字系统设计试题20A卷》由会员分享,可在线阅读,更多相关《数字系统设计试卷:2011年_数字系统设计试题20A卷(4页珍藏版)》请在装配图网上搜索。

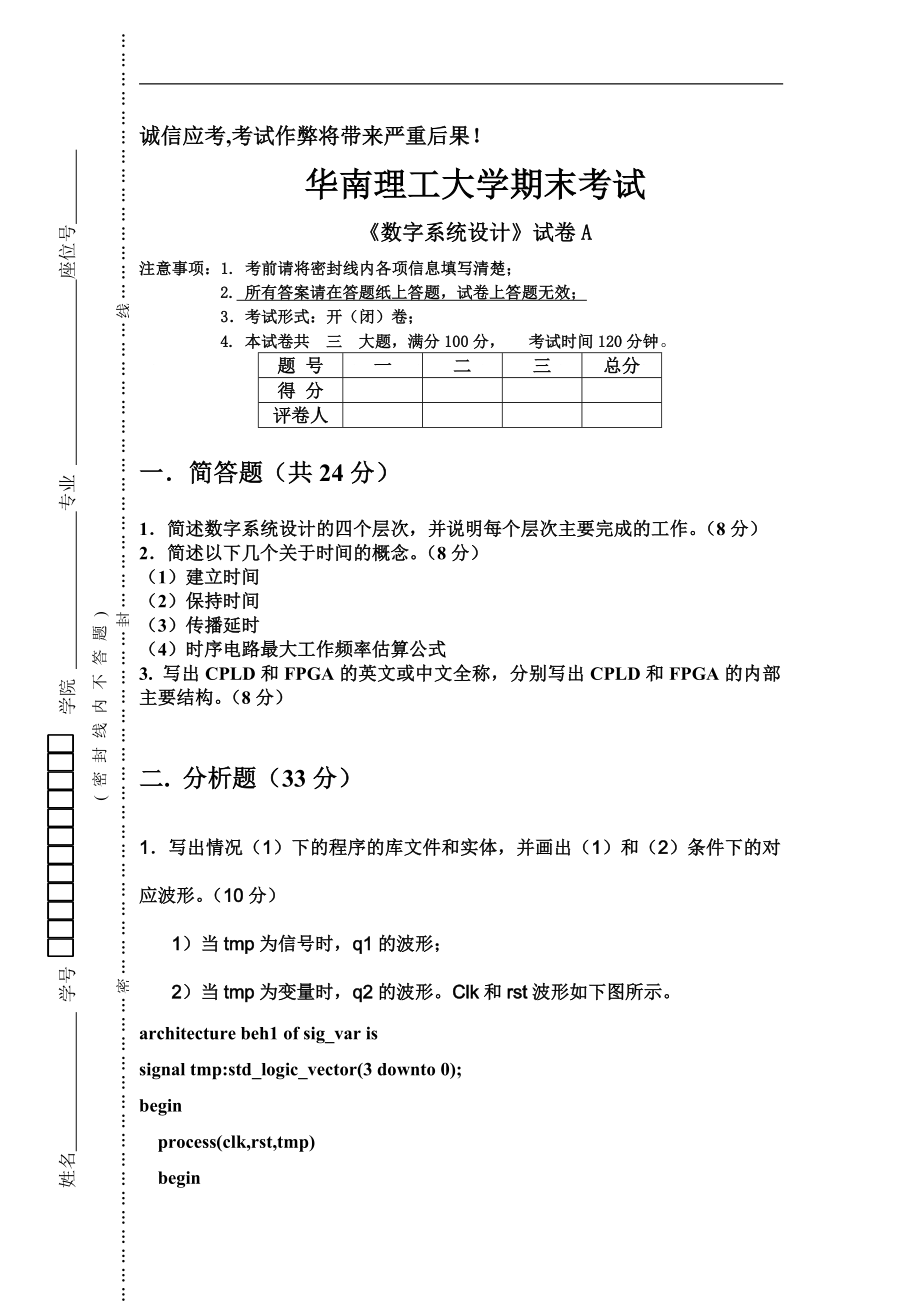

1、姓名 学号 学院 专业 座位号 ( 密 封 线 内 不 答 题 )密封线线_ _ 诚信应考,考试作弊将带来严重后果! 华南理工大学期末考试数字系统设计试卷A注意事项:1. 考前请将密封线内各项信息填写清楚; 2. 所有答案请在答题纸上答题,试卷上答题无效; 3考试形式:开(闭)卷; 4. 本试卷共 三 大题,满分100分,考试时间120分钟。题 号一二三总分得 分评卷人一简答题(共24分)1简述数字系统设计的四个层次,并说明每个层次主要完成的工作。(8分)2简述以下几个关于时间的概念。(8分)(1)建立时间(2)保持时间(3)传播延时(4)时序电路最大工作频率估算公式3. 写出CPLD和FPG

2、A的英文或中文全称,分别写出CPLD和FPGA的内部主要结构。(8分)二. 分析题(33分)1写出情况(1)下的程序的库文件和实体,并画出(1)和(2)条件下的对应波形。(10分)1)当tmp为信号时,q1的波形;2)当tmp为变量时,q2的波形。Clk和rst波形如下图所示。architecture beh1 of sig_var issignal tmp:std_logic_vector(3 downto 0);begin process(clk,rst,tmp) begin if rst=1 then tmp=0000; elsif clkevent and clk=1 then tmp

3、=tmp+1; q1=tmp; end if; end process;end beh1;architecture beh2 of sig_var isbegin process(clk,rst) variable tmp:std_logic_vector(3 downto 0);begin if rst=1 then tmp:=0000; elsif clkevent and clk=1 then tmp:=tmp+1; q2=tmp; end if; end process;end beh2;2有一个传输门,其惯性延时时间为4ns。根据下述赋值语句和给定的波形,画出对应Z1,Z2和Z3的波

4、形图。(6分)(1)Z1=Vi (2)Z2 =Vi after 4 ns (3)Z3 = TRANSPORT Vi AFTER 3 ns3根据给定的A的波形,分别画出(a)、(b)和(c)程序的S1、S2和S3对应的波形,其中S1S3为integer.(9分) IF A = 4 THEN IF A = 4 THEN IF A = 4 THEN S1=1; S2=1; S3=1; END IF; ELSIF A = 5 THEN ELSE IF A = 5 THEN S2=2; S3=2; S1=2; END IF; END IF; END IF; (a) (b) (c)4按要求转换下列程序。(

5、8分)(1)将下列程序替换为wait语句。(3分)process (clk) begin if clk = 1 and clkevent then q = data; end if;end process;(2)将下列程序替换为if语句,请不要改变条件的顺序性。(5分)y = 11 when a(3)=1 else 10 when a(2)=1 else 01 when a(1)=1 else 00 when a(0)=1 else 00;三、电路设计题 (43分)1简述仿真测试平台的基本架构(4分);试用VHDL语言编写测试平台文件(Testbench),要求testbench产生的时钟周期

6、为100ns,占空比50%;复位信号0电平有效,且起始时刻为0,100ns后变为1。(12分)。被测文件的实体如下所示:ENTITY sin_gen IS PORT(rst : IN STD_LOGIC;clk : IN STD_LOGIC;q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);END sin_gen;2系统有三台设备,分别称为设备1、设备2和设备3。试用有限状态机(FSM)实现此3个设备请求共享资源的。请求信号r1、r2、r3分别代表上述3个设备的请求,认可信号g1、g2和g3代表设备1、设备2和设备3得到共享资源。设备被分配给不同的优先级,设备1的优先级最高,设备2的优先级其次,设备3的优先级最低。因此,若多个设备同时发出请求信号,则FSM将把认可信号发给提出请求设备中优先级最高的设备。(1)试画出上述仲裁器的ASM图;(6分)(2)上述状态机中,若设备1和设备2不断提出请求,则设备3永远得不到服务的机会,即使在空闲状态,不是设备1就是设备2总是提出请求。为了确保设备3能得到服务,在设备3提出请求的情况下,设备1和2只能得到一次服务,然后设备3的服务请求便能得到认可。设画出此时的ASM图。(12分)(3)试对(1)的ASM图进行VHDL建模。(9分)

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。