LED灯移位显示-ise开发环境Verilog编程流水灯

LED灯移位显示-ise开发环境Verilog编程流水灯

《LED灯移位显示-ise开发环境Verilog编程流水灯》由会员分享,可在线阅读,更多相关《LED灯移位显示-ise开发环境Verilog编程流水灯(4页珍藏版)》请在装配图网上搜索。

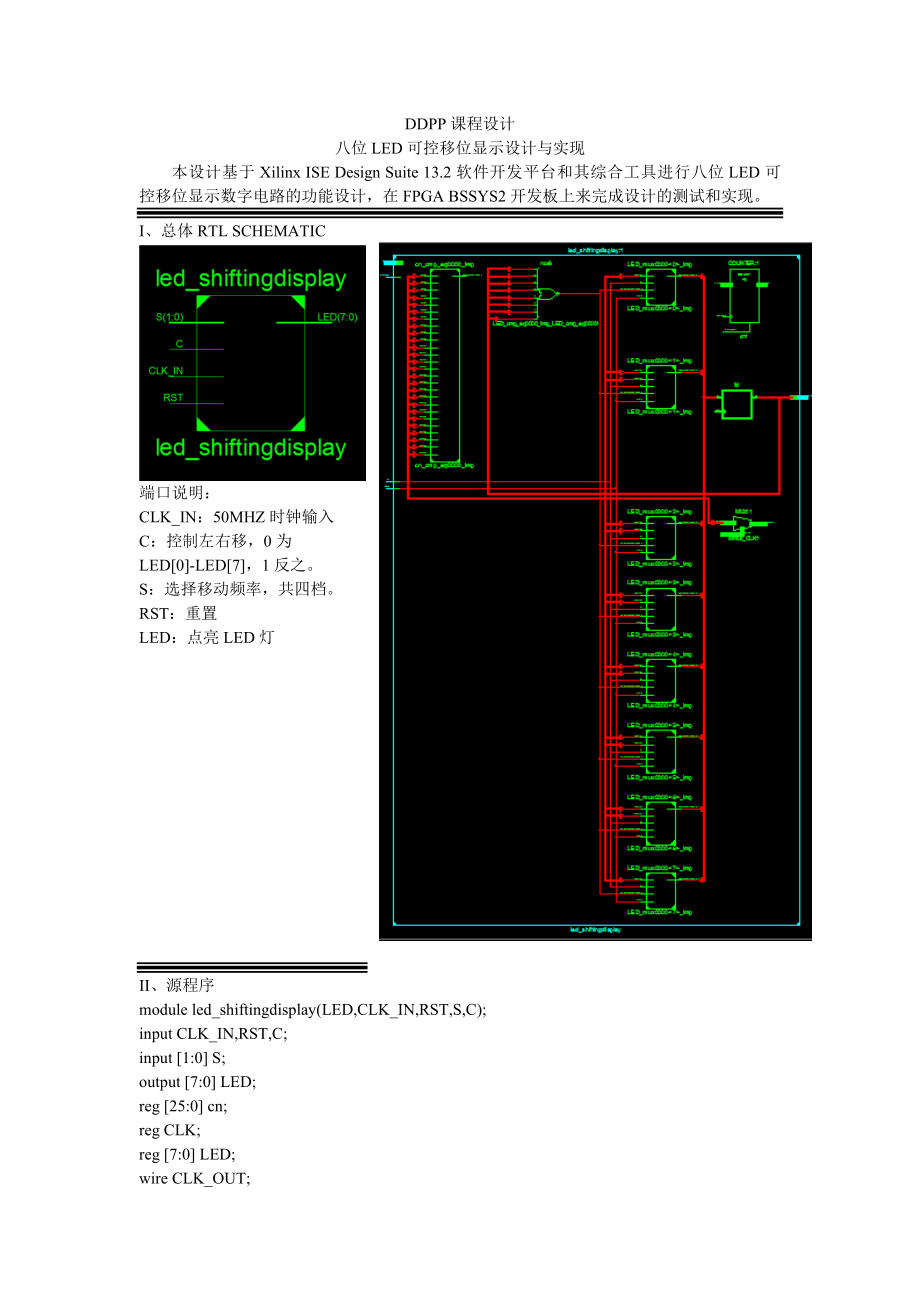

1、DDPP课程设计八位LED可控移位显示设计与实现本设计基于Xilinx ISE Design Suite 13.2软件开发平台和其综合工具进行八位LED可控移位显示数字电路的功能设计,在FPGA BSSYS2开发板上来完成设计的测试和实现。I、总体RTL SCHEMATIC端口说明:CLK_IN:50MHZ时钟输入C:控制左右移,0为LED0-LED7,1反之。S:选择移动频率,共四档。RST:重置LED:点亮LED灯II、源程序module led_shiftingdisplay(LED,CLK_IN,RST,S,C);input CLK_IN,RST,C;input 1:0 S;outpu

2、t 7:0 LED;reg 25:0 cn;reg CLK;reg 7:0 LED;wire CLK_OUT;wire CLK2_OUT;wire CLK3_OUT;wire CLK4_OUT;initial begin cn=0;endalways (posedge CLK_IN)beginif(cn=49999999)begin cn=0; endelse cn=cn+26d1;endassign CLK_OUT=cn25;/1HZassign CLK2_OUT=cn24;/2HZassign CLK3_OUT=cn21;/16HZassign CLK4_OUT=cn20;/32HZalw

3、ays (S,CLK_OUT,CLK2_OUT,CLK3_OUT,CLK4_OUT)begincase(S)2d0:CLK=CLK_OUT;2d1:CLK=CLK2_OUT;2d2:CLK=CLK3_OUT;2d3:CLK=CLK4_OUT;endcaseendinitial begin LED=8b00000000;endalways (posedge CLK)beginif(C)/C=1,left shiftingif(RST) LED=8b00000001;else if(LED=8b00000000)LED=8b00000001;else LED=LED1;else/C=1,right

4、 shiftingif(RST) LED=8b10000000;else if(LED=8b00000000)LED=8b10000000;else LED1;endendmoduleIII、用户约束文件led_shiftingdisplay.vNET C LOC = N3;NET CLK_IN LOC = B8;NET LED0 LOC = M5;NET LED1 LOC = M11;NET LED2 LOC = P7;NET LED3 LOC = P6;NET LED4 LOC = N5;NET LED5 LOC = N4;NET LED6 LOC = P4;NET LED7 LOC =

5、G1;NET RST LOC = A7;NET S0 LOC = P11;NET S1 LOC = L3;# PlanAhead Generated IO constraints NET C IOSTANDARD = LVCMOS33;NET CLK_IN IOSTANDARD = LVCMOS33;NET LED0 IOSTANDARD = LVCMOS33;NET LED1 IOSTANDARD = LVCMOS33;NET LED2 IOSTANDARD = LVCMOS33;NET LED3 IOSTANDARD = LVCMOS33;NET LED4 IOSTANDARD = LVC

6、MOS33;NET LED5 IOSTANDARD = LVCMOS33;NET LED6 IOSTANDARD = LVCMOS33;NET LED7 IOSTANDARD = LVCMOS33;NET RST IOSTANDARD = LVCMOS33;NET S0 IOSTANDARD = LVCMOS33;NET S1 IOSTANDARD = LVCMOS33;IV、程序仿真测试文件led_shiftingdisplay.vmodule test_ledshiftingdisplay;reg CLK_IN;reg RST;reg 1:0 S;reg C; wire 7:0 LED;led_shiftingdisplay uut (.LED(LED), .CLK_IN(CLK_IN), .RST(RST), .S(S), .C(C);parameter PERIOD = 20; initialbegin CLK_IN = 1b0; #10; forever #(PERIOD/2) CLK_IN = CLK_IN; endinitial beginRST = 0;S = 3;C = 1;endendmodule仿真波形:各个信号仿真波形正常,唯有LED7:0均为高阻态(除最低位外),仿真不成功,不得其解。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。