上海大学verilog设计32位浮点加法器设计

上海大学verilog设计32位浮点加法器设计

《上海大学verilog设计32位浮点加法器设计》由会员分享,可在线阅读,更多相关《上海大学verilog设计32位浮点加法器设计(9页珍藏版)》请在装配图网上搜索。

1、32位浮点加法器设计摘要:浮点数具有数值范围大,表示格式不受限制的特点,因此浮点数的应用是非常广泛的。浮点数加法 运算比较复杂,算法很多,但是为了提高运算速度,大部分均是基于流水线的设计结构。本文介绍了基于 IEE754标准的用Verilog语言设计的32位浮点加法器,能够实现32位浮点数的加法运算。虽然未采用流 水线的设计结构但是仍然对流水线结构做了比较详细的介绍。关键字:浮点数,流水线,32位浮点数加法运算,Verilog语言设计32-bit floating point adder designCao Chi,Shen Jia- qi,Zheng Yun-jia(Schoolof Mec

2、hatronic Engineering and Automation,Shanghai Universi ty,Shanghai ,China)Abstract:/沈佳琪搞定Key words: float; Assembly line; 32-bit floating-point adder浮点数的应用非常广泛,无论是在计算机还是微处理器中都离不开浮点数。但是浮点数的加 法运算规则比较复杂不易理解掌握,而且按照传统的运算方法,运算速度较慢。因此,浮点 加法器的设计采用了流水线的设计方法。32位浮点数运算的摄入处理采用了 IEE754标准的 “0舍1入”法。1.浮点数的介绍在处理器中,数据不

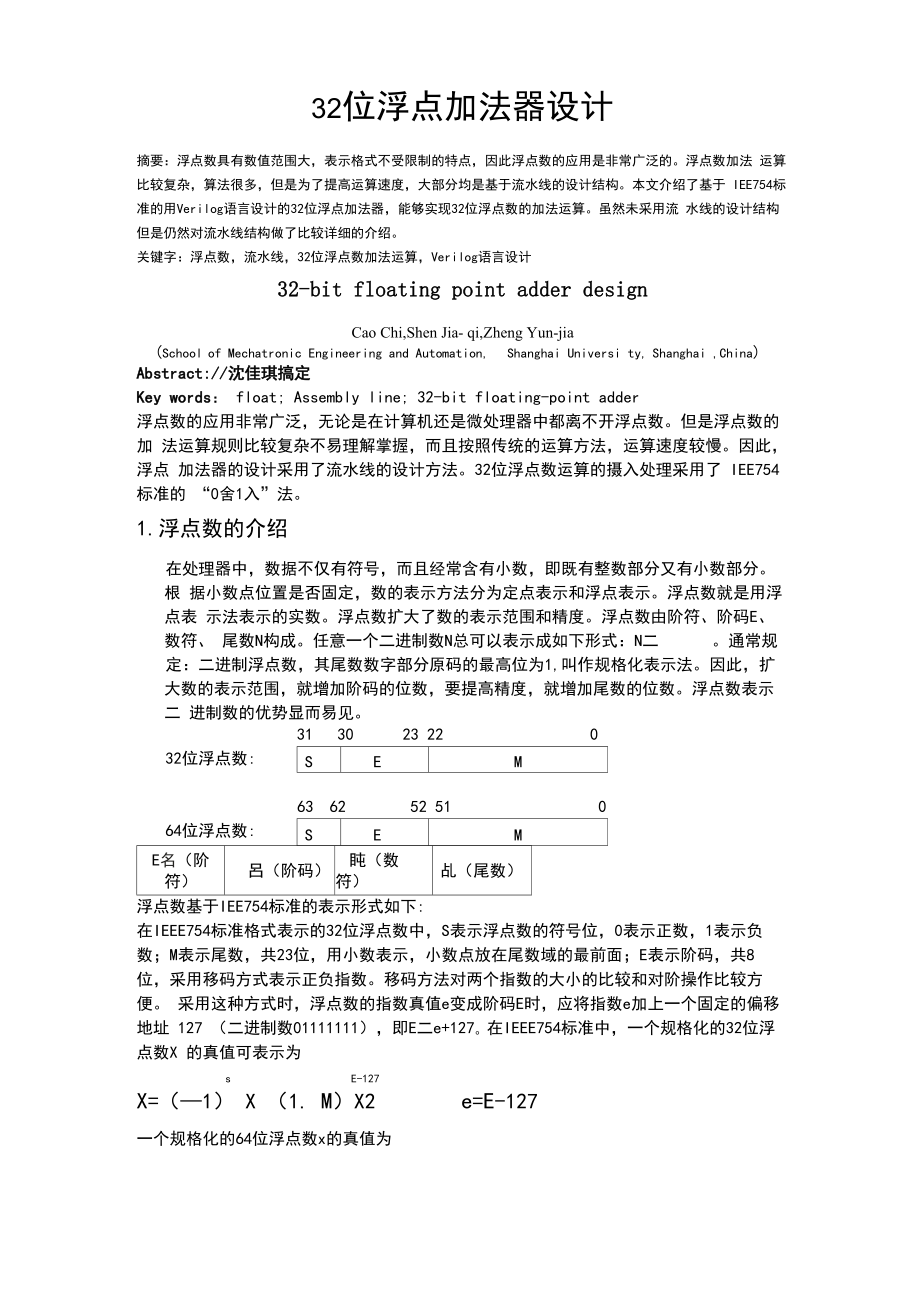

3、仅有符号,而且经常含有小数,即既有整数部分又有小数部分。根 据小数点位置是否固定,数的表示方法分为定点表示和浮点表示。浮点数就是用浮点表 示法表示的实数。浮点数扩大了数的表示范围和精度。浮点数由阶符、阶码E、数符、 尾数N构成。任意一个二进制数N总可以表示成如下形式:N二。通常规定:二进制浮点数,其尾数数字部分原码的最高位为1,叫作规格化表示法。因此,扩 大数的表示范围,就增加阶码的位数,要提高精度,就增加尾数的位数。浮点数表示二 进制数的优势显而易见。32位浮点数:SEM313023 22064位浮点数:SEM636252 510E名(阶符)呂(阶码)盹(数符)乩(尾数)浮点数基于IEE75

4、4标准的表示形式如下:在IEEE754标准格式表示的32位浮点数中,S表示浮点数的符号位,0表示正数,1表示负 数;M表示尾数,共23位,用小数表示,小数点放在尾数域的最前面;E表示阶码,共8 位,采用移码方式表示正负指数。移码方法对两个指数的大小的比较和对阶操作比较方便。 采用这种方式时,浮点数的指数真值e变成阶码E时,应将指数e加上一个固定的偏移地址 127 (二进制数01111111),即E二e+127。在IEEE754标准中,一个规格化的32位浮点数X 的真值可表示为sE-127X=(1) X (1. M)X2e=E-127一个规格化的64位浮点数x的真值为sE-1023e=E1023

5、X= (-1) X (1. M)X2为提高数据的精度,当尾数的值不为0时,尾域的最高有效位为1,否则修改阶码同时 左右移动小数点,使其变成规格化表示的浮点数。这一过程称之为规格化表示。当浮点 数的尾数为零时,不论阶码为何值或者阶码的值遇到比它所能表示的最小值还小时,不 管其尾数为何值,计算机都把该浮点数当做零值。原码非0值浮点数的尾数值最高位必 定为1,在保存浮点数时,通过尾数左移(小数点向右移动)把该位去掉,用同样多的 位数能多存一位二进制数,有利于提高数据表示精度,这种处理方案称之为隐藏位技术。 32位浮点数的表示范围有限,超过该范围的浮点数会产生溢出。溢出分为正上溢和负上 、亠 溢。00

6、正匕溢负数正数+oo2.32位浮点数加法运算0操作数的检查;比较阶码大小并完成对阶; 尾数进行加法运算; 结果进行规格化处理; 舍入处理;溢出处理。浮点数的加法运算与二进制数直接进行加法运算区别是很大的。浮点数的加法运算分为 以下几个步骤:(2)(3)(4)(5)0操作数的检查是判断两个数据是否为零,若有一个数据为0则直接输出结果;比较两 个数据的阶码大小,并通过尾数的移动来改变阶码使其相等。对阶的过程要遵循阶码小 的向阶码大的数对齐,小阶的尾数右移,每右移一位,阶码加一。尾数求和运算与一般 二进制数的加法运算相同;在尾数相加后得到的数可能不是规格化的数,为了提供运算 的精度,就必须对求和的结

7、果进行规格化处理。当运算结果溢出时,进行右归。左归时 阶码做减法,右归时阶码做加法。在IEEE754标准中,舍入处理提供了四种方法:(2)(6)就近舍入:实质上就是通常所说的“四舍五入”朝0舍入:朝数轴原点方向舍入,就是简单的截尾。无论尾数是正数还是负数, 截尾都使取值的绝对值比原值的绝对值小。(3)(4)朝+8舍入:对正数来说,只要多余位不全为0则向最低有效位进1;对负数来 说则是简单的截尾。朝一8舍入:处理方法与朝+8舍入情况相反。对正数来说只要多余位不全为0 则简单截尾;对负数来说,向最低有效位进1。与一般二进制数的加法运算相似,浮点数的加法运算也要是否溢出。尾数之和 出现01.XXXX

8、或10.XXXX时,并不表示溢出,只有将此数进行右归后,再根据 阶码来判断浮点运算结果是否溢出。一般说浮点是否溢出均是指上溢(正上溢、 下上溢)。因此,浮点数是否溢出可由阶码来决定。从以上加法的运算过程可以看出,浮点数加法运算步骤较多,体系结构相对比 较复杂,目前比较常见的浮点加法器的结构有标准算法结构、L0P算法结构、双 通道算法结构。一般的标准算法结构首先比较阶数,得到阶差,根据阶差进行尾数的移位,然后送入定点加法器进行尾数相加,规格化单元对结果进行规格 化,在规格化单元里有一个前导1检测电路,可检测出尾数中第一个1的位置, 后移位器根据此位置对尾数进行左移,同时减去相应的值。LOP算法与

9、标准算法的区别在于它采用前导1预测电路代替了前导1检测电路代 替了前导1检测电路。LOP电路可以与尾数加法并行执行,这样减少整个系统的 延迟。双通道算法的结构有两个并行的数据通道,当指数差大于1时,选择far通道, 指数对阶分配较长时间,尾数运算结果规范化时的移位分配较少的时间,否则 选择close通道,此时尾数最多移一位,甚至不用移位,这样可以去掉前移位 器。在以上3种算法中,一般的标准算法延迟较大,但占用资源最少;双通道 算法虽然延迟较小,但占用资源最多。在进行后续的流水线设计时,由于结构 复杂,因而不利于流水线寄存器的插入和流水级数的划分,从而导致了时序速 度的下降。LOP算法的速度和面

10、积介于两者之间。综合比较以上三种算法以及自己知识的局限性,因此采用一般的标准算法来进 行32浮点数运算加法器的设计。3.流水线设计结构流水线处理是高速设计中的一个常用设计手段。如果某个设计的处理流程分为 若干个步骤,而且是整个数据处理是“单流向”的,即没有反馈或者是迭代运 算,前一个步骤的输出是下一个步骤的输入则可以考虑采用流水线设计方法提 系统的工作频率。流水线设计的结构如图所示:其基本结构为:将适当划分的单个操作步骤单流向串联起来。流水线操作的特点和 要求是,从时间上看数据流在各个步骤的处理是连续的。如果将每个操作步骤简化假设为通 过一个D触发器,那么流水线操作就类似一个移位寄存器组,数据

11、流依次流经D触发器,完 成每个步骤的操作。流水线时序设计如下图:St ep1St ep2St ep3a21 1St ep1St ep2St ep3b2.| |St ep1St ep2St ep3C2#3 LJ流水线设计的关键在于整个设计时序的合理安排。要求每个操作步骤的划分合理。如果前级 操作时间恰好等于后级操作时间,设计最为简单,前级的输出直接汇入后级的输入即可。如 果前级操作时间大于后级的操作时间,则需要对前级的输出数据适当缓存,才能汇入后级的 输入端。如果前级操作时间恰好小于后级的操作时间,则必须通过复制逻辑,将数据分流, 或者在前级对数据采用存储、后处理方式,否则会造成后级数据溢出。流

12、水线的处理方式相当于复制了处理模块,所以通过这种方式设计的芯片频率较高。在本文中32位浮点加法器的设计虽然没有采用流水线的设计结构,但是仍然从中得到了启发。4.32位浮点加法器的Verilog设计在进行Verilog语言设计32位浮点加法器时,要先画出流程图。在画流程图之前,要理 顺32位浮点加法器的顺序步骤,在此基础上画出其程图如图:_翱江帶符和丫变符i1 = 1/是Z*0是舍入处理小阶加1E 数右移喰尾数梯1应阶码加1I:从流程图可以看出,浮点加法运算器的完成可以分成阶码和尾数两部分。阶码只有加减运算 (左右移位),而尾数则有加减乘除4种运算。因此,浮点加法运算器主要由两个定点运算 部件组

13、成,一个是阶码运算部件来完成阶码加减,以及控制对阶时小阶的尾数右移次数和规 格化时对阶码的调整;另一个是尾数运算部件来完成尾数的加减运算并判断尾数是否已规格 化。除了这两个主要的运算部件之外,还需要一个溢出电路来判断是否溢出。根据以上的流 程图和分析,可以大致画出运算电路的结构图:E两个操作数的阶码部分,分别放在寄存器E1和E2中,它们与并行加法器相连可以计算E1 E2。阶码比较是通过E1 E2来实现的,相减结果放在计数器E。然后按E的符号来决 定哪一个阶码较大,并用E来控制其中一个尾数的移位次数。E每递减1次,相应的尾数右 移一位,直到E = 0为止。一旦尾数调整完毕,就可按通常的加、减方法

14、处理,并将其结果 的阶码放入E寄存器中。在画出浮点加法运算器的内部电路后,就可以用Verilog语言来编 写程序了。在编写的程序中使用的是同步有限状态机来实现电路的功能的。同步有限状态机 的编写在理顺了浮点加法运算的运算步骤之后,很容易可以得到电路的几个状态,以及各个 状态之间相互跳并的条件。在弄清楚各个状态之间的跳并条件之后很容易就可以画出有限状 态机的状态迁移图。通过有限状态机的迁移图,可以比较方便的写出状态机的Verilog语言 描述。再结合电路结构框图,把电路的各部分功能加以实现填充到状态机中就完成了32位 浮点加法器的Verilog语言设计。此时,可以用软件进行仿真测试,得到仿真波形

15、如下图:沁卽建露丁站汽-IE畑圮-対曲口三基 lie E:it韶cTools Wiridow粧恤isKOIDGmilG 11 刚顾 SOCGoooiiioccineaiDooo(Dioci师11 咖間加罚 W JBOiiOLOl 11C01111OK!U:C(;MG1*呦丈LTUytrLTJIiJUtTLHjrriLTLT可1111n护 A/ce嗣K4前踽!訓皿紳1屈hx. i:(aiinooi!niaiii i:o.msiooi 81190011101050)c:*止淪图中ix,iy为数据输入信号elk为时钟信号,reset为复位信号,oz为数据输出信号,of 为判断是否溢出的信号输出。同步

16、有限状态机的源代码和测试程序代码如下:/同步有限状态机代码 if(xm=0)module floatadder(elk,reset,ix,iy,oz,ofw);/begin定义模块端口;ze,zm=ye,ym;input clk,rese t; / 时钟、复位信号;nex tstat e=over;inpu t31:0ix, iy;/输入信号;endou tput 31:0oz;/输出信号;elseoutput ofw; /溢出位信号;if(ym=0)reg31:0oz;beginreg23:0xm,ym,zm;/定义尾数;ze,zm=xe,xm;reg7:0xe,ye,ze; /定义阶码ne

17、xtstateye)beginye=ye+1; /阶码左移,阶码加1ym=1b0,ym23:1;if(ym=0)beginzm=xm;ze=xe;zs=ix31; oz=zs,xe,zm23:1;beginxe=ix30:23;xm=1b1,ix22:0;ye=iy30:23;ym=1b1,iy22:0;nextstate= zeroek;end/操作数检查,判断操作数是否为0;zeroek:endelse nextstate=exequal;endelsebeginxe=xe+1; /阶码左移 ,阶码加1;xm=1b0,xm23:1;if(xm=0)addm =3b011,begininfi

18、fl=3b100,if(xe=ye)zerofl=3b101,nextstate=addm;over=3b110;assign ofw=(s tat e=over)?1:0;/判断溢出位/每一个时钟产生一个可能的状态变化always(posedge elk)if(!reset) state=start;elsestate=nextstate;/产生下一个状态的组合逻辑always(state)ease(state)start:nextstate=over;beginbeginzm=ym;ze=ye; zs=iy31; oz=zs,ze,zm23:1; nextstate=over;endels

19、enextstate=exequal;endend/尾数求和运算;addm:beginze=xe;if(iy31)mc,zm=xm+(ym);elsemc,zm=xm+ym;if(zm=24b0) nextstate=over;elsenextstate=infifl;end/结果规格化操作;infifl:beginif(mc)begin zm=mc,zm23:1; ze=ze+1; zs=ix31; oz=zs,ze,zm22:0; if(ze=8b1111_1111) /溢出 nextstate=over;elsenextstate=zerofl;end参考文献:elsenextstate

20、=zerofl;end/结果做舍入处理;zerofl:beginif(zm23=1b1)beginzm=1b0,zm23:1;/ 向左移位;ze=ze-1;zs=ix31;oz=zs,ze,zm22:0; nextstate=zerofl;endelseif(zm23:22=2b0)beginzm 向右移位;ze=ze+1;zs=ix31;oz=zs,ze,zm22:0;if(ze=8b1111_1111) nextstate=over;elsenextstate=zerofl;endelsenextstate=over;endover:beginenddefault:state=start;endcaseendmodule1 崔云娟.基于FPGA浮点运算器的设计及其在雷达中的应用D.西安:西安电子科技大学,2007:18-21.2 吉伟,黄巾,杨靓,黄士坦.基于FPGA的32位浮点加法器的设计J.微电子学与计算机,2008,25 (6) 209-211.3 杨靓,徐伟,黄士坦.FPGA上浮点加/减法器的设计J.计算机工程与应用,2003,2(24) ,39-41.

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。