FPGA实验三:液晶屏的显示设计

FPGA实验三:液晶屏的显示设计

《FPGA实验三:液晶屏的显示设计》由会员分享,可在线阅读,更多相关《FPGA实验三:液晶屏的显示设计(30页珍藏版)》请在装配图网上搜索。

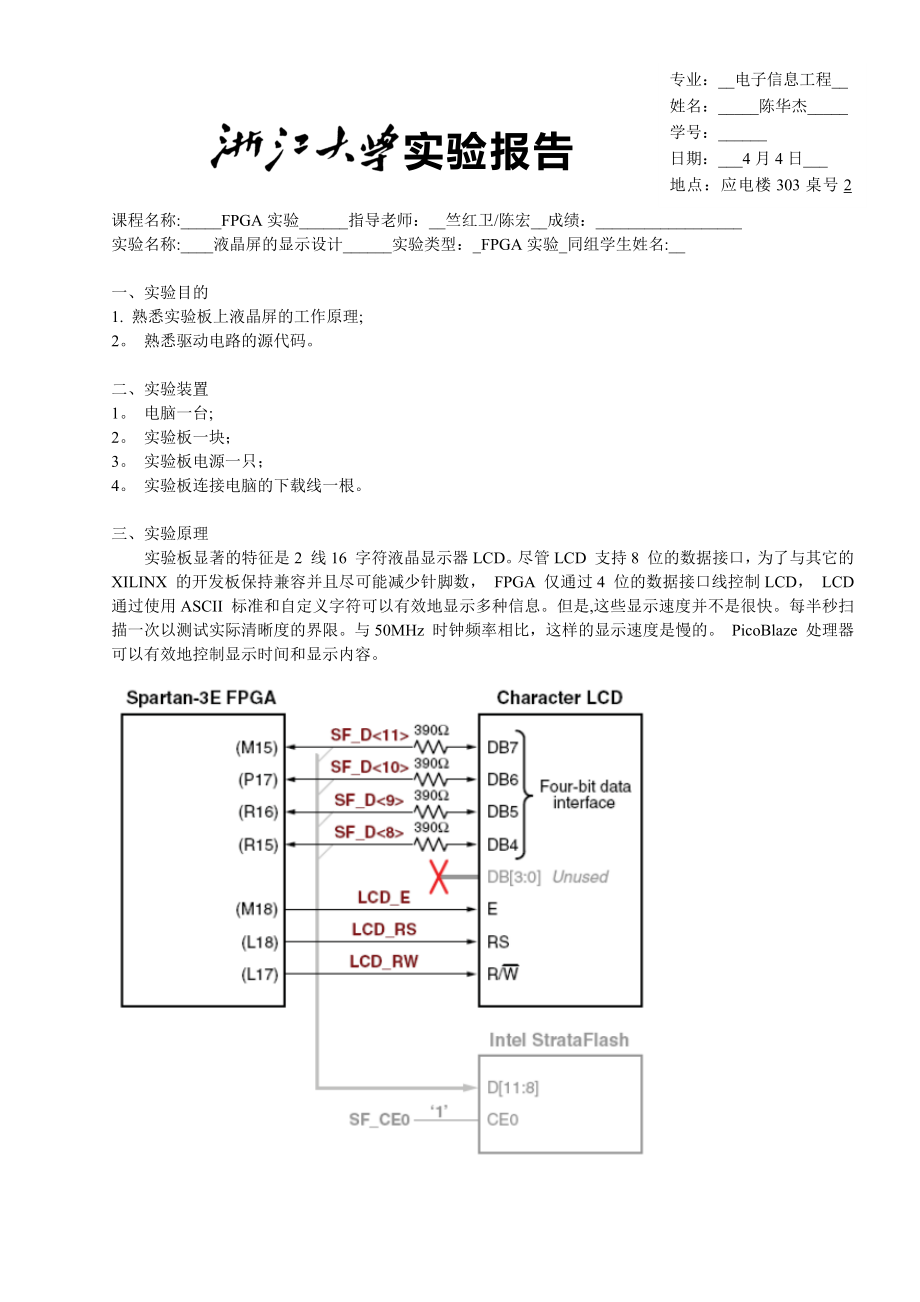

1、专业:_电子信息工程_姓名:_陈华杰_学号:_日期:_4月4日_地点:应电楼303桌号2组 实验报告课程名称:_FPGA实验_指导老师:_竺红卫/陈宏_成绩:_实验名称:_液晶屏的显示设计_实验类型:_FPGA实验_同组学生姓名:_一、 实验目的1. 熟悉实验板上液晶屏的工作原理;2。 熟悉驱动电路的源代码。二、实验装置1。 电脑一台;2。 实验板一块;3。 实验板电源一只;4。 实验板连接电脑的下载线一根。三、实验原理实验板显著的特征是2 线16 字符液晶显示器LCD。尽管LCD 支持8 位的数据接口,为了与其它的XILINX 的开发板保持兼容并且尽可能减少针脚数, FPGA 仅通过4 位的

2、数据接口线控制LCD, LCD 通过使用ASCII 标准和自定义字符可以有效地显示多种信息。但是,这些显示速度并不是很快。每半秒扫描一次以测试实际清晰度的界限。与50MHz 时钟频率相比,这样的显示速度是慢的。 PicoBlaze 处理器可以有效地控制显示时间和显示内容。字符 LCD 的供电电压是5V。 FPGA 的I/O 口信号的电压是3.3V。但是, FPGA 的输出电平是通过LCD 来识别是有效的低电平还是高电平。 LCD 控制器接收5V TTL 信号电平, FPGA输出3.3V 的LCMOS 以满足5V TTL 电压要求。数据线上的390 欧串联电阻,当LCD 驱动一个逻辑高电平时,其

3、用来防止了FPGA 和SrtataFlsah I/O 管脚的超负载.当LCD_RW 为高时, LCD驱动数据线。在绝大多数应用中, LCD作为只读外围设备,几乎没有从显示器读数据。四、操作方法和实验步骤对于程序的各个步骤,如新建项目、新建Verilog HDL、新建.ucf文件、Synthesize、Implement Design、Generate Programming File、Configure Target Device等等,在实验一中已经展示过,每一次实验的基本操作步骤都是差不多的,故这里不再重复阐述。本次实验总共需要做三份程序并观察现象:1)例程2)设计按键拨动时显示小时、分钟和

4、秒,中间分别空一格.3)按键拨动开始显示,10秒钟显示结束,结束时LCD上显示ABCDEF,同时八只LED灯亮.五、实验源代码和现象1)例程UCF文件如下:NET CLK_50MHZ” LOC=”C9;NET ”LCD_D0” LOC=R15”;NET LCD_D1” LOC=”R16;NET ”LCD_D” LOC=M15”;NET LCD_E LOC=M18;NET LCD_RS LOC=”L18”;NET ”LCD_RW LOC=”L17”;源代码如下:module lcd_write_number_test(input CLK_50MHZ,output LCD_E,output LCD

5、_RS,output LCD_RW,output 3:0 LCD_D);wire if_ready;reg if_write;reg 31:0 if_data;reg 1:0 state;reg 31:0 cntr;parameter IDLE = 2b00,IF_WRITE_1 = 2b01,SET_IF_WRITE_0 = 2b10,WAIT = 2b11;/ Instantiate the Unit Under Test (UUT)lcd_write_number uut(。CLK_50MHZ(CLK_50MHZ),.LCD_E(LCD_E),。LCD_RS(LCD_RS),.LCD_R

6、W(LCD_RW),。LCD_D(LCD_D),.if_data(if_data),.if_write(if_write),。if_ready(if_ready));initial beginif_data = 32habba0123;state = IDLE;if_write = 1b0;cntr = 32b0;endalways (posedge CLK_50MHZ) begincase (state)IDLE:if (if_ready) beginif_data = if_data + 1b1;if_write = 1b1;state = IF_WRITE_1;cntr = 32b0;e

7、ndIF_WRITE_1: / this state to keep if_write up for 2 cyclesstate = SET_IF_WRITE_0;SET_IF_WRITE_0: / set if_write 0 and start the counterbeginif_write = 1b0;state = WAIT;cntr = 32b0;endWAIT:if (cntr 25000000) / wait for 0.5 secondscntr = cntr + 32b1;elsestate = IDLE;endcaseendendmoduletimescale 1ns /

8、 1psmodule lcd_write_number(input CLK_50MHZ,output LCD_E,output LCD_RS,output LCD_RW,output 3:0 LCD_D,input 31:0 if_data,input if_write,output if_ready);reg 7:0 disp_data;reg disp_rs;reg 31:0 disp_delay;reg disp_write;wire disp_ready;reg disp_b8;reg 7:0 char;reg 1:0 state;reg 31:0 number;reg init_do

9、ne;reg running;reg 4:0 shift_cntr;reg if_ready_r;assign if_ready = if_ready_r;lcd_display display(.clk(CLK_50MHZ),.rst(1b0),.lcd_e(LCD_E),.lcd_rw(LCD_RW),.lcd_rs(LCD_RS),.lcd_d(LCD_D),。if_data(disp_data),.if_rs(disp_rs),.if_delay(disp_delay),。if_write(disp_write),。if_ready(disp_ready),。if_8bit(disp_

10、b8));parameter NB_CHARS = 8d12;parameter START = 2b00,WAIT_WRITE_0 = 2b01,WRITE_1 = 2b10,WAIT_WRITE_1 = 2b11;initial beginstate = 2b00;char = 8b0;init_done = 1b0;if_ready_r = 1b0;shift_cntr = 5b0;endalways (posedge CLK_50MHZ) beginif (init_done & char 8d16) beginif (disp_ready)if_ready_r = 1b1;if (i

11、f_write) beginchar = 4d8; / reset the displayendend else if (char = 8d16) beginif_ready_r = 1b0;case (state)START:if (disp_ready) begindisp_write = 1b1;state = WAIT_WRITE_0;endWAIT_WRITE_0:state = WRITE_1;WRITE_1:begindisp_write = 1b0;state = 2b11;endWAIT_WRITE_1:beginstate =START;char = char + 8b1;

12、endendcase / case (state)end / else: !if(!running)end / always (posedge CLK_50MHZ)always (negedge CLK_50MHZ) begin/ these next steps initialize the LCD display:case (char)0:begindisp_b8 = 1b0;disp_data = 8h30;disp_delay = 32d10000000;disp_rs = 1b0;end1: disp_data = 8h30;2:begindisp_data = 8h30;disp_

13、delay = 32d1000000;end3:begindisp_data = 8h20;disp_delay = 32d20000;end4:begindisp_b8 = 1b1;disp_data = 8h28;end5: disp_data = 8h06;6: disp_data = 8h0C;7:begindisp_data = 8h01;disp_delay = 32d1000000;init_done = 1b1;shift_cntr = 5d9;end8: / this state provides an entry point to reset the display and

14、 then/ go on to the default state that writes the numberbegindisp_rs = 1b0;disp_data = 8h01;disp_delay = 32d1000000;shift_cntr = 5b0;number = if_data;enddefault:/ state machine to print a 32-bit number outif (disp_ready & state = START) beginif (shift_cntr 5d8) begindisp_rs = 1b1;disp_delay = 32d200

15、00;if (number31:28 4b1010)disp_data = number31:28 + 8h30;elsedisp_data = number31:28 + 8h37;number = number 4;shift_cntr = shift_cntr + 5b1;endendendcase / case (char)end / always (negedge CLK_50MHZ)endmoduletimescale 1ns / 1psmodule lcd_display(input clk,input rst,output lcd_e,output lcd_rw,output

16、lcd_rs,output 3:0 lcd_d,input 7:0 if_data,input if_rs,input 31:0 if_delay,input if_write,output if_ready,input if_8bit);reg 2:0 state;reg lcdr_e;reg 3:0 lcdr_d;reg 31:0 wait_cntr;reg ready;reg init_done;parameter IDLE = 3b000,WAIT_PULSE_E_0 = 3b001,LOAD_LOWER_NIBBLE = 3b010,WAIT_PULSE_E_1 = 3b011,WA

17、IT_COMMAND = 3b100;parameter PULSE_E_DLY = 32d12;parameter INIT_TIME = 32d20000000;assign lcd_d = lcdr_d;assign lcd_rs = if_rs;assign lcd_rw = 1b0;assign lcd_e = lcdr_e;assign if_ready = ready;initial beginstate = IDLE;ready = 1b0;lcdr_e = 1b0;init_done = 1b0;endalways (posedge clk) beginif (rst) be

18、ginstate = IDLE;end else if (!init_done) beginif (wait_cntr INIT_TIME)wait_cntr = wait_cntr + 1;else begininit_done = 1b1;ready = 1b1;endend else begincase (state)IDLE:beginif (if_write) beginlcdr_e = 1b1;lcdr_d = if_data7:4; / upper nibble firstready = 1b0;wait_cntr = 32b0;state = WAIT_PULSE_E_0;en

19、dendWAIT_PULSE_E_0:if (wait_cntr PULSE_E_DLY) beginwait_cntr = wait_cntr + 1;end else beginlcdr_e = 1b0;wait_cntr = 0;if (if_8bit)state = LOAD_LOWER_NIBBLE;elsestate = WAIT_COMMAND;endLOAD_LOWER_NIBBLE:if (wait_cntr PULSE_E_DLY) beginwait_cntr = wait_cntr + 1;end else beginwait_cntr = 0;lcdr_e = 1b1

20、;lcdr_d = if_data3:0; / lower nibblestate = WAIT_PULSE_E_1;endWAIT_PULSE_E_1:if (wait_cntr PULSE_E_DLY) beginwait_cntr = wait_cntr + 1;end else beginlcdr_e = 1b0;wait_cntr = 0;state = WAIT_COMMAND;endWAIT_COMMAND:if (wait_cntr if_delay) beginwait_cntr = wait_cntr + 32b1;end else beginwait_cntr LOC=R

21、15”;NET LCD_D LOC=”R16”;NET LCD_D2” LOC=”P17;NET ”LCD_D LOC=”M15;NET ”LCD_E LOC=M18”;NET LCD_RS” LOC=L18”;NET ”LCD_RW LOC=L17;NET SW1 LOC=L14;源代码如下:module lcd_write_number_test(input SW1,input CLK_50MHZ,output LCD_E,output LCD_RS,output LCD_RW,output 3:0 LCD_D);wire if_ready;reg if_write;reg 31:0 if

22、_data;reg 1:0 state;reg 31:0 cntr;parameter IDLE = 2b00,IF_WRITE_1 = 2b01,SET_IF_WRITE_0 = 2b10,WAIT = 2b11;/ Instantiate the Unit Under Test (UUT)lcd_write_number uut(.SW1(SW1),.CLK_50MHZ(CLK_50MHZ),。LCD_E(LCD_E),。LCD_RS(LCD_RS),.LCD_RW(LCD_RW),。LCD_D(LCD_D),。if_data(if_data),。if_write(if_write),.i

23、f_ready(if_ready));initial beginif_data = 32h19044012;state = IDLE;if_write = 1b0;cntr = 32b0;endalways (posedge CLK_50MHZ) begincase (state)IDLE:if (if_ready) beginif(if_data31:0=32h23059059)if_data = 32h0;else if(if_data27:0=28h9059059)if_data = if_data + 32h6fa6fa7;else if(if_data19:0=20h59059)if

24、_data = if_data + 32hfa6fa7;else if(if_data15:0=16h9059)if_data = if_data + 32h6fa7;else if(if_data7:0=8h59)if_data = if_data + 32hfa7;else if(if_data3:0=4h9)if_data = if_data + 32h7;else if_data = if_data + 1b1;if_write = 1b1;state = IF_WRITE_1;cntr = 32b0;endIF_WRITE_1: / this state to keep if_wri

25、te up for 2 cyclesstate = SET_IF_WRITE_0;SET_IF_WRITE_0: / set if_write 0 and start the counterbeginif_write = 1b0;state = WAIT;cntr = 32b0;endWAIT:if (cntr 50000000) / wait for 1 secondscntr = cntr + 32b1;elsestate = IDLE;endcaseendendmoduletimescale 1ns / 1psmodule lcd_display(input clk,input rst,

26、output lcd_e,output lcd_rw,output lcd_rs,output 3:0 lcd_d,input 7:0 if_data,input if_rs,input 31:0 if_delay,input if_write,output if_ready,input if_8bit);reg 2:0 state;reg lcdr_e;reg 3:0 lcdr_d;reg 31:0 wait_cntr;reg ready;reg init_done;parameter IDLE = 3b000,WAIT_PULSE_E_0 = 3b001,LOAD_LOWER_NIBBLE

27、 = 3b010,WAIT_PULSE_E_1 = 3b011,WAIT_COMMAND = 3b100;parameter PULSE_E_DLY = 32d12;parameter INIT_TIME = 32d20000000;assign lcd_d = lcdr_d;assign lcd_rs = if_rs;assign lcd_rw = 1b0;assign lcd_e = lcdr_e;assign if_ready = ready;initial beginstate = IDLE;ready = 1b0;lcdr_e = 1b0;init_done = 1b0;endalw

28、ays (posedge clk) beginif (rst) beginstate = IDLE;end else if (!init_done) beginif (wait_cntr INIT_TIME)wait_cntr = wait_cntr + 1;else begininit_done = 1b1;ready = 1b1;endend else begincase (state)IDLE:beginif (if_write) beginlcdr_e = 1b1;lcdr_d = if_data7:4; / upper nibble firstready = 1b0;wait_cnt

29、r = 32b0;state = WAIT_PULSE_E_0;endendWAIT_PULSE_E_0:if (wait_cntr PULSE_E_DLY) beginwait_cntr = wait_cntr + 1;end else beginlcdr_e = 1b0;wait_cntr = 0;if (if_8bit)state = LOAD_LOWER_NIBBLE;elsestate = WAIT_COMMAND;endLOAD_LOWER_NIBBLE:if (wait_cntr PULSE_E_DLY) beginwait_cntr = wait_cntr + 1;end el

30、se beginwait_cntr = 0;lcdr_e = 1b1;lcdr_d = if_data3:0; / lower nibblestate = WAIT_PULSE_E_1;endWAIT_PULSE_E_1:if (wait_cntr PULSE_E_DLY) beginwait_cntr = wait_cntr + 1;end else beginlcdr_e = 1b0;wait_cntr = 0;state = WAIT_COMMAND;endWAIT_COMMAND:if (wait_cntr if_delay) beginwait_cntr = wait_cntr +

31、32b1;end else beginwait_cntr = 0;if (!if_write) beginstate = IDLE;ready = 1b1;endendendcase / case (state)endendendmoduletimescale 1ns / 1psmodule lcd_write_number(input CLK_50MHZ,input SW1,output LCD_E,output LCD_RS,output LCD_RW,output 3:0 LCD_D,input 31:0 if_data,input if_write,output if_ready);r

32、eg 7:0 disp_data;reg disp_rs;reg 31:0 disp_delay;reg disp_write;wire disp_ready;reg disp_b8;reg 7:0 char;reg 1:0 state;reg 31:0 number;reg init_done;reg running;reg 4:0 shift_cntr;reg if_ready_r;assign if_ready = if_ready_r;lcd_display display(。clk(CLK_50MHZ),。rst(1b0),。lcd_e(LCD_E),。lcd_rw(LCD_RW),

33、。lcd_rs(LCD_RS),.lcd_d(LCD_D),。if_data(disp_data),.if_rs(disp_rs),。if_delay(disp_delay),.if_write(disp_write),.if_ready(disp_ready),。if_8bit(disp_b8);parameter NB_CHARS = 8d12;parameter START = 2b00, WAIT_WRITE_0 = 2b01, WRITE_1 = 2b10, WAIT_WRITE_1 = 2b11; initial beginstate = 2b00;char = 8b0;init_

34、done = 1b0;if_ready_r 8d16) begin if (disp_ready) if_ready_r = 1b1; if (if_write) begin char = 4d8; / reset the display endend else if (char = 8d16) begin if_ready_r = 1b0; case (state) START:if (disp_ready) begindisp_write = 1b1;state = WAIT_WRITE_0;endWAIT_WRITE_0:state = WRITE_1;WRITE_1:begindisp

35、_write = 1b0;state = 2b11;endWAIT_WRITE_1:beginstate = START;char = char + 8b1;endendcase / case (state)end / else: !if(!running)end / always (posedge CLK_50MHZ)always (negedge CLK_50MHZ) begin/ these next steps initialize the LCD display:case (char)0:begindisp_b8 = 1b0;disp_data = 8h30;disp_delay =

36、 32d10000000;disp_rs = 1b0;end1: disp_data = 8h30;2:begindisp_data = 8h30;disp_delay = 32d1000000;end3:begindisp_data = 8h20;disp_delay = 32d20000;end4:begindisp_b8 = 1b1;disp_data = 8h28;end5: disp_data = 8h06;6: disp_data = 8h0C;7:begindisp_data = 8h01;disp_delay = 32d1000000;init_done = 1b1;shift

37、_cntr = 5d9;end8: / this state provides an entry point to reset the display and then/ go on to the default state that writes the numberbegindisp_rs = 1b0;disp_data = 8h01;disp_delay = 32d1000000;shift_cntr = 5b0;number = if_data;enddefault:/ state machine to print a 32-bit number outif (SW1)beginif

38、(disp_ready & state = START) begin if (shift_cntr 5d8) begin disp_rs = 1b1; disp_delay = 32d20000; if(shift_cntr = 5d2) | (shift_cntr = 5d5)) begin disp_data = 8h20; endelse begin if (number31:28 4b1010) disp_data = number31:28 + 8h30; else disp_data = number31:28 + 8h37; endnumber = number 4; shift

39、_cntr = shift_cntr + 5b1;endendendendcase / case (char)end / always (negedge CLK_50MHZ)endmodule实验现象:当SW1为低电平时,LCD无显示.SW1向上拨后,如下图,LCD显示小时、分钟和秒,中间分别空一格,且该输出显示会按照时钟的样式计时、刷新,每过一秒钟秒位进一,秒的个位满10进位,秒数满60则分数增一当SW1再次向下拨,LCD显示关闭,但始终仍然在计时。程序刚烧进板子时,时钟的初始时间是人为设定的19时44分12秒.3)按键拨动开始显示,10秒钟显示结束,结束时LCD上显示ABCDEF,同时八只

40、LED灯亮。UCF文件如下:NET ”CLK_50MHZ” LOC=”C9”;NET ”LCD_D” LOC=R15;NET LCD_D LOC=R16;NET LCD_D2” LOC=P17;NET ”LCD_D3” LOC=M15;NET LCD_E LOC=M18;NET ”LCD_RS LOC=L18;NET ”LCD_RW” LOC=L17;NET ”SW1” LOC=L14;NET ”LED0 LOC=F12;NET LED1” LOC=E12;NET LED2 LOC=E11;NET ”LED3 LOC=F11;NET LED4 LOC=C11;NET LED5 LOC=D11;

41、NET ”LED6 LOC=E9;NET ”LED7 LOC=F9;源代码如下:module lcd_write_number_test(input CLK_50MHZ,input SW1,output LCD_E,output LCD_RS,output LCD_RW,output 3:0 LCD_D,output LED0,output LED1,output LED2,output LED3,output LED4,output LED5,output LED6,output LED7);wire if_ready;reg if_write;reg 31:0 if_data;reg 1:

42、0 state;reg 31:0 cntr;parameter IDLE = 2b00,IF_WRITE_1 = 2b01,SET_IF_WRITE_0 = 2b10,WAIT = 2b11;/ Instantiate the Unit Under Test (UUT)lcd_write_number uut(.SW1(SW1),。CLK_50MHZ(CLK_50MHZ),。LCD_E(LCD_E),.LCD_RS(LCD_RS),。LCD_RW(LCD_RW),.LCD_D(LCD_D),.if_data(if_data),。if_write(if_write),.if_ready(if_r

43、eady),。LED0(LED0),。LED1(LED1),。LED2(LED2),。LED3(LED3),。LED4(LED4),.LED5(LED5),.LED6(LED6),.LED7(LED7);initial beginif_data = 32h19044012;state = IDLE;if_write = 1b0;cntr = 32b0;endalways (posedge CLK_50MHZ) begincase (state)IDLE:if (if_ready) beginif(if_data31:0=32h23059059)if_data = 32h0;else if(if

44、_data27:0=28h9059059)if_data = if_data + 32h6fa6fa7;else if(if_data19:0=20h59059)if_data = if_data + 32hfa6fa7;else if(if_data15:0=16h9059)if_data = if_data + 32h6fa7;else if(if_data7:0=8h59)if_data = if_data + 32hfa7;else if(if_data3:0=4h9)if_data = if_data + 32h7;else if_data = if_data + 1b1;if_wr

45、ite = 1b1;state = IF_WRITE_1;cntr = 32b0;endIF_WRITE_1: / this state to keep if_write up for 2 cyclesstate = SET_IF_WRITE_0;SET_IF_WRITE_0: / set if_write 0 and start the counterbeginif_write = 1b0;state = WAIT;cntr = 32b0;endWAIT:if (cntr 50000000) / wait for 1 secondscntr = cntr + 32b1;elsestate =

46、 IDLE;endcaseendendmoduletimescale 1ns / 1psmodule lcd_write_number(input CLK_50MHZ,input SW1,output LCD_E,output LCD_RS,output LCD_RW,output 3:0 LCD_D,output LED0,output LED1,output LED2,output LED3,output LED4,output LED5,output LED6,output LED7,input 31:0 if_data,input if_write,output if_ready);r

47、eg 7:0 disp_data;reg disp_rs;reg 31:0 disp_delay;reg disp_write;wire disp_ready;reg disp_b8;reg 7:0 char;reg 1:0 state;reg 31:0 number;reg init_done;reg running;reg 4:0 shift_cntr;reg if_ready_r;reg 28:0 cnt;reg cnt_state;reg light;assign if_ready = if_ready_r;lcd_display display(。clk(CLK_50MHZ),.rs

48、t(1b0),。lcd_e(LCD_E),。lcd_rw(LCD_RW),。lcd_rs(LCD_RS),。lcd_d(LCD_D),。if_data(disp_data),。if_rs(disp_rs),.if_delay(disp_delay),。if_write(disp_write),。if_ready(disp_ready),。if_8bit(disp_b8);parameter NB_CHARS = 8d12;parameter START = 2b00, WAIT_WRITE_0 = 2b01, WRITE_1 = 2b10, WAIT_WRITE_1 = 2b11; initi

49、al beginstate = 2b00;char = 8b0;init_done = 1b0;if_ready_r = 1b0;shift_cntr = 5b0;cnt_state = 1b0;cnt = 29b0;light 8d16) begin if (disp_ready) if_ready_r = 1b1; if (if_write) begin char = 4d8; / reset the display endend else if (char = 8d16) begin if_ready_r = 1b0; case (state) START:if (disp_ready)

50、 begindisp_write = 1b1;state = WAIT_WRITE_0;endWAIT_WRITE_0:state = WRITE_1;WRITE_1:begindisp_write = 1b0;state = 2b11;endWAIT_WRITE_1:beginstate = START;char = char + 8b1;endendcase / case (state)end / else: !if(!running)end / always (posedge CLK_50MHZ)always (posedge CLK_50MHZ)if (!SW1) begincnt =

51、 29b0;cnt_state=1b0;endelse if (cnt=29h1dcd6500) cnt_state=1b1;else cnt = cnt+1b1;always (negedge CLK_50MHZ) begin/ these next steps initialize the LCD display:case (char)0:begindisp_b8 = 1b0;disp_data = 8h30;disp_delay = 32d10000000;disp_rs = 1b0;end1: disp_data = 8h30;2:begindisp_data = 8h30;disp_

52、delay = 32d1000000;end3:begindisp_data = 8h20;disp_delay = 32d20000;end4:begindisp_b8 = 1b1;disp_data = 8h28;end5: disp_data = 8h06;6: disp_data = 8h0C;7:begindisp_data = 8h01;disp_delay = 32d1000000;init_done = 1b1;shift_cntr = 5d9;end8: / this state provides an entry point to reset the display and

53、 then/ go on to the default state that writes the numberbegindisp_rs = 1b0;disp_data = 8h01;disp_delay = 32d1000000;shift_cntr = 5b0;number = if_data;enddefault:/ state machine to print a 32-bit number outif (SW1 (!cnt_state))beginif (disp_ready state = START) begin if (shift_cntr 5d8) begin disp_rs

54、 = 1b1; disp_delay = 32d20000; if((shift_cntr = 5d2) (shift_cntr = 5d5) disp_data = 8h20; else begin if (number31:28 4b1010) disp_data = number31:28 + 8h30; else disp_data = number31:28 + 8h37; end number = number 4; shift_cntr = shift_cntr + 5b1;endendlight = 1b0;endelse if (SW1 & cnt_state)beginif (disp_rea

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。