《EDA技术与项目训练》试题

《EDA技术与项目训练》试题

《《EDA技术与项目训练》试题》由会员分享,可在线阅读,更多相关《《EDA技术与项目训练》试题(4页珍藏版)》请在装配图网上搜索。

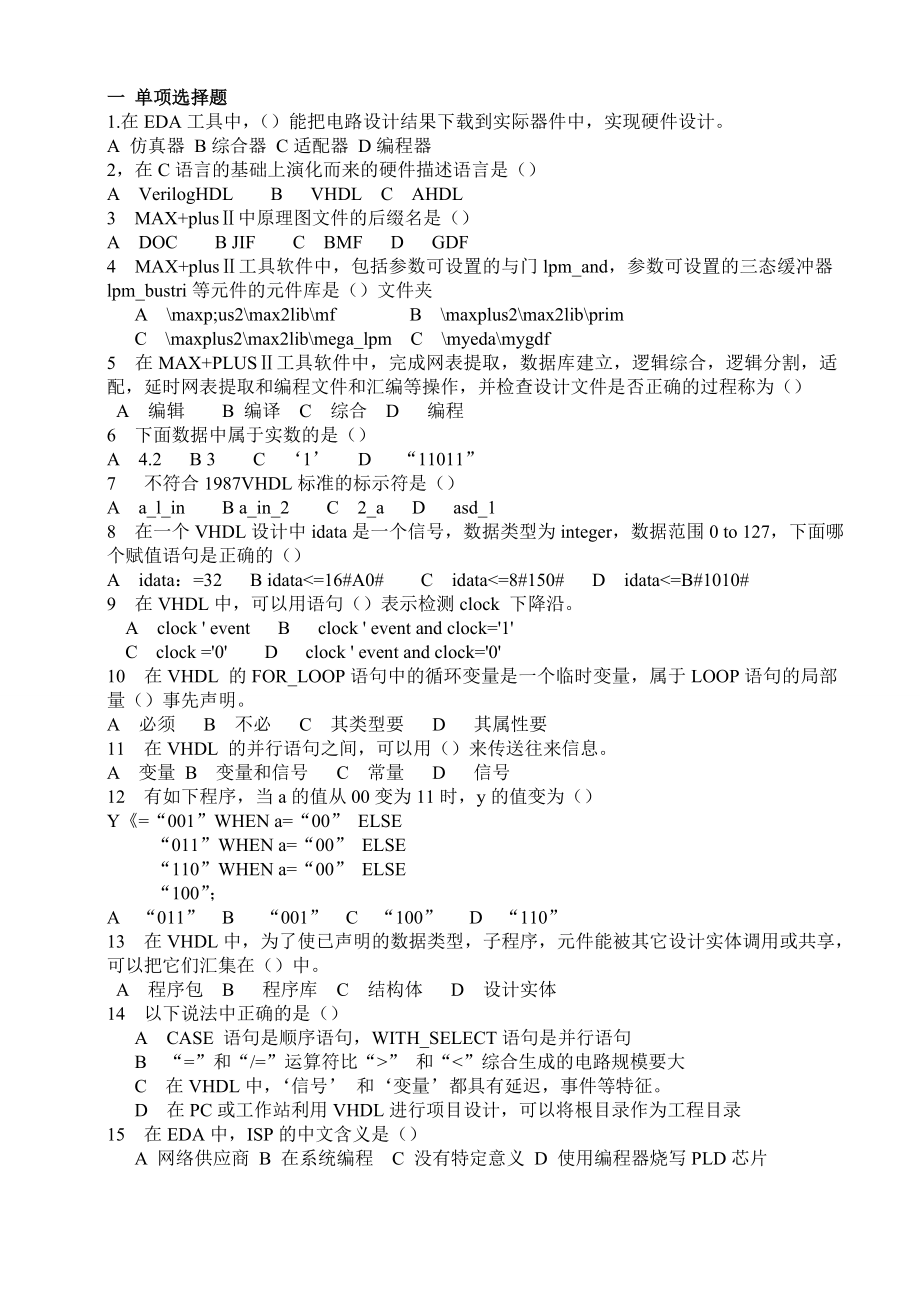

1、一 单项选择题1. 在EDA工具中,()能把电路设计结果下载到实际器件中,实现硬件设计。A 仿真器 B综合器 C适配器 D编程器2,在C语言的基础上演化而来的硬件描述语言是()A VerilogHDL B VHDL C AHDL 3 MAX+plus中原理图文件的后缀名是()A DOC B JIF C BMF D GDF4 MAX+plus工具软件中,包括参数可设置的与门lpm_and,参数可设置的三态缓冲器lpm_bustri等元件的元件库是()文件夹 A maxp;us2max2libmf B maxplus2max2libprim C maxplus2max2libmega_lpm C

2、myedamygdf5 在MAX+PLUS工具软件中,完成网表提取,数据库建立,逻辑综合,逻辑分割,适配,延时网表提取和编程文件和汇编等操作,并检查设计文件是否正确的过程称为() A 编辑 B 编译 C 综合 D 编程6 下面数据中属于实数的是()A 4.2 B 3 C 1 D “11011”7 不符合1987VHDL标准的标示符是()A a_l_in B a_in_2 C 2_a D asd_18 在一个VHDL设计中idata是一个信号,数据类型为integer,数据范围0 to 127,下面哪个赋值语句是正确的()A idata:=32 B idata=16#A0# C idata=8#

3、150# D idata” 和“”综合生成的电路规模要大 C 在VHDL中,信号 和变量都具有延迟,事件等特征。 D 在PC或工作站利用VHDL进行项目设计,可以将根目录作为工程目录15 在EDA中,ISP的中文含义是() A 网络供应商 B 在系统编程 C 没有特定意义 D 使用编程器烧写PLD芯片二 填空题1 EDA设计流程包括_ , _ , _和_四个步骤,以及相应的_ , _和_三个设计验证过程。2,利用EDA技术进行电路设计输入有多种方式,如_ , _,_3,CPLD器件中至少包含_ , _和_三种结构4,假设开始执行如下进程时,a,b,c,d 的值分别为1 0 1 0 .执行完,信

4、号x的值为_信号y的值为 _PROCESS(a,b,c)BEGIN d=a; x=c AND d; d=b; y=c AND d;END PROCESS;U25,设已用VHDL完成一个二输入端与非门mynd2的设计,并将设计的元件声明按如下格式装入到程序包中, x1U11COMPONENT mynd2 x2 y PORT(a,b:IN STD_LOGIC; x3 c:OUT STD_LOGIC);END COMPONENT;用元件例化语句完成如右图所示电路(只须完成结构体部分的语句)ARCHITECTURE one OF mynd31 IS SIGNAL x:STD_LOGIC;BEGIN_E

5、ND one;三 简答题1,简述MAX+plus的原理图输入法的基本操作流程。2,简述变量与信号的区别3,简述WHEN_ELSE条件信号赋值语句和IF_ELSE顺序语句的异同。 四 解释程序 要求:1. 解释带有下划线的语句。2. 画出该程序的引脚示意图。3. 说明该程序逻辑功能。LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY aaa IS _PORT(s1,s0:IN STD_LOGIC;_ d3,d2,d1,d0:IN STD_LOGIC; y:OUT STD_LOGIC);END aaa;ARCHITECTURE one OF aaa IS

6、 SIGNAL s:STD_LOGIC_VECTOR(1 DOWNTO 0);_BEGIN s=s1&s0;_ WITH s SELECT y=d0 WHEN “00”,_ d0 WHEN “01”, d0 WHEN “10”, d0 WHEN “11”,XWHEN OTHERS;END one;五,改错题 以下程序要实现下降沿触发的T触发器,其原理图和逻辑功能表如下。请找出程序中的错误,并在所在的语句右边改正。(3个语法错误,1个逻辑错误,同一个错误在多条语句中出现,属于同一个错误,并且都要改正。)LIBRARY IEEE;t qclkUSE IEEE.STD_LOGIC_1164.ALL;

7、ENTITY 5tff IS PORT(t:IN STD_LOGIC; clk :IN STD_LOGIC; q :IN STD_LOGIC); 输出 clk t q qn+1 0 0 0 0 1 1 保持 1 0 1 1 1 0 翻转 输入END 5tff;ARCHITECTURE one OF 5tff ISBEGIN PROCESS(clk) BEGINIF clk= 0 THEN IF t= 1 THEN q=NOT q;END IF; END PROCESS;END one;六 编程题 1,用CASE 语句设计一个数据选择器MUX,其系统模块图和功能表如下图所示。(8分) SEL(1:0) SEL COUNTMUX 00 AIN AND BIN AIN(1:0) 01 AIN XOR BIN COUNT(1:0) 10 NOT AIN BIN(1:0) 11 NOT BIN OTHERS Xrst q1.0clk2,用状态机的设计方法设计一个带复位端rst(低电平复位,复位时计数器输出全为1)的4进制减计数器。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。