2023年公司提供基于的开关磁阻电机驱动程序全套

2023年公司提供基于的开关磁阻电机驱动程序全套

《2023年公司提供基于的开关磁阻电机驱动程序全套》由会员分享,可在线阅读,更多相关《2023年公司提供基于的开关磁阻电机驱动程序全套(96页珍藏版)》请在装配图网上搜索。

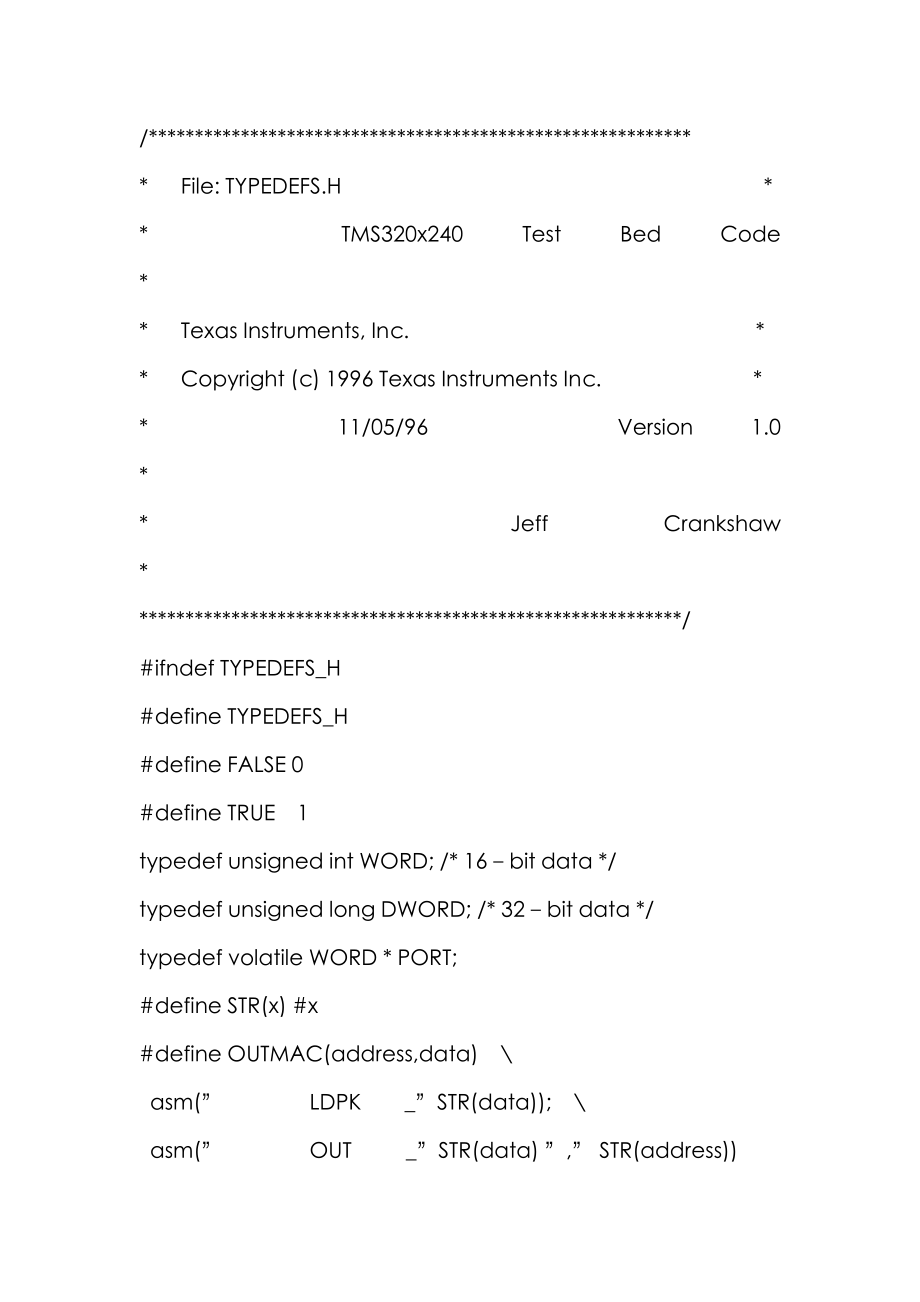

1、/* File: TYPEDEFS.H * TMS320x240 Test Bed Code * Texas Instruments, Inc. * Copyright (c) 1996 Texas Instruments Inc. * 11/05/96 Version 1.0 * Jeff Crankshaw */#ifndef TYPEDEFS_H#define TYPEDEFS_H#define FALSE 0#define TRUE 1typedef unsigned int WORD; /* 16bit data */typedef unsigned long DWORD; /* 3

2、2bit data */typedef volatile WORD * PORT;#define STR(x) #x#define OUTMAC(address,data) asm(” LDPK _”STR(data); asm(” OUT _”STR(data) ”,” STR(address)#define INMAC(address,data) asm(” LDPK _”STR(data); asm(” IN _”STR(data) ”,” STR(address)#define Int_Read(addr) * (int *) (addr)#define Int_Write(addr,

3、data) * (int *) (addr) = (data)#endif /* _TYPEDEFS */* File: C240.H * TMS320x240 Test Bed Code * Texas Instruments, Inc. * Copyright (c) 1996 Texas Instruments Inc. * 11/05/96 Version 1.0 * Jeff Crankshaw * * TMS320C240 Peripheral Register Addresses * */#ifndef c240_h#define c240_h#include ”typedefs

4、.h”/*/* definitions of I/O space macros */*/#define STR(x) #x#define OUTMAC(address,data) asm(” LDPK _”STR(data); asm(” OUT _”STR(data) ”,” STR(address)#define INMAC(address,data) asm(” LDPK _”STR(data); asm(” IN _”STR(data) ”,” STR(address)#define LED_LOC 000ch /* F240 EVM I/O space location for LE

5、Ds */*/* definitions of CPU core registers */*/#define IMR_REG ( PORT )0x0004 )#define IFR_REG ( PORT )0x0006 )/*/* External Memory Interface Registers */*/#define WSGR 0x0ffff/* Wait State Generator Register */*/* System Module Registers */*/#define SYSCR ( PORT )0x07018) /* System Module Control R

6、egister */#define SYSSR ( PORT )0x0701A) /* System Module Status Register */#define SYSIVR ( PORT )0x0701E) /* System Interrupt Vector Register */#define XINT1_CR ( PORT )0x07070) /* Int1 (type A) Control reg */#define NMI_CR ( PORT )0x07072) /* Non maskable Int (type A) Control reg */#define XINT2_

7、CR ( PORT )0x07078) /* Int2 (type C) Control reg */#define XINT3_CR ( PORT )0x0707A) /* Int3 (type C) Control reg */#define PDPINT_CR ( PORT )0x0742C) /* Power Drive Protection Int cntl reg */* System Interrupt Vector Register Address offsets */#define PHANTOM_INT_VECTOR 0x00#define NMI_INT_VECTOR 0

8、x02#define XINT1_INT_VECTOR 0x01#define XINT2_INT_VECTOR 0x11#define XINT3_INT_VECTOR 0x1f#define SPI_INT_VECTOR 0x05#define SCI_RX_INT_VECTOR 0x06#define SCI_TX_INT_VECTOR 0x07#define RTI_INT_VECTOR 0x10#define PDP_INT_VECTOR 0x20#define EV_CMP1_INT_VECTOR 0x21#define EV_CMP2_INT_VECTOR 0x22#define

9、 EV_CMP3_INT_VECTOR 0x23#define EV_SCMP1_INT_VECTOR 0x24#define EV_SCMP2_INT_VECTOR 0x25#define EV_SCMP3_INT_VECTOR 0x26#define EV_T1PER_INT_VECTOR 0x27#define EV_T1CMP_INT_VECTOR 0x28#define EV_T1UF_INT_VECTOR 0x29#define EV_T1OF_INT_VECTOR 0x2a#define EV_T2PER_INT_VECTOR 0x2b#define EV_T2CMP_INT_V

10、ECTOR 0x2c#define EV_T2UF_INT_VECTOR 0x2d#define EV_T2OF_INT_VECTOR 0x2e#define EV_T3PER_INT_VECTOR 0x2f#define EV_T3CMP_INT_VECTOR 0x30#define EV_T3UF_INT_VECTOR 0x31#define EV_T3OF_INT_VECTOR 0x32#define EV_CAP1_INT_VECTOR 0x33#define EV_CAP2_INT_VECTOR 0x34#define EV_CAP3_INT_VECTOR 0x35#define E

11、V_CAP4_INT_VECTOR 0x36#define AC2_INT_VECTOR 0x04/*/* Digital I/O Registers */*/#define OCRA ( PORT )0x07090) /* Output Control Reg A */#define OCRB ( PORT )0x07092) /* Output Control Reg B */#define PADATDIR ( PORT )0x07098) /* I/O port A Data & Direction reg. */#define PBDATDIR ( PORT )0x0709A) /*

12、 I/O port B Data & Direction reg. */#define PCDATDIR ( PORT )0x0709C) /* I/O port C Data & Direction reg. */*/* WatchDog(WD) / Real Time Int(RTI) / Phase Lock Loop(PLL) Registers */*/#define RTICNTR ( PORT )0x07021) /* RTI Counter reg */#define WDTCNTR ( PORT )0x07023) /* WD Counter reg */#define WD

13、TKEY ( PORT )0x07025) /* WD Key reg */#define RTICR ( PORT )0x07027) /* RTI Control reg */#define WDCR ( PORT )0x07029) /* WD Control reg */#define CKCR0 ( PORT )0x0702B) /* PLL control reg 1 */#define CKCR1 ( PORT )0x0702D) /* PLL control reg 2 */*/* AnalogtoDigital Converter(ADC) registers */*/#de

14、fine ADCTRL1 ( PORT )0x07032) /* ADC Control & Status reg */#define ADCTRL2 ( PORT )0x07034) /* ADC Configuration reg */#define ADCFIFO1 ( PORT )0x07036) /* ADC Channel 1 Result Data */#define ADCFIFO2 ( PORT )0x07038) /* ADC Channel 2 Result Data */*/* Serial Peripheral Interface (SPI) Registers */

15、*/#define SPICCR ( PORT )0x07040) /* SPI Config Control Reg */#define SPICTL ( PORT )0x07041) /* SPI Operation Control Reg */#define SPISTS ( PORT )0x07042) /* SPI Status Reg */#define SPIBRR ( PORT )0x07044) /* SPI Baud rate control reg */#define SPIEMU ( PORT )0x07046) /* SPI Emulation buffer reg

16、*/#define SPIBUF ( PORT )0x07047) /* SPI Serial Input buffer reg */#define SPIDAT ( PORT )0x07049) /* SPI Serial Data reg */#define SPIPC1 ( PORT )0x0704D) /* SPI Port control reg1 */#define SPIPC2 ( PORT )0x0704E) /* SPI Port control reg2 */#define SPIPRI ( PORT )0x0704F) /* SPI Priority control re

17、g */*/* Serial Communications Interface (SCI) Registers */*/#define SCICCR ( PORT )0x07050) /* SCI Comms Control Reg */#define SCICTL1 ( PORT )0x07051) /* SCI Control Reg 1 */#define SCIHBAUD ( PORT )0x07052) /* SCI Baud rate control */#define SCILBAUD ( PORT )0x07053) /* SCI Baud rate control */#de

18、fine SCICTL2 ( PORT )0x07054) /* SCI Control Reg 2 */#define SCIRXST ( PORT )0x07055) /* SCI Receive status reg */#define SCIRXEMU ( PORT )0x07056) /* SCI EMU data buffer */#define SCIRXBUF ( PORT )0x07057) /* SCI Receive data buffer */#define SCITXBUF ( PORT )0x07059) /* SCI Transmit data buffer */

19、#define SCIPC1 ( PORT )0x0705D) /* SCI Port control reg1 */#define SCIPC2 ( PORT )0x0705E) /* SCI Port control reg2 */#define SCIPRI ( PORT )0x0705F) /* SCI Priority control reg */*/* Event Manager (EV) Registers */*/#define GPTCON ( PORT )0x07400) /* General Timer Controls */#define T1CNT ( PORT )0

20、x07401) /* T1 Counter Register */#define T1CMP ( PORT )0x07402) /* T1 Compare Register */#define T1PER ( PORT )0x07403) /* T1 Period Register */#define T1CON ( PORT )0x07404) /* T1 Control Register */#define T2CNT ( PORT )0x07405) /* T2 Counter Register */#define T2CMP ( PORT )0x07406) /* T2 Compare

21、 Register */#define T2PER ( PORT )0x07407) /* T2 Period Register */#define T2CON ( PORT )0x07408) /* T2 Control Register */#define T3CNT ( PORT )0x07409) /* T3 Counter Register */#define T3CMP ( PORT )0x0740a) /* T3 Compare Register */#define T3PER ( PORT )0x0740b) /* T3 Period Register */#define T3

22、CON ( PORT )0x0740c) /* T3 Control Register */#define COMCON ( PORT )0x07411) /* Compare Unit Control */#define ACTR ( PORT )0x07413) /* Full Compare Unit Output Action Ctrl */#define SACTR ( PORT )0x07414) /* Simple Comp Unit Output Action Ctrl */#define DBTCON ( PORT )0x07415) /* Dead Band Timer C

23、ontrol */#define CMPR1 ( PORT )0x07417) /* Full Compare Channel 1 Threshold */#define CMPR2 ( PORT )0x07418) /* Full Compare Channel 2 Threshold */#define CMPR3 ( PORT )0x07419) /* Full Compare Channel 3 Threshold */#define SCMPR1 ( PORT )0x0741a) /* Simple Comp Channel 1 Threshold */#define SCMPR2

24、( PORT )0x0741b) /* Simple Comp Channel 2 Threshold */#define SCMPR3 ( PORT )0x0741c) /* Simple Comp Channel 3 Threshold */#define CAPCON ( PORT )0x07420) /* Capture Unit Control */#define CAPFIFO ( PORT )0x07422) /* FIFO14 Status Register */#define FIFO1 ( PORT )0x07423) /* Capture Channel 1 FIFO T

25、op */#define FIFO2 ( PORT )0x07424) /* Capture Channel 2 FIFO Top */#define FIFO3 ( PORT )0x07425) /* Capture Channel 3 FIFO Top */#define FIFO4 ( PORT )0x07426) /* Capture Channel 4 FIFO Top */#define IMRA ( PORT )0x0742c) /* Group A Interrupt Mask Register */#define IMRB ( PORT )0x0742d) /* Group

26、B Interrupt Mask Register */#define IMRC ( PORT )0x0742e) /* Group C Interrupt Mask Register */#define IFRA ( PORT )0x0742f) /* Group A Interrupt Flag Register */#define IFRB ( PORT )0x07430) /* Group B Interrupt Flag Register */#define IFRC ( PORT )0x07431) /* Group C Interrupt Flag Register */#def

27、ine IVRA ( PORT )0x07432) /* Group A Int. Vector Offset Register */#define IVRB ( PORT )0x07433) /* Group B Int. Vector Offset Register */#define IVRC ( PORT )0x07434) /* Group C Int. Vector Offset Register */#endif/*+*/* */*File: CONSTANT.H */*Target Processor: TMS320F240 */*Compiler Version: */*As

28、sembler Version: */*Created: 10/1/97 */* */*/* Constants for the SRM control algorithms */*+*/*/* clock frequencies and time related constants */*/#define PWM_FREQ 0 /* PWM frequency (Hz) */#define SYSCLK_FREQ /* DSP clock frequency (Hz) */#define CPU_INT_FREQ 5000 /* timer ISR frequency (Hz) */#def

29、ine ONE_HALF_SECOND (CPU_INT_FREQ/2)/* */* current loop algorithm constants */* */#define ILOOP_GAIN 22 /* current loop gain: */* (Q3: gain = 2.75) */#define ILIMIT 1023 /* current limit: (1023 bits = */* 5 V x 0.855 A/V = 4.273 A) */#define MAXIMUM_DUTYRATIO 999 /* limit on the PWM duty cycle: */*

30、100 % = */* (SYSCLK_FREQ/PWM_FREQ 1) */*/* velocity loop algorithm constants */*/#define INTEGRAL_LIMIT 2793472 /* integrator limit */#define KI 3 /* (Q13*1000): Ki = 0.366 */#define KP 1 /* Q1: Kp = 0.5 */*/* position & velocity estimation algorithm constants */*/#define K_POSITION_EST 1432#define

31、K1_VELOCITY_EST 0#define K2_VELOCITY_EST 62500#define ALPHA 7 /* Q3: alpha = 0.875 */#define ONE_MINUS_ALPHA 1 /* Q3: 1alpha = 0.125 */*/* motor geometry related */*/#define NR 8 /* number of rotor poles */#define NUMBER_OF_PHASES 3/*/* Electrical Angles: 2*pi (rad) = 65535 */*/#define PIBYSIX_16 54

32、61#define PIBYFOUR_16 8192#define PIBYTHREE_16 10923#define TWOPIBYTHREE_16 21845#define THREEPIBYFOUR_16 24576#define FIVEPIBYSIX_16 27307#define PI_16 32768#define FOURPIBYTHREE_16 43690#define FIVEPIBYTHREE_16 54613#define TWOPI_16 65535/*+*/* */*File: SRM.H */*Target Processor: TMS320F240 */*Com

33、piler Version: */*Assembler Version: */*Created: 10/1/97 */* */*/* Variable declarations for the SRM control algorithm */*+*/#include ”constant.h”#include ”typedefs.h”/*/* position estimation state machine data structure */*/typedef struct int state;WORD position;int direction; state_machine;/*/* SR

34、M variables data structure: */*/*a2d_chani sets which A/D pin is used for the ith phase current/*desiredTorque torque command (output of velocity loop)/*integral_speed_error velocity loop integrator for PI compensator/*iDesi current command for the ith phase/*capture_edgei timer #2 count value at th

35、e occurence of/* the most recent ith capture/*capture_deltai2 change in the timer #2 count value between/* the occurences of the ith capture events. The two most/* recent events are stored./*delta_count change in the software counter of the timer ISR/* between occurences of any capture event./*wEst_

36、10xrpm shaft velocity estimate (units of rpm*10)/* wDes_10xrpm desired shaft velocity (units of rpm*10)/* activei flag indicating whether the ith phase is ON (1 = on)/* iFBi current feedback measurement for the ith phase/* dutyRatioi commanded % duty ratio for the highside FET of/* the ith phase/*po

37、sition shaft position estimate (electrical degrees)/* scaled: 2*pi (rad) = 65535 bits/*position_state position state of the SRM (defined by optocouplers)/*shaft_direction direction which the shaft is rotating./*trans_lut74 the position state machine/*position_initial_guess7 initial position guess, b

38、ased on state/*dp_remainder 16bit remainder used in the position estimation alg/*last_capture the most recent capture to occur/*/typedef struct int a2d_chanNUMBER_OF_PHASES;int desiredTorque;long integral_speed_error; WORD iDesNUMBER_OF_PHASES;WORD capture_edgeNUMBER_OF_PHASES;WORD capture_deltaNUMB

39、ER_OF_PHASES2;WORD delta_count;int wEst_10xrpm; int wDes_10xrpm; int activeNUMBER_OF_PHASES; WORD iFBNUMBER_OF_PHASES; int dutyRatioNUMBER_OF_PHASES;WORD position; int position_state;int shaft_direction;state_machine trans_lut74;WORD position_initial_guess7;long dp_remainder;int last_capture; anSRM_

40、struct;/*/*PROTOTYPE DEFINITIONS */*/void eventmgr_init();void initializeSRM(anSRM_struct *anSRM);void Commutation_Algorithm( anSRM_struct *anSRM);void Time_Update_Position(anSRM_struct *anSRM);void velocityController( anSRM_struct *anSRM);void currentController( anSRM_struct *anSRM);void computePos

41、itionAndVelocity(anSRM_struct *anSRM);void Msmt_Update_Velocity(anSRM_struct *anSRM, int mode);void Msmt_Update_Position(anSRM_struct *anSRM);void switch_lowside(int phaseactive);void switch_mux(int adc1, int adc2);void disable_interrupts();void dsp_setup();void initialize_counters_and_flags();void

42、enable_interrupts();void start_background();void check_for_stall();/*+/*/*File: MAIN.C/*Target Processor: TMS320F240/*Compiler Version: 6.6/*Assembler Version: 6.6/*Created: 10/31/97/*/*+/* This file is the main program for the control of an SRM drive with a/*position sensor/*+*/*/*INCLUDE FILES */*

43、/#include ”c240.h”#include ”srm.h”/*/*GLOBAL VARIABLE DECLARATIONS */*/int count;int slice;int old_count;int Update_Velocity;int Toggle_LED;int Msmt_Update;anSRM_struct SRM;int LEDvalue;/*/*MAIN PROGRAM */*/void main() disable_interrupts();dsp_setup();initializeSRM(&SRM);eventmgr_init();initialize_c

44、ounters_and_flags();enable_interrupts();start_background();/*+ */*BACKGROUND TASKS */* */*Upon completion of the required initialization, the main/*program starts the background task. The background is/*simply an infinite loop. Time critical motor control/*processing is done via interrupt service routines and lower/*priority processing is done in the background, when they/*are needed. Two background operations are defined:/*/*1) Update_Velocity when a capture interrupt occurs,/* the ISR stores the capture data and then int

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 七年级数学:平面直角坐标系中不规则图形面积的计算课件

- 地理环境的差异性课件——曲靖市麒麟区第一中学-郭金涛1

- 高考数学文科一轮复习(北京卷B)ppt课件102双曲线及其性质

- 剖宫产瘢痕妊娠课件

- 七年级《走进初中-享受学习》主题班会ppt课件

- 2020高端楼盘营销渠道拓客课件

- 七年级道德与法治下册第四单元走进法治天地第九课法律在我们身边第1框生活需要法律ppt课件2新人教版

- 七年级生物血管和心脏课件

- 高考数学一轮复习讲义-第一章-1.2-命题及其关系、充分条件与必要条件ppt课件

- 2021公司元旦跨年预售活动方案课件

- 高考数学一轮复习-第十八章-第2讲-极坐标与参数方程ppt课件-文

- 高考数学一轮复习-第二章第四节-幂函数与二次函数ppt课件-理-(广东专用)

- 北欧家具设计课件

- 高考数学一轮复习5.35特殊数列求和ppt课件理

- 高考数学浙江专用二轮培优ppt课件专题六第1讲排列组合二项式定理