8位CPU的设计,VHDL语言,综合性实验实验报告

8位CPU的设计,VHDL语言,综合性实验实验报告

《8位CPU的设计,VHDL语言,综合性实验实验报告》由会员分享,可在线阅读,更多相关《8位CPU的设计,VHDL语言,综合性实验实验报告(44页珍藏版)》请在装配图网上搜索。

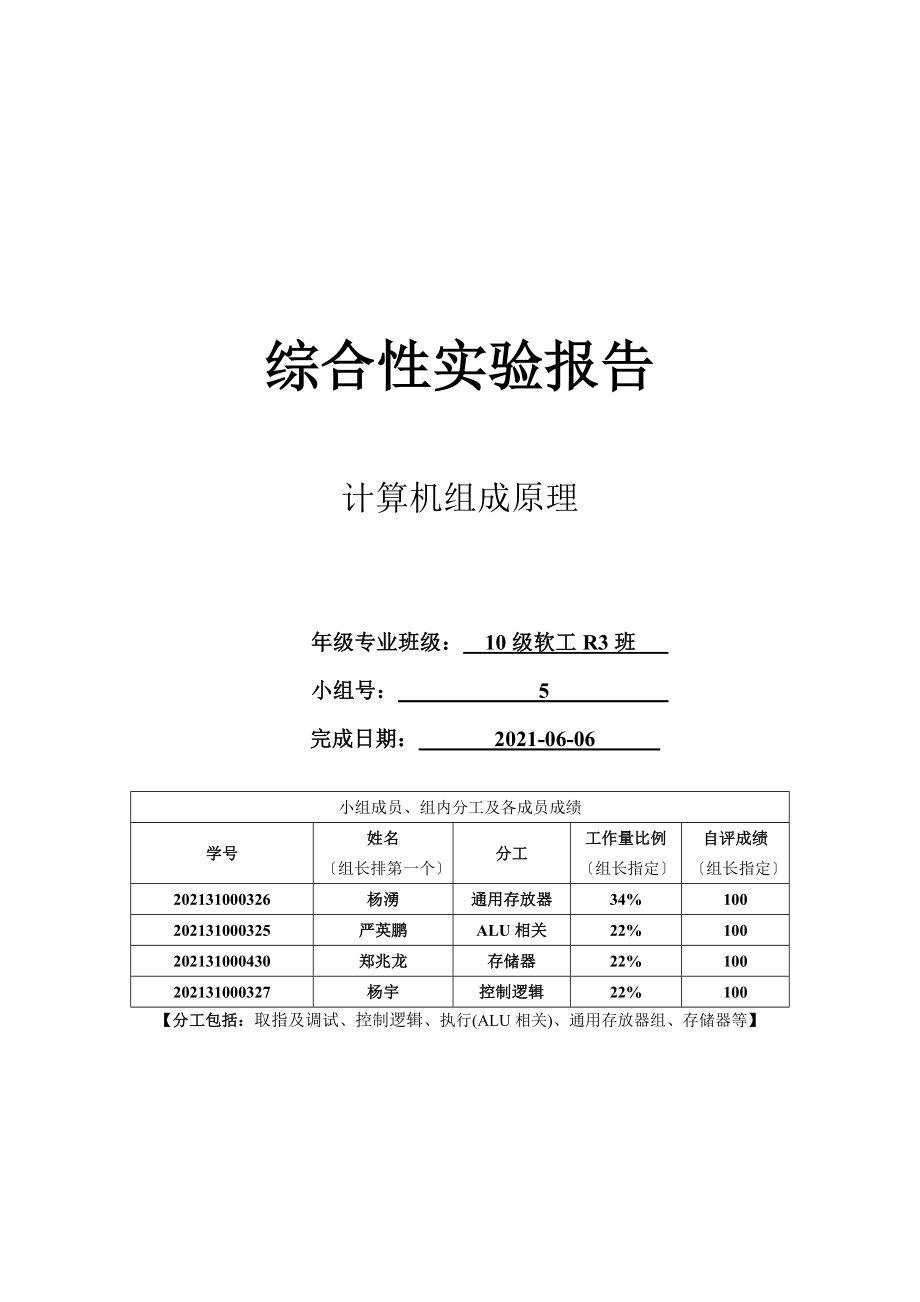

1、综合性实验报告计算机组成原理年级专业班级: 10级软工R3班 小组号: 5 完成日期: 2021-06-06 小组成员、组内分工及各成员成绩学号姓名组长排第一个分工工作量比例组长指定自评成绩组长指定202131000326杨湧通用存放器34%100202131000325严英鹏ALU相关22%100202131000430郑兆龙存储器22%100202131000327杨宇控制逻辑22%100【分工包括:取指及调试、控制逻辑、执行(ALU相关)、通用存放器组、存储器等】一实验类型:验证性+设计性二实验类别:综合性专业根底实验三实验学时数:8学时四实验目的理解和验证参考代码,并在其根底上,通过适

2、当改造,尝试设计一个简单的CPU,并测试其结果。五实验内容设计一个能验证计算机CPU工作原理的实验系统,包括取指局部、指令译码局部、执行局部、通用存放器组以及存储器,并测试其结果。六实验要求 根本目标:缩小到8位的数据通路,也即是4位OP和4位的地址码。参考代码是16位数据通路,也即8位OP和8位的地址码)学生按照实验要求,在实验平台上实现具有存储与运算功能的计算机系统,并能通过测试,以验证其正确性。具体要求如下:1取指及调试(组长兼任)。熟悉指令取指过程,并把16位的局部改为8位。使用DebugController和系统中的调试模块(,)。2熟悉电原理图的连接,以通用存放器组局部为例。实现上

3、,用实验4所用的简单通用存放器组4个存放器+1个2-4译码器+2个4选1多路开关设计方法,替代参考代码中的通用存放器组局部。3学习和掌握控制逻辑。设计一套指令集可在原参考代码指令集的根底上做删减,从中选取16条根本的指令,并修改控制器中指令集的译码局部。4执行部件,ALU的改造。可在原参考代码的根底上,改变某些运算功能的实现方式,比方加、减、增1、减1等算术运算。实现上,原参考代码采用了最少编码量的“+、“-号实现。可以改用通过port map语句调用系统自带的加法器,也可以进一步自己编写加法器,然后用port map语句调用。5存储器局部的参加。原参考代码采用的带外部存储器的模式。实现上,可

4、以在实验3的根底上,设计一个适合加到本CPU系统的存储器局部,通过与原参考代码系统连接外带存储器的数据线、控制线和地址线相连接。此局部设计中,存储器的指令置入是一个难点。可以考虑简单点的作为只读模式把指令写死在存储器中可用于验证指令的执行;或者考虑在reset的那一拍里,实现存储器中待指令的置入。存储器模块单独调试可行后再加到系统上。七实验设备TEC-CA组成原理实验箱。八实验课承当单位:信息学院九总结构图组长负责组织填写十指令集组长负责组织填写参考实验大纲中的例如,结合各小组自己的设计指令系统总体说明 (p9-11页)(1) 指令格式分类按指令字长和操作数不同: 单字单操作数指令7 43 2

5、1 0 OPCODE DEST_REG 00 OPCODE OFFSET 包括:DEC,INC,SHL,SHR,JR,JRC,JRNC,JRZ,JRNZ,JRS,JRNS 单字双操作数指令7 43 21 0 OPCODE DEST_REG SOUR_REG 包括:ADD,SUB,AND,CMP,XOR,TEST,OR,MVRR,ADC,SBB,LDRR,STRR 单字无操作数指令7 43 21 0 OPCODE 00 00 包括:CLC,STC 双字单操作数指令7 43 21 0 OPCODE 00 00 ADR 包括:JMPA 双字双操作数指令7 43 21 0 OPCODE DEST_RE

6、G 00 DATA 包括:MVRD(2) 指令的分组及节拍:由于没有中断操作,本机指令的执行步骤可概括如下:读取指令:地址存放器-指令地址,修改PC内容使其指向下一条将要执行的指令; 读内存,指令存放器-读出的内容。分析指令执行指令:通用存放器之间的运算或传送,可1步完成; 读写内存,通常要两步完成。根据指令的执行步骤不同,可以把全部指令分为A、B两组。其中A组指令完成的是通用存放器之间的数据运算或传送,或其他一些特殊操作,在取指之后可一步完成,包括:ADD、SUB、AND、XOR、OR、INC、DEC、CMP、ADC、JR、JRC、JRNC;B组指令完成的是一次内存读写操作,在取指之后可两步

7、完成,包括:JMPA,LDRR,STRR,MVRD。在编码的时候以指令操作码的最高位来区分 A、B组指令,0为A组指令,1为B组指令。在控制器方面我们选用了组合逻辑控制器方案。使用节拍来标记每条指令的执行步骤。由指令而定,在我们的系统中不同的执行步骤只有5个,故使用3位节拍就足够了。000AR-PC,PC-PC+1001读写内存传送地址AR-地址读内存,IR-读出内容 B组指令 101 111A组指令011存放器之间的数据运算或传送(3) 指令汇总表:节拍指令编码SciSSTI7I6I5I4I3I2I1I0/WRREC注释000011110100000101AR-PC,PC-PC+100100

8、1100000000110IR-MEM011ADD0000000001000000100DR-DR+SRSUB0001000001000001100DR-DR-SRAND0010000001000010100DR-DR and SRXOR0011000001000100100DR-DR xor SROR0100000001000011100DR-DR or SRINC0101010001010000100DR-DR+1DEC 0110010001010001100DR-DR-1CMP0111000000000001100DR-SRADC1000100001000000100DR-DR+SR+C

9、JR1001001110011000100PC-OFFSET+PCJRC10100011C0011000100PC-OFFSET+PCJRNC10110011/C0011000100PC-OFFSET+PC101JMPA1100011110100000101AR-PC,PC-PC+1MVRD1101011110100000101AR-PC,PC-PC+1LDRR1110001100001000111AR-SRSTRR1111001100010000111AR-DR111JMPA1100001110101000100PC-MEMMVRD1101001101101000100DR-MEMLDRR1

10、110001101101000100DR-MEMSTRR1111001100001000000MEM内存控制器从内存中读取指令-内存控制器把读取到的指令送上数据总线-CPU从数据总线上读到指令的二进制码-CPU执行指令2. 使用DebugController调试1) 将实验台背后的9针插座和PC机的一个串行口用RS232通讯电缆连接,将实验小板上的下载插座和PC机的并行口用下载电缆连接。翻开实验台电源。2) 启动DebugController程序。启动程序后,程序自动扫描可用串口。程序会向COM1COM4顺序发送一个测试命令,等待测试命令的会送命令,如果X号串口不可用,那么会在提示信息窗口显示

11、“COMx not found or cannot open. Check cable or hardware!;如果x号串口可用但是测试命令没有送回,那么会显示“COMx timed out, current operation aborted You must recondig COM!;如果x号串口可用而且测试命令得到了会送,会显示“Auto scan linked TEC-CA on COMx Successfully。3) 翻开位汇编代码文件 和翻开编译规那么文件 。4) 点击Build菜单中的Compile Code或者点击工具栏中的,将伪汇编文件编译为16进制文件。5) 将实验平

12、台的调试模式设置为FPGA-CPU附加外部RAM运行模式REGSEL=0,CLKSEL=1,FDSEL=1过着单片机控制FPGA-CPU调试运行模式REGSEL=1,CLKSEL=0,FDSEL=1。6) 点击Build菜单中的Upload BIN或者点击工具栏中的,将16进制代码文件上传到存储器RAM中。传完之后在Log Window中会有提示信息。7) 在使用Quartus软件将CPU设计经编译、连接和适配后,将它下载到FPGA中,在FPGA中生成一个物理CPU。将实验平台上的调试模式设置为单片机控制FPGA-CPU调试运行模式REGSEL=1,CLKSEL=0,FDSEL=1,就可以通过

13、DebugController对FPGA-CPU进行调试了。8) 点击Debug菜单中的Begin Debug,或者点击工具栏中的开始调试。9) 可以使用Debug调试菜单中的子菜单,也可以使用工具栏的,一次代表Half Cycle,One Cycle,Run To BP,Reset和End Debug。10) 特别之处,设置断点是在Debug Window相应的行上鼠标双击,取消断点也是相应的鼠标双击。由于单片机指令本身只支持单断点,所以程序中也只能设置单个断点。11) 结束调试。结束调试前如果要查看实验台上存储器的内容,请使用Download RAM从存储器读二进制文件命令。点击Debug

14、菜单中的End Debug或者工具栏上的,结束Debug模式。12) 注意:在结束Debug之后,如果想重新进入Debug模式,必须手动选择串口。有改动过的或者新增的.bsf图、vhd文件内容,以及相关电原理图截图、用于说明的表格、用于说明的示意图等。加注释,特别是在参考材料的源代码根底上改动之处,用蓝色标出。可以局部参照参考材料的文档写法。特别注意:如果没被抽中去演示,那么主要根据分工所对应的这局部设计的撰写的内容评分,因此要尽量详细地介绍你的工作。2. 控制逻辑0是否加到最后整组的系统中 如果答复为否,可跳过第1和2问。是1修改后是否编译通过指加到整个小组的系统里是2修改后是否可运行指加到

15、整个小组的系统里是3概要描述(2-3句话描述你的工作)主要是选择了16条指令并对其进行修改,并且对controller和timer的代码进行修改。4相关的源代码、电原理图和其它说明表格。有改动过的或者新增的.bsf图、vhd文件内容,以及相关电原理图截图、用于说明的表格、用于说明的示意图等。加注释,特别是在参考材料的源代码根底上改动之处,用蓝色标出。可以局部参照参考材料的文档写法。特别注意:如果没被抽中去演示,那么主要根据分工所对应的这局部设计的撰写的内容评分,因此要尽量详细地介绍你的工作。Controller代码library ieee;use ieee.std_logic_1164.all

16、;entity controller is -实体描述port( timer: in std_logic_vector(2 downto 0); -节拍 instruction: in std_logic_vector(7 downto 0); -指令内容 c,z,v,s: in std_logic; -标志位 dest_reg,sour_reg: out std_logic_vector(1 downto 0); -目的和源存放器的选择信号 offset: out std_logic_vector(3 downto 0); -偏移地址 sst,sci,rec: out std_logic_v

17、ector(1 downto 0); -输出各个控制信号 alu_func,alu_in_sel: out std_logic_vector(2 downto 0); en_reg,en_pc,wr: out std_logic);end controller;architecture behave of controller isbeginprocess(timer,instruction,c,z,v,s)variable temp1,temp2 : std_logic_vector(3 downto 0) ;variable temp3,temp4 : std_logic_vector(1

18、 downto 0) ;variable alu_out_sel: std_logic_vector(1 downto 0);beginfor I in 3 downto 0 looptemp1(I):=instruction(I+4); -暂存指令高4位temp2(I):=instruction(I); -暂存指令低4位end loop;for I in 1 downto 0 looptemp3(I):=instruction(I+2); -暂存低4位中的高2位temp4(I):=instruction(I); -暂存低4位中的低2位end loop;case timer iswhen 10

19、0= -初始状态dest_reg=00;sour_reg=00;offset=0000;sci=00;sst=11;alu_out_sel:=00;alu_in_sel=000;alu_func=000;wr=1;rec -读取指令第一拍dest_reg=00;sour_reg=00;offset=0000;sci=01;sst=11;alu_out_sel:=10;alu_in_sel=100;alu_func=000;wr=1;rec -读内存,放到指令存放器dest_reg=00;sour_reg=00;offset=0000;sci=00;sst=11;alu_out_sel:=00;

20、alu_in_sel=000;alu_func=000;wr=1;rec -A组指令wr=1;rec -ADDdest_reg=temp3;sour_reg=temp4;offset=0000;sci=00;sst=00;alu_out_sel:=01;alu_in_sel=000;alu_func -SUBdest_reg=temp3;sour_reg=temp4;offset=0000;sci=00;sst=00;alu_out_sel:=01;alu_in_sel=000;alu_func -ANDdest_reg=temp3;sour_reg=temp4;offset=0000;sci

21、=00;sst=00;alu_out_sel:=01;alu_in_sel=000;alu_func -XORdest_reg=temp3;sour_reg=temp4;offset=0000;sci=00;sst=00;alu_out_sel:=01;alu_in_sel=000;alu_func -ORdest_reg=temp3;sour_reg=temp4;offset=0000;sci=00;sst=00;alu_out_sel:=01;alu_in_sel=000;alu_func -INCdest_reg=temp3;sour_reg=temp4;offset=0000;sci=

22、01;sst=00;alu_out_sel:=01;alu_in_sel=010;alu_func -DECdest_reg=temp3;sour_reg=temp4;offset=0000;sci=01;sst=00;alu_out_sel:=01;alu_in_sel=010;alu_func -CMPdest_reg=temp3;sour_reg=temp4;offset=0000;sci=00;sst=00;alu_out_sel:=00;alu_in_sel=000;alu_func -ADCdest_reg=temp3;sour_reg=temp4;offset=0000;sci=

23、10;sst=00;alu_out_sel:=01;alu_in_sel=000;alu_func -JRdest_reg=00;sour_reg=00;offset=temp2;sci=00;sst=11;alu_out_sel:=10;alu_in_sel=011;alu_func -JRCdest_reg=00;sour_reg=00;offset=temp2;sci=00;sst=11;alu_out_sel:=c&0;alu_in_sel=011;alu_func -JRNCdest_reg=00;sour_reg=00;offset=temp2;sci=00;sst=11;alu_

24、out_sel:=(not c)&0;alu_in_sel=011;alu_funcnull;end case;when 101= -B组指令alu_func=000;wr=1;sst=11;dest_reg=temp3;sour_reg=temp4;offset -读取双字指令的后一半(JMPA MVRD)sci=01;alu_out_sel:=10;alu_in_sel=100;rec -目的地址送地址存放器 LDRRsci=00;alu_out_sel:=00;alu_in_sel=001;recsci=00;alu_out_sel:=00;alu_in_sel=010;recnull;

25、end case;when 111= -读写内存dest_reg=temp3;sour_reg=temp4;offset=0000;sci=00;sst=11;alu_func=000;rec -LDRR MVRDalu_out_sel:=01;alu_in_sel=101;wr -JMPAalu_out_sel:=10;alu_in_sel=101;wr -STRRalu_out_sel:=00;alu_in_sel=001;wrnull;end case;when others=null;end case;en_reg=alu_out_sel(0);en_pc=alu_out_sel(1)

26、;end process;end behave;controller截图Timer代码library ieee;use ieee.std_logic_1164.all;entity timer is port( clk : in std_logic; reset : in std_logic; ins : in std_logic_vector(7 downto 0); output : out std_logic_vector(2 downto 0);end timer;architecture behave of timer istype state_type is(s0,s1,s2,s3

27、,s4,s5);signal state:state_type;beginprocess(clk,reset,ins)beginif reset=0 then statestatestateif (ins(7) = 1 and ins(6) = 1) then -根据头两位是11选择B组指令state=s4;else statestatestatestateoutputoutputoutputoutputoutputoutput=111;end case;end process;end behave;Timer截图3. 执行(ALU相关)0是否加到最后整组的系统中如果答复为否,可跳过第1和2问

28、。答:是。1修改后是否编译通过指加到整个小组的系统里答:是。编译通过,0个错误,0个警告。2修改后是否可运行指加到整个小组的系统里答:可以运行。3概要描述(2-3句话描述你的工作) 答:在将16位cpu改造成8位cpu小组实验中,我的主要工作是执行部件,ALU的改造。将cpu中的16位alu器件改为8位alu器件。并且改变alu中加减法的实现方式,简单的说,就是去掉alu代码中的加减号,用port map语句调用自己设计的加法器来进行加减法运算。另外还要将16位数据选择器BUS_MUX也改成8位通路,以及将组合逻辑器件器件T1也改成8位通路,并且参加了小组的整个程序相关局部的调式。4相关的源代

29、码、电原理图和其它说明表格。有改动过的或者新增的.bsf图、vhd文件内容,以及相关电原理图截图、用于说明的表格、用于说明的示意图等。加注释,特别是在参考材料的源代码根底上改动之处,用蓝色标出。可以局部参照参考材料的文档写法。特别注意:如果没被抽中去演示,那么主要根据分工所对应的这局部设计的撰写的内容评分,因此要尽量详细地介绍你的工作。1、ALU:组合逻辑部件,对两个16位的输入及进位输入Cin可进行由3位控制信号控制的如下操作:I2I1I0功能000A+B+Cin001A-B-Cin010A与B011A或B100A异或B101B 左移110B右移由Quartus生成的.bsf图如下:一位fa

30、8位加法器 Alu改造后的VHDL语言的行为描述如下,下面为alu.vhd文件里面的内容:说明:用绿色说明的文字表示是相应的注释,用绿色说明的代码为原先的局部代码即是要修改或是要取代的代码,用蓝色外表的代码为修改的或是自行增加的代码,用加粗局部的文字为参考原来参考材料报告的局部内容。-自行设计的1位fa加法器-library ieee;use ieee.std_logic_1164.all;-定义一个名为fa的实体-entity fa isport(a,b,ci : in std_logic; s,co : out std_logic);end fa;architecture b_fa of

31、fa isbegin s=a xor b xor ci; co=(a xor b) and ci) or (a and b);-一位加法过程end b_fa;-自行设计的8位adder加法器-library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder8bit isport( a,b : in std_logic_vector(7 downto 0); s : out std_logic_vector(7 downto 0); ci : in std_logic);end adder8

32、bit;-定义实体architecture structure of adder8bit is -结构体定义,里面可以对signal名、component、常量进行定义component faport(a,b,ci : in std_logic; s,co : out std_logic);end component;-元件定义语句,把实体的内容搬上去,说明要引用的元件signal s_temp, c : std_logic_vector(7 downto 0); -定义信号,结果过程变量s_temp, 进位C beginf0: fa port map( a(0),b(0),ci,s_temp

33、(0),c(0) ); -最低位调用port map语句相加 f1_7: for i in 1 to 7 generate -其他7位分别用循环体相加 fm: fa port map( a(i),b(i),c(i-1),s_temp(i),c(i) ); end generate f1_7; s =s_temp;end structure;-alu-library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity alu isport(cin:

34、in std_logic;-alu_a,alu_b:in std_logic_vector(15 downto 0);原来的16位。 a,b:in std_logic_vector(7 downto 0); alu_func:in std_logic_vector(2 downto 0); alu_out:out std_logic_vector(7 downto 0); c,z,v,s:out std_logic);end alu;architecture behave of alu is -ALU行为描述-定义4组下面进程语句要用到的信号,每组信号用于相应的两位相加减赋值。说明:信号的定义

35、必须在进程之外说明-signal a_in : std_logic_vector(7 downto 0); -操作数 a ,过程变量 signal b_in : std_logic_vector(7 downto 0); -操作数 b , 过程变量 signal c_in : std_logic; -最低位进位 ,过程变量signal result_add8 : std_logic_vector(7 downto 0); -输出结果 ,过程变量 -signal a_in_1:std_logic_vector(7 downto 0); -操作数 a ,过程变量signal b_in_1 : st

36、d_logic_vector(7 downto 0); -操作数 b ,过程变量 signal c_in_1 : std_logic; -最低位进位, 过程变量signal result_add8_1 : std_logic_vector(7 downto 0); -输出结果,过程变量-signal a_in_2 : std_logic_vector(7 downto 0); -操作数 a ,过程变量 signal b_in_2 : std_logic_vector(7 downto 0); -操作数 b ,过程变量 signal c_in_2 : std_logic; -最低位进位 ,过程变

37、量 signal result_add8_2 : std_logic_vector(7 downto 0); -输出结果,过程变量- signal a_in_3 : std_logic_vector(7 downto 0); -操作数 a ,过程变量 signal b_in_3 : std_logic_vector(7 downto 0); -操作数 b ,过程变量 signal c_in_3 : std_logic; -最低位进位 ,过程变量 signal result_add8_3 : std_logic_vector(7 downto 0); -输出结果 ,过程变量- signal te

38、mp1 : std_logic_vector(7 downto 0); -过程变量,一般用于存放低位进位-component adder8bit is -8位加法器,对需要调用的组件进行声明 port(a,b : in std_logic_vector(7 downto 0); s : out std_logic_vector(7 downto 0); ci : in std_logic); end component;begin-进程开始之前进行位扩展- temp1 = 0000000&cin; -temp2 := alu_b+alu_a+cin或temp2 := alu_b-alu_a-t

39、emp1- -并且进行加减法统一处理,根据式子,有两组信号来处理- a_in=b;-根据相加的格式做相应位置的调整,并且对相应的信号根据使用的功能不同进行赋值 b_in=not a when alu_func=001 else a;- -做减法时b的位置要求反 c_in=1 when alu_func=001 else -做减法或者减1时,最低位置为1 cin; f_add: adder8bit port map( a_in,b_in,result_add8,c_in);-元件例话语句,标号名要唯一,用port map语句调用8位加法器,并且port map语句只能在进程之外调用。 - -a_

40、in_1=result_add8;b_in_1=not temp1 when alu_func=001 else temp1;c_in_1=1 when alu_func=001 else cin;f_add_1: adder8bit port map( a_in_1,b_in_1,result_add8_1,c_in_1); -元件例化语句,标号名要唯一,用port map语句调用8位加法器,并且port map语句只能在进程之外调用。 -temp3 := 11111111-alu_b-temp1- -需要两组信号来处理-a_in_2 = 11111111;b_in_2 = not b wh

41、en alu_func=000 else b; -做减法时b要求反 c_in_2 = 1 when alu_func=000 else cin;-做减法或者减1时,最低位置为1 f_add_2: adder8bit port map( a_in_2,b_in_2,result_add8_2,c_in_2); -元件例话语句,标号名要唯一,用port map语句调用8位加法器,并且port map语句只能在进程之外调用。-a_in_3 = result_add8_2;b_in_3 = not temp1 when alu_func=001 else -做减法时b要求反 temp1; c_in_3 =

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。