设计示例432位先行进位加法器的设计

设计示例432位先行进位加法器的设计

《设计示例432位先行进位加法器的设计》由会员分享,可在线阅读,更多相关《设计示例432位先行进位加法器的设计(5页珍藏版)》请在装配图网上搜索。

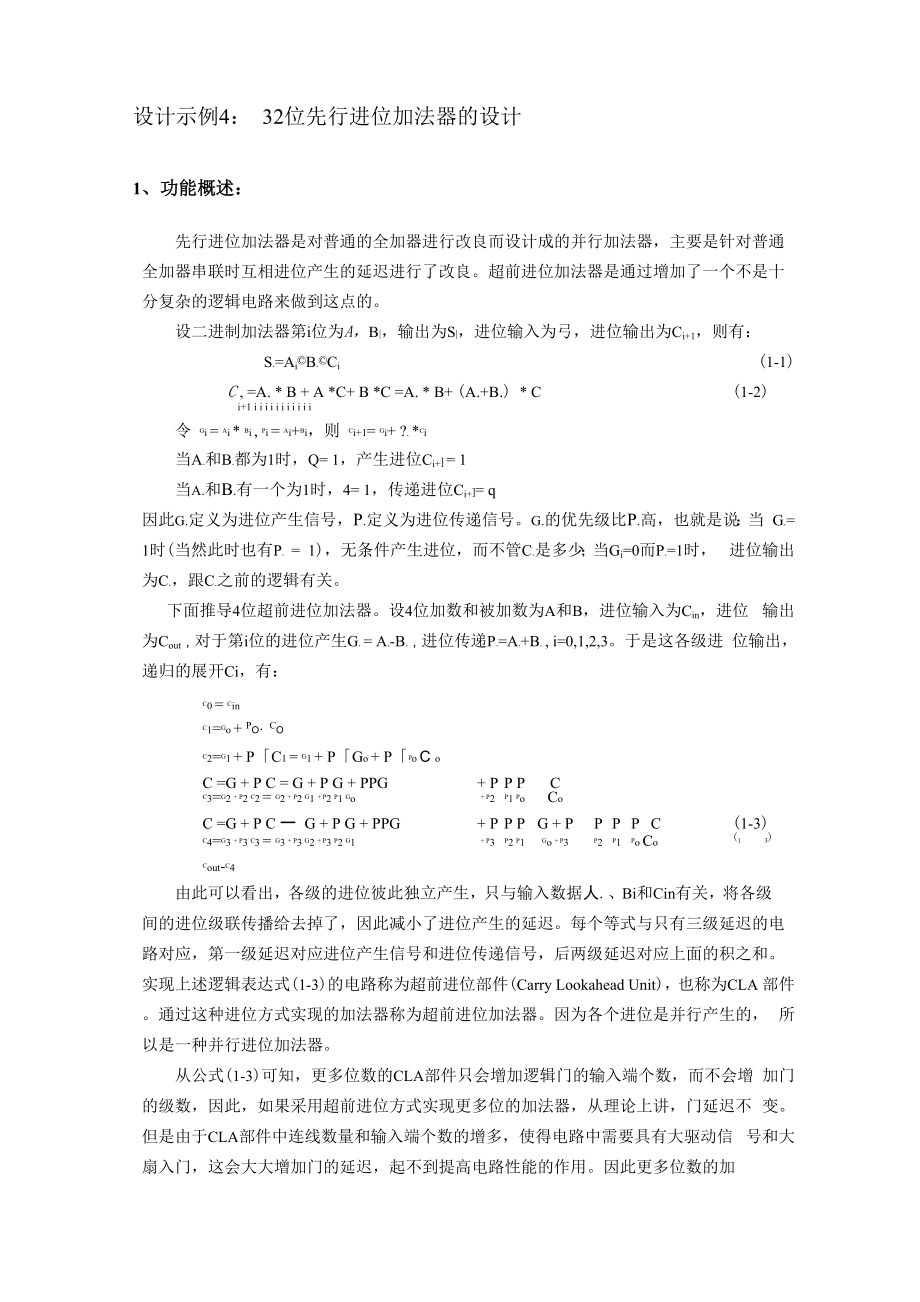

1、设计示例4: 32位先行进位加法器的设计1、功能概述:先行进位加法器是对普通的全加器进行改良而设计成的并行加法器,主要是针对普通 全加器串联时互相进位产生的延迟进行了改良。超前进位加法器是通过增加了一个不是十 分复杂的逻辑电路来做到这点的。设二进制加法器第i位为A,B|,输出为S|,进位输入为弓,进位输出为Ci+1,则有:S.=AiB.Ci(1-1)C , =A. * B + A *C+ B *C =A. * B+ (A.+B.) * C(1-2)i+1 i i i i i i i i i i i令 Gi = Ai * Bi , Pi = Ai+Bi,则 Ci+1= Gi+ ?. *Ci当A.

2、和B.都为1时,Q= 1,产生进位Ci+ = 1当a.和B.有一个为1时,4= 1,传递进位Ci+= q因此g.定义为进位产生信号,P.定义为进位传递信号。g.的优先级比P.高,也就是说:当 G.= 1时(当然此时也有P. = 1),无条件产生进位,而不管C.是多少;当Gi=0而P.=1时, 进位输出为C.,跟C.之前的逻辑有关。下面推导4位超前进位加法器。设4位加数和被加数为A和B,进位输入为Cin,进位 输出为Cout,对于第i位的进位产生G. = A.-B.,进位传递P.=A.+B. , i=0,1,2,3。于是这各级进 位输出,递归的展开Ci,有:C0 = CinC1=Go + PoC

3、oC2=G1 + PC1 = G1 + PGo + Ppo C oC =G + P C = G + P G + PPG+ PP PCC3=G2 + P2 C2 = G2 + P2 G1 + P2 P1 Go+ P2P1 PoCoC =G + P C 一 G + P G + PPG+ PP PG + PPPPC(1-3)C4=G3 + P3 C3 = G3 + P3 G2 + P3 P2 G1+ P3P2 P1Go + P3P2P1Po Co(13)Cout-C4由此可以看出,各级的进位彼此独立产生,只与输入数据人.、Bi和Cin有关,将各级 间的进位级联传播给去掉了,因此减小了进位产生的延迟。

4、每个等式与只有三级延迟的电 路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。 实现上述逻辑表达式(1-3)的电路称为超前进位部件(Carry Lookahead Unit),也称为CLA 部件。通过这种进位方式实现的加法器称为超前进位加法器。因为各个进位是并行产生的, 所以是一种并行进位加法器。从公式(1-3)可知,更多位数的CLA部件只会增加逻辑门的输入端个数,而不会增 加门的级数,因此,如果采用超前进位方式实现更多位的加法器,从理论上讲,门延迟不 变。但是由于CLA部件中连线数量和输入端个数的增多,使得电路中需要具有大驱动信 号和大扇入门,这会大大增加门的延迟

5、,起不到提高电路性能的作用。因此更多位数的加法器可通过4位CLA部件和4位超前进位加法器来实现,如图2所示。将式(1-3)中进位C4的逻辑方程改写为:C4=Gm0 + Pmo-C0d-4)C4表示4位加法器的进位输出,Pm0、Gm0分别表示4位加法器的进位传递输出和 进位产生输出,分别为:Pm0 = P3-P2-P1-P0G-G + PG + PPG + PPP GGm0一G3 + P3G2 + P3 P2 G1 + P3P2P1 G0将式(1-4)应用于4个4位先行进位加法器,则有:C4=Gm0 + Pm0C0C8= Gm1 + PmC4= Gm1 + Pm1Gm0 + PmPm0 C 0C

6、 = G+PC= G+ PG+ PPG+ PPPCC12Gm2 +Pm2 C8Gm2 + Pm2Gm1+ Pm2Pm1Gm0+ Pm2 Pm1 Pm0 C0C=G+PC=G+P G+P PG+PPPG+PP P P C+16 m3 m3 12 m3 m3 m2 m3 m2 m1 m3 m2 m1 m0 m3 m2 m1 m0 0(1-5)比较式(1-3)和式(1-5),可以看出这两组进位逻辑表达式是类似的。不过式(1-3) 表示的是组内进位,式(1-5)表示的是组间的进位。实现逻辑方程组(1-5)的电路称为 成组先行进位部件。图1a为所设计的32位超前进位加法器的结构框图,该加法器采用三 级超

7、前进位加法器设计,组内和组间均采用超前进位。由8个4位超前进位加法器与3个 BCLA部件构成。图1b为采用超前进位和进位选择实现的32位先行进位加法器结构图。2、结构框图:4位24282016位CLA4位bCLa4位AA4位A_S_ 2724P。.m64 位BCLAS_- 2320H S3128gm7 Pm7gm612320 A1916B1916A1512 B 1512A118B118 A74 B74 A 30 B 304位 C4位气(a)32位超前进位加法器结构图1916m4ft-S1512m3124位,CLA4位吒44位LT AlCLU *S-SF S11824位 BCLAgm1 m10S

8、 31-16S 15-0(b)超前进位+进位选择实现结构图1 32位先行进位加法器结构图3、接口说明:表1: 32位超前进位加法器接口信号说明表序号接口信号名称方向说明备注1A31:0I输入数据2B31:0I输入数据3Result31:0O加法器结果4、4位超前进位加法器的设计(4bits CLA)4.1功能概述产生进位信号(如图2a)、4位加法器的进位传递信号Px以及4位加法器的进位产生信 号Gx。Px = P3-P2-P1-P0G = G + P G + PPG + P P P GGx = G3 + P3 G2 + P3 P2 G1 + P3 P2 P1 G04.2结构框图C0G3P3G2

9、P2G1PG0 P0(a)4位超前进位链bit.Au2bit3BIT AfA BC0(b)4位超前进位加法器图2 4位CLA部件和4位超前进位加法器5、设计电路源代码(部分)/4bit carry lookahead unitmodule cla_4(p,g,c_in,c,gx,px);input3:0 p,g;input c_in;output4:1 c;output gx,px;assign c1 = p0&c_in | g0;assign c2 = p1&p0&c_in | p1&g0 | g1;assign c3 = p &p1&p0&c_in | p2&p1&g0 | p &g1 | g2;assign c4 = px&c_in | gx;assign px = p3&p2&p1&p0;assign gx = g3 | p3&g2 | p3&p2&g1 | p3&p2&p1&g0;endmodule

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。