allegro入门学习适合初学者

allegro入门学习适合初学者

《allegro入门学习适合初学者》由会员分享,可在线阅读,更多相关《allegro入门学习适合初学者(13页珍藏版)》请在装配图网上搜索。

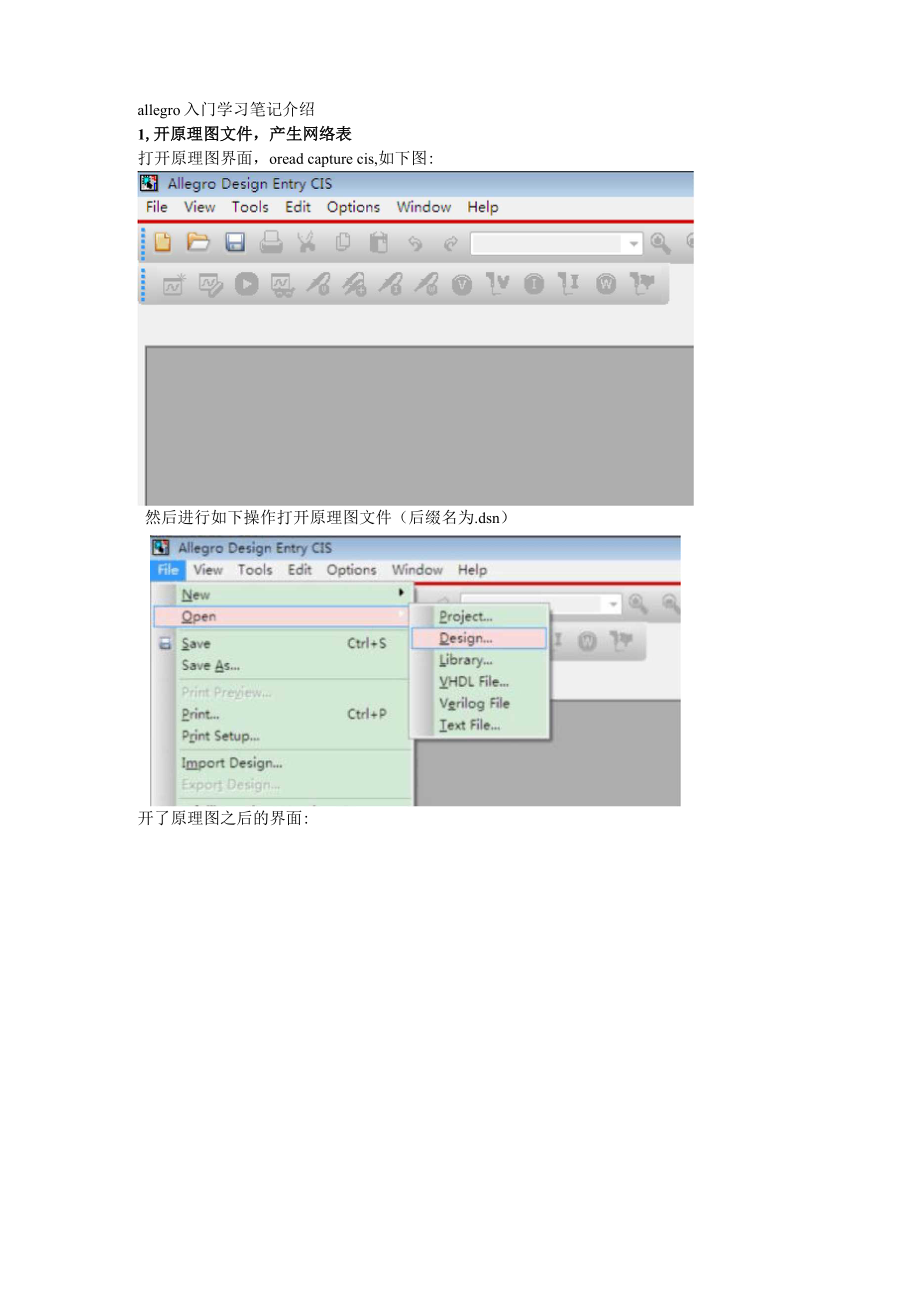

1、allegro入门学习笔记介绍1,开原理图文件,产生网络表打开原理图界面,oread capture cis,如下图:然后进行如下操作打开原理图文件(后缀名为.dsn)开了原理图之后的界面:然后产生网络表(netlist),方法如下: 选中.dsn 文件,tools-create netlist:出现如下界面,直接保持默认选项,点击确定:3 Create N區list然后出现如下窗口,点击确定:然后出现如下窗口,再继续确定:这时候会在原理图文件所在的路径里产生一个名为allegro的文件夹,我们需要的网络表就 存放在这个文件夹里。TEST.DSN.DSNlck test.d5r.OPJ_.LO

2、G TEST.DSN O.D3此时我们已经成功产生了网络表。2,打开PCB editor,导入网络表。打开绘图软件,如下图:File Edit ViewAddDisplaySetup ShapeLogic El 呂匚巳 Rou t 巳 Analyze ManufactureTools Helpcadence:u & B_e x野4 0 4遞 Allegro PCB Design XL: unnamed.brd Project: F:/O925IIi5ib 三 ty Find options我用的是cadence 16.2,其他版本的功能界面也类似。 新建一个PCB文件,后缀为.brd将其命名为

3、test.brd加1电gFo PCB De$tgr XLt unnamid-bFd Preset 卩:/02戈丘d(t yiew Add display Setup hape ogicUew.Ctrf+NQpen.CttF-i-OSave Ammpert*Export*Viewlog.FilfPlot Setyp- Pint PrevitHt Plnt_.选择board,并在上方写好命名并选好保存路径:此时,名为test.brd的PCB文件已经新建好了。然后导入网络表,操作如下:file-import-logic:出现如下界面,按照红色标记的选中,下面的import directory选择刚刚

4、产生的网络表的路径, 也就是刚刚产生的allegro文件夹路径:亲【rnport LcgicCadence OtherBranding: NoneImport logic typeDesign entry HDLo Design entrv CIS (Capture)Place changed component o AlwayseverIf same symbolUnconditionalHDL Constraint Manager Enabled Flow options(o) Import changes onlyOverwrite current constraintsDesign C

5、ompare.Allow etch removal during ECOIgnore FIXED properCreate user-defined propertiesCreate PCEl XML from input data设置好了之后,点击右上角的import cadence:然后出现下面的提示,import successful,说明导入成功:Cadence OtherB landing: Dfrsign_E rtiji_Cl 5NevesIf same symbollimpat cfrectoiy: Fest/scIValegfoPlce changed componeni:9

6、Always.Alow elch iemav during E COIgncweFIXED propsly.Cieaie utseijdefined propertiesCieale PCB XML Irom inp dataImpoit logic lypeDesign ento屮 HDIL0 Design eHiy OS |CaptueSCALDon CompH DL Constraint M anager E nabled Fkw opt kuns Impoit changes onO vefmite cutiarri Donslrdiimport Logic点 Cadence Logi

7、c Import (allegrci此时已经成功导入了网络表到PCB中。3,导入元器件封装。首先可以将界面的格点显示出来,格点显示开关是这个图标:然后绘制板框,setup-outlines-board outline:弹出如下界面,我们将board edge clearance设置为40mil.这个距离是布线边界距离板框的 最小距离。然后在空白地方画一个矩形,然后点击OK完成绘制,得到如下的板框,图中的黄色区域为可布线的区域:板框绘制完成后,导入元器件封装,place-quickplace:出现如下界面,然后点击place:此时我们会看到元器件都被放置到了板框的外面:lliAdd然后点击OK,

8、完成放置。我们可以用这个方法查看元器件是否都成功摆放:Display-status:W些Srtp Qlcr/Visibility*. ayer Pnofity.J 亡 HimCoftitrirntPnDpprty.得到下面这个界面:查看unplaced symbols,后面的0/18,说明一共有18个元器件封装,还 有0个未导入,也就是所有元器件封装都成功导入。且T Statusri 回StatusUnrouted connections:94/94100ShapesIsolated shapes:0Unassigned shapes:0Update to Smooth Out of date shapes:0/0Dynamic fill: SmoothRough DisabledDRCsUpdate DRC DR匚 errors: Out Of Date0 Waived DRC errors:0 On-Line DRCI匚RefreshHelp元器件成功导入后,我们就可以开始布局了。后面的详细内容,且听下回分解。:-)

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。