CMOS集成电路的闩锁效应

CMOS集成电路的闩锁效应

《CMOS集成电路的闩锁效应》由会员分享,可在线阅读,更多相关《CMOS集成电路的闩锁效应(3页珍藏版)》请在装配图网上搜索。

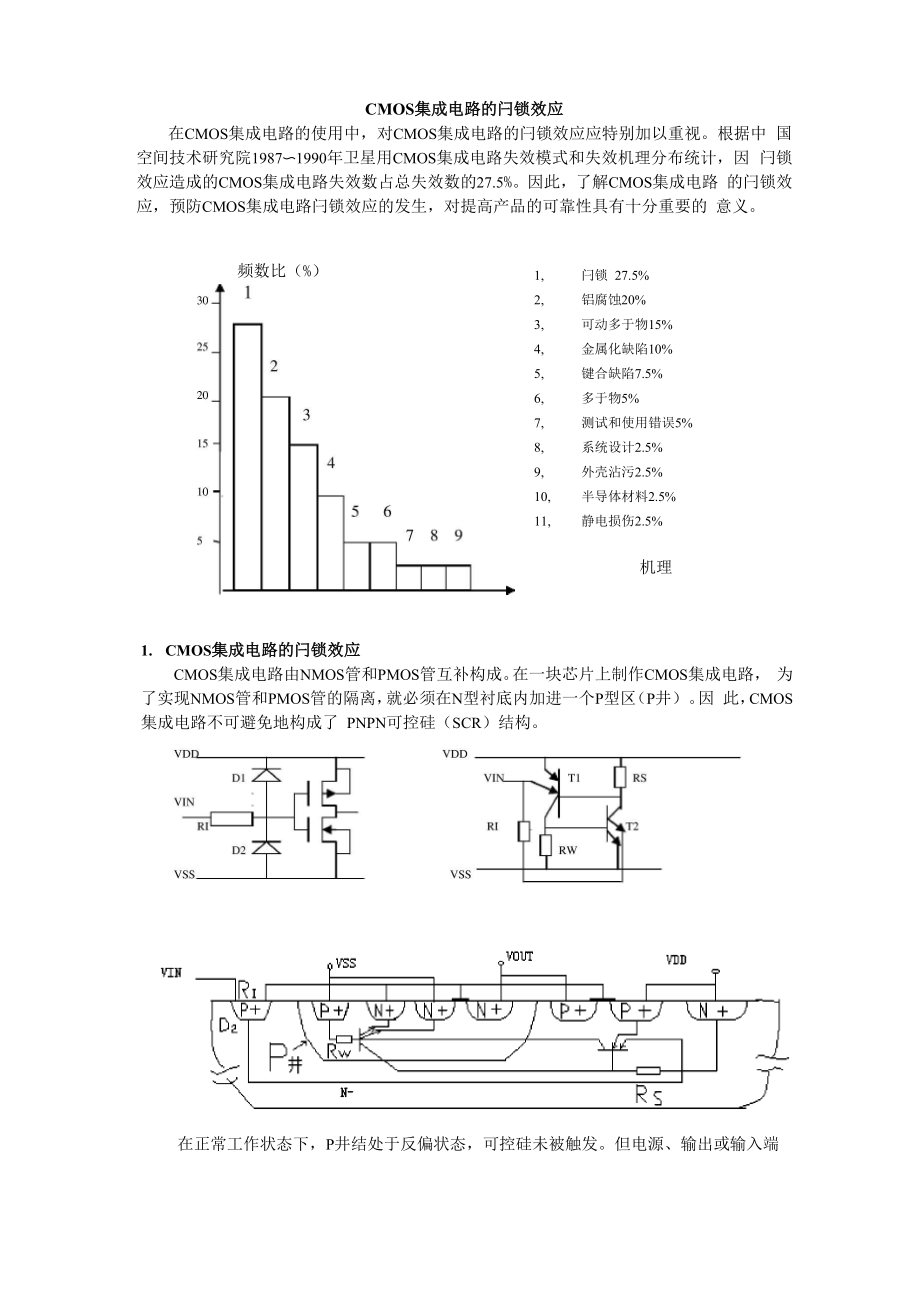

1、频数比(%)1. CMOS集成电路的闩锁效应CMOS集成电路由NMOS管和PMOS管互补构成。在一块芯片上制作CMOS集成电路, 为了实现NMOS管和PMOS管的隔离,就必须在N型衬底内加进一个P型区(P井)。因 此,CMOS集成电路不可避免地构成了 PNPN可控硅(SCR)结构。CMOS集成电路的闩锁效应在CMOS集成电路的使用中,对CMOS集成电路的闩锁效应应特别加以重视。根据中 国空间技术研究院19871990年卫星用CMOS集成电路失效模式和失效机理分布统计,因 闩锁效应造成的CMOS集成电路失效数占总失效数的27.5%。因此,了解CMOS集成电路 的闩锁效应,预防CMOS集成电路闩锁

2、效应的发生,对提高产品的可靠性具有十分重要的 意义。1, 闩锁 27.5%2, 铝腐蚀20%3, 可动多于物15%4, 金属化缺陷10%5, 键合缺陷7.5%6, 多于物5%7, 测试和使用错误5%8, 系统设计2.5%9, 外壳沾污2.5%10, 半导体材料2.5%11, 静电损伤2.5%机理在正常工作状态下,P井结处于反偏状态,可控硅未被触发。但电源、输出或输入端 有较强的电浪涌信号触发时,VDD-VSS之间将会出现地阻大电流(即CMOS电路发生闩 锁)。如果电源不加限流电阻,CMOS电路就会遭到损伤甚至被烧毁。2.闩锁的发生及预防CMOS电路的静态功耗极小,但可控硅效应被触发后功耗会变的

3、很大(50200毫安), 并导致电路发生烧毁失效。CMOS电路的硅芯片内部,在VDD与VSS之间有大量寄生可 控硅存在,并且所有输出端和输入端都是它的触发端,在正常条件下工作,由于输入和输出 电压满足下式轧要求:VDDVOUTVSSVDDVINVSS所以正常工作条件下CMOS电路不会发生可控硅效应。但在某些特殊情况下,上述条件就 会不满足,凡是出现以下情况之一,可控硅效应(闩锁)就可能发生,发生闩锁的CMOS 电路如果无限流保护就会被烧毁。1)Vin10mA时,VVB很容易出现闩锁。如果VAVB的情况无法避免,一山/可在连线间串接限流电阻L RP RP,使 IVoD,或Vin VDD,这种瞬间

4、过压可能引起闩锁。可在电源线上并入电容,电容 用10100|J F电解电容和高频电容0.010.1|J F并联。为了减少电源线内阻,电源线要尽 量短而粗。4)当输出端有大电容负载时,有可能引起闩锁。由于关断电源或者电源电压下跌使得大电容上的电压可能大于VDD,即VoutVoD。并 且大电容的充放电电流较大,容易触发闩锁。5)当外界有瞬间的过电压(电压浪涌)加到CMOS电路电源上时,有可能引起闩锁。如果浪涌电压超过二次击穿电压(一般25V30V),电路进入负阻区,将导致闩锁发 生。为了减少电源内的电压浪涌,应在电源一地之间并入电容,用来吸收瞬间过大的电压。6)抗闩锁性能差的CMOS电路容易发生闩

5、锁,不同厂家,不同工艺,不同品种的CMOS 电路,抗闩锁性能有较大差异。在选择与采购电路时,首先应选择抗闩锁性能较好的 CMOS电路。3. CMOS电路使用注意事项1为了防止CMOS电路内部的寄生可控硅被触发,输入端电压必须满足VssWVinWVDD。2加电时,先加VDD,后加Vin;先关Vin,后关Vdd。如果以上条件不能满足或接有大电容 时,输入端应串接110K限流电阻。当VDD没有加上时,若单独在输入端加脉冲,Vin 经保护二极管整形后作Vdd,容易触发闩锁,必须避免这种情况发生。3不用的输入端不能浮空,将它们接Vdd或Vss。4若输入信号的上升时间tr、下降时间tf太长,不仅会使功耗增

6、大,而且会引起数据丢失, 因先用施密特电路整形。定时电路之定时输入的上升或下降时间不得大于5MSo5输出端不能与Vdd或Vss短路。6不带三态输出,输出端不得直接“线或”、“线与”连接。7输出端接有大电容负载时,电容器要串接电阻,使充电电流小于1mA。8工作电压应小于Vdd max,至少应小于23V。9尽量避免采用多电源系统供电。10VDD和Vss绝不能接反,否则会损坏电路。11管腿不能接错、插反。12避免使输入二极管处于正向导通状态(即避免VDD+0.5VVinVSS-0.5V),如果出现瞬间 正向导通,导通电流应限制在10mA以下。13在输出端不能强迫馈入10mA以上的电流(包括瞬间馈入)。14CMOS电路与其他电路接口时要考虑逻辑摆幅、驱动电流、噪声容限及工作速度等。15防止静电放电损伤。16尽量避免带电插拔印制电路板。17禁止使用一块印制板上的CMOS电路通过长线去直接驱动另一块印制板上的CMOS电路, 尤其是对高速电路,应尽量减小分布电容、电感;尽量减小电源线、地线的电阻,以免 发生振荡。18CMOS电路用作线性放大、单稳电路和振荡器时,要注意输出端的功率过载问题。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。