用状态机实现序列检测器的设计

用状态机实现序列检测器的设计

《用状态机实现序列检测器的设计》由会员分享,可在线阅读,更多相关《用状态机实现序列检测器的设计(8页珍藏版)》请在装配图网上搜索。

1、1. 掌握基于语言的 ISE 设计全流程;实验三:用状态机实现序列检测器的设计一、实验目的用状态机实现序列检测器的设计,并对其进行仿真和硬件测试。掌握基于语言的ISE设计全流程;熟悉、应用 VerilogHDL 描述数字电路;实验原理与设计过程实验内容:序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连 续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出A,否则输出bo 由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码 及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。在检测过程中, 任何一位不

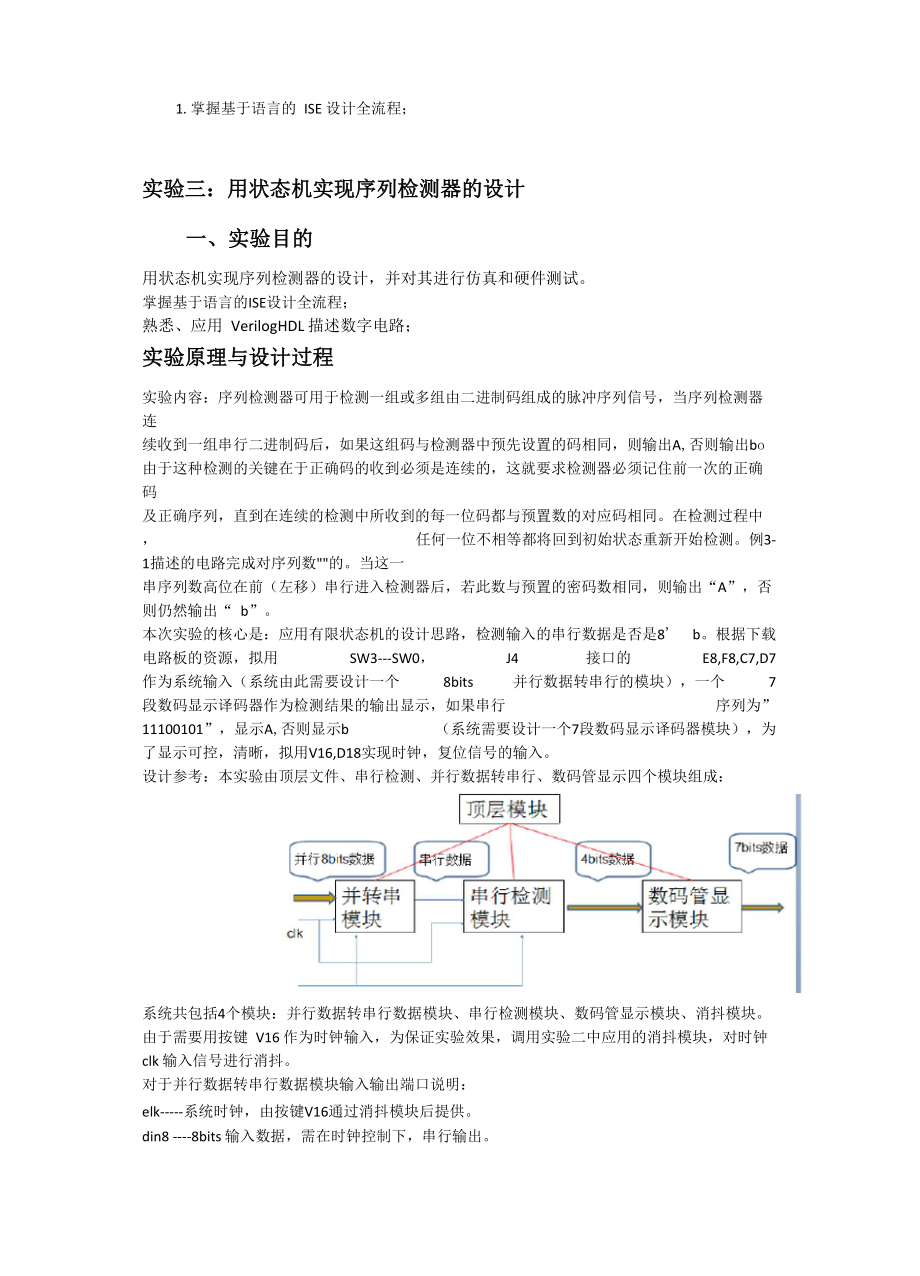

2、相等都将回到初始状态重新开始检测。例3-1描述的电路完成对序列数的。当这一 串序列数高位在前(左移)串行进入检测器后,若此数与预置的密码数相同,则输出“A”,否 则仍然输出“ b”。本次实验的核心是:应用有限状态机的设计思路,检测输入的串行数据是否是8 b。根据下载 电路板的资源,拟用 SW3-SW0, J4 接口的 E8,F8,C7,D7 作为系统输入(系统由此需要设计一个 8bits 并行数据转串行的模块),一个 7 段数码显示译码器作为检测结果的输出显示,如果串行 序列为” 11100101”,显示A,否则显示b (系统需要设计一个7段数码显示译码器模块),为 了显示可控,清晰,拟用V1

3、6,D18实现时钟,复位信号的输入。设计参考:本实验由顶层文件、串行检测、并行数据转串行、数码管显示四个模块组成:系统共包括4个模块:并行数据转串行数据模块、串行检测模块、数码管显示模块、消抖模块。 由于需要用按键 V16 作为时钟输入,为保证实验效果,调用实验二中应用的消抖模块,对时钟 clk 输入信号进行消抖。对于并行数据转串行数据模块输入输出端口说明:elk-系统时钟,由按键V16通过消抖模块后提供。din88bits 输入数据,需在时钟控制下,串行输出。reset系统复位信号,当 reset=1 b1 时,系统输出复位,否则系统正常工作。din1bit 输出信号。该并行模块的设计如下:

4、module xulie_u1(elk,din8,reset,din );input clk; input7:0 din8;input reset;output din;parameters0 = 3b000,s1 = 3b001,s2 = 3b010,s3 = 3b011,s4 = 3b100,s5 = 3b101,s6 = 3b110,s7 = 3b111;reg2:0 cur_state,next_state;reg din;always (posedge clk or posedge reset) if(reset)cur_state = s0;elsecur_state = next

5、_state;always (cur_state or din8 or din ) begincase (cur_state)s0 : begindin = din87; next_state = s1;ends1 : begindin = din86; next_state = s2;ends2 : begindin = din85; next_state = s3;ends3 : begindin = din84; next_state = s4;ends4 : begindin = din83; next_state = s5;ends5 : begindin = din82;next_

6、state = s6;ends6 : begindin = din81;next_state = s7;ends7 : begindin = din80;next_state = s0;enddefault : begindin = 1b0;next_state = s0;endendcaseendendmodule对于串行检测模块其输入输出端口说明如下:din1bit 的串行输入数据clk同步输入时钟clr -异步清零信号,当CLR=1,系统输出置0否则,系统正常工作AB4bits数据,如果系统检测到8 b的串行输入,AB=4 b1010,否则,AB=4 b1011.其设计代码如下:modu

7、le schk_u2(din,clk,reset,AB);input din;input clk;input reset;output3:0 AB;reg3:0 AB;reg3:0 current_state,next_state;parameterst0=4b0000,st1=4b0001,st2=4b0010,st3=4b0011,st4=4b0100,st5=4b0101,st6=4b0110,st7=4b0111,st8=4b1000;always (posedge clk or posedge reset)beginif(reset)current_state=st0;elsecur

8、rent_state=next_state;endalways (current_state or din)begincase(current_state)st0:begin AB=4b1011; next_state=(din=1)st1:st0;endst1:begin AB=4b1011; next_state=(din=1)st2:st0;endst2:begin AB=4b1011; next_state=(din=1)st3:st0;endst3:begin AB=4b1011; next_state=(din=0)st4:st3;endst4:begin AB=4b1011; n

9、ext_state=(din=0)st5:st1;endst5:begin AB=4b1011; next_state=(din=1)st6:st0;endst6:begin AB=4b1011; next_state=(din=0)st7:st1;endst7:beginif(din=1)begin AB=4b1010;next_state=st8;endelsebegin AB=4b1011;next_state=st0;endendst8:begin AB=4b1011; next_state=(din=1)st1:st0;endendcaseendendmodule其中最后的LED驱动

10、模块不做过多说明,只是简单的设计如下:module decled7s_u3(AB,led7 );input3:0 AB;output6:0 led7;reg6:0 led7;wire3:0 AB;initial led7=7b0000000;always (AB)begincase(AB)4b1010:led7=7b1110111;4b1011:led7=7b1111100;default:led7=7b0111111;endcaseendEndmodule(六)最终加入消抖模块综合结果如下:r-n-,皿啣Add E&JliLLjLg. SiU-c-t n:4rbL-i H= fSRircsr

11、jaa-Ale: oetodun朋i c匚肌 &BTBr Pin_lm Pwa_0wi:-3 jIjiI*ffKlUE9_KB*il.4l .dal!BKlUEI_HC4j.U vl nl is Ji Sd 1211. r)G羽-icUt.-d CwWt疋 诀-皿1|桃_曲卅-韵 i.UE4 otE fll.UEU *E:i.KrHl fjQiSyiTUwaaxs - JEU: r tfc6rrr*. Iioiet 田购TWElWTcct*: NiibheiInpE- CUfj lnpiE- X5T3J inc-e E*Ji=a ZnjLas .Io I rin_In,卜/ J.npuq -

12、HJli fan I HZ&I-r / 口uqcu- LJg_Si.ai i LiH_3ifl tr 77 lrwuc; - frai U1 iFia.ciLi rin_Guc v r/ aucpuc - to *:综合模块代码:module XULIEQI(clk_50M,clk1,reset,din8,led7 ); input clk_50M,clk1;input reset;input 7:0 din8;output 6:0 led7;wire 3:0 AB;wire din,clk;debounce_module u1(clk_50M,reset,clk1,clk); xulie_u

13、1 u2(clk, din8, reset, din);schk_u2 u3(din,clk,reset,AB); decled7s_u3 u4(AB,led7);endmodule实验仿真根据实验过程综合程序结果:din8(7:0)lcd7(6:0)clk_50Mclk1resetSaurcLXS-aurai-E f-wi.t-1 on0 iJily 曰祐血曰0c4H3TOfr-SEfiKDCllLIM ttULIEW 诃7 at iJabouriCfc_*odjiLi 间讥呼1山“扛11中 y:i u2 - sill i c_-i3L (KuLiejjj. h)刃屹-5chk_ 曲 肚工”

14、时14 - ifecle?sji3 (decltdFsjiS. )马乂ULIUjI 2 CiULIlQI 心):更回亘鱼亘主I*泠涉潍秒穽Bi* Siurcu. jj- JllQi伽目闻讣诚lx LTtriacrlaTmmsjs;临Ft DC4TXI-I. far TTEJEQTCrSiiU MW SXIFiZiS!ViiS D5L fff.Deicu UtLillies iJEKr Cftnstfianls iSyiitbLCSJEt - 1STa 沖-:0 H, j|Tl y ! KauLs旧 dicnar ! Traxrirrii elc Fil 由 I匚阪Fi jut* T u-ehL

15、 D3 cnH*ac*EErt实验引脚约束文件如下:NET clk1 LOC = V16 |PULLDOWN ;NET clk_50MNET din80NET din81NET din82NET din83NET din84NET din85NET din86NET din87NET led70NET led71NET led72NET led73NET led74NET led75NET led76LOC = C9 ;LOC = D7 ;LOC = C7 ;LOC = F8 ;LOC = E8 ;LOC = L13 ;LOC = L14 ;LOC = H18 ;LOC = N17 ;LOC

16、= D5 ;LOC = C5 ;LOC = B6 ;LOC = E7 ;LOC = F7 ;LOC = A4 ;LOC = B4 ;NET reset LOC = D18NET clk1 CLOCK_DEDICATED_ROUTE=FALSE;并行模块的时序仿真情况为:f fK -warfflemex E、 其 知电 M 茹弱 H &r诜 f 汕制 飞 时自 飞 “Ed 買 幻湘End TiMA: WnMfl处Ifferaarl百HmSPIAdM 口 anMH 强I図$JI ana 14 汕却血 a*dWR in.冲串行检测模块的相应仿真:四、思考题本次实验的设计代码表达的是 Moore 类型的状态机它的输出信号仅与当前的状态有关,与当前 的输入无关。reset=O时,当din=1,idle状态转为si状态,输出为b;当din=1,s1状态转为s2状态, 输出为b;当din=1,s2状态转为s3状态,输出为b;当din=1,s3状态转为s4状态,否则转为s3状 态,输出为b;当din=0,s4状态转为s5状态,输出为b;当din=1,s5状态转为s6状态,输出为b; 当din=0,s6状态转为s7状态,否则转为s2状态,输出为b;当din=1,s7状态转为s8状态,输出 为A。当din=1,s8状态转为si状态,输出为b,依次循环。当reset=1时,输出复位为b。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。