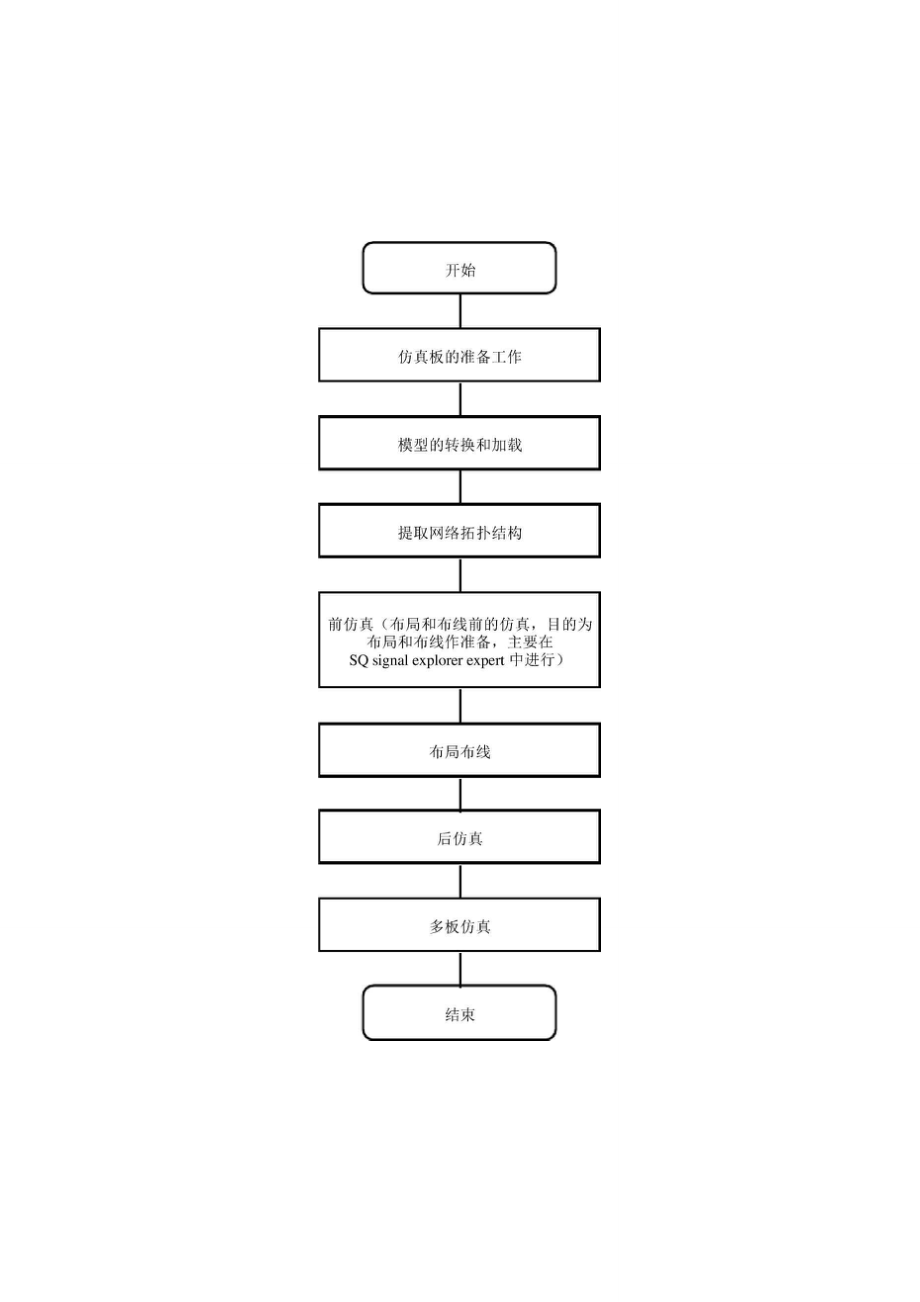

CADENCE仿真流程

CADENCE仿真流程

《CADENCE仿真流程》由会员分享,可在线阅读,更多相关《CADENCE仿真流程(24页珍藏版)》请在装配图网上搜索。

1、第一章进行SI仿真的PCB板图的准备仿真前的准备工作主要包括以下几点:1、仿真板的准备 原理图设计; PCB封装设计; PCB板外型边框(Outline)设计,PCB板禁止布线区划分(Keepouts);输出网表(如果是用CADENCE的ConceptHDL设计的原理图,可将网表直接Expot到BRD文件中;如果是用PowerPCB设计的板图,转换到allegro中的板图,其操作见附录一的说明);器件预布局(Placement):将其中的关键器件进行合理的预布局,主要涉及相对距离、抗干扰、散热、高频电路与低频电路、数字电路与模拟电路等方面; PCB板布线分区(Rooms):主要用来区分高频电路

2、与低频电路、数字电路与模拟电路以及相对独立的电路。元器件的布局以及电源和地线的处理将直接影响到电路性能和电磁兼容性能;2、器件模型的准备收集器件的IBIS模型(网上下载、向代理申请、修改同类型器件的IBIS模型等)收集器件的关键参数,如Teo、Tsetup、Tholdup等及系统有关的时间参数Tclock、Tskew、Tjitter对IBIS模型进行整理、检查、纠错和验证。3、确定需要仿真的电路部分,一般包括频率较高,负载较多,拓扑结构比较复杂(点到多点、多点到多点),时钟电路等关键信号线第二章IBIS模型的转化和加载CADENCE中的信号完整性仿真是建立在IBIS模型的基础上的,但又不是直接

3、应用IBIS模型,CADECE的软件自带一个将IBIS模型转换为自己可用的DML(DeviceModelLibrary)模型的功能模块,本章主要就IBIS模型的转换及加载进行讲解。1、IBIS模型到DML模型的转换在Allegro窗口中选择AnalyseSI/EMISIMLibrary,打开“signalanalyzelibrarybrowser”窗口,在该窗口的右下方点击“Translatef”按钮,在出现的下拉菜单中选择“ibis2signois”项,出现“SelectIBISSourceFile”窗口(图1),选择想要进行转换的源IBIS文件,按下“打开”按钮,出现转换后文件名及路径设置

4、窗口(缺省设置为和源IBIS文件同名并同路径放置,但此处文件名后缀为dml),设置后按下“保存”按钮,出现保存确定窗口(图2),点击OK按钮即可,随后会出现一个messages”窗口,该窗口中的报告文件说明在模型转换过程中出现的问题,对其中的“warning”可不用在意,但如果出现“error”则必须进行修改后重新进行模型格式转化直到没有“error”出现为止,此时转换得到的dml文件才是有效的。注:若已有规范的完整DML模型库,我们可以直接将需要的模型库加入到工作库中,即可跳过第一步直接执行第二步。图1:IBIS模型转换源文件设置窗口图2:输出dml文件确认窗口2、将转换后的dml模型加载到

5、模型库在signalanalyzelibrarybrowser窗口中,按下“AddExistingLibrary”按钮,出现下拉菜单,选择“LocalLibrary”出现“打开”窗口,选择你放置dml文件的路径并选中要加载的dml文件点击“打开”按钮就将dml文件加载到了模型库中。3、分配DML文件给特定的器件。在Allegro窗口中选择AnalyseSI/EMISIMModel,打开“SignalModelAssignment”窗口(图3所示),在该窗口中所有使用到的器件是按序排列的。可以点击“AutoSetup”进行器件模型的自动分配,此时的分配原则是如果器件的名称和模型的名称完全一致,则

6、该模型自动分配给这个元器件。也可以选中某一元器件,点击“FindModel”按钮,出现“ModelBrower”窗口,在“ModelNamePatter”一栏中填入“*”号,一些模型的名称进入下面的列表框,在列表框里选中你需要的模块后,在“SignalModelAssignment”窗口中的对应器件的“SignalName”列里就会出现它的模型名称。在“SignalModelAssignment”窗口中选中某些器件后,还可点击“CreateModel”按钮进入创建模型的界面(图4所示)。对于定义了value值的无源器件(包括电阻、电容、电感),系统会自动生成在仿真中使用的Espice模型。对于

7、没有自动生成模型的无源器件,在模型创建窗口选择“CreateEspiceModel”,而对于其他没有模型的有源器件则选择“CreateIBISModel”,然后按提示输入value值及各管脚的功能即可,同时可以存盘生成*.dat文件以备后用,此时这个新生成的模型就出现在所选器件的“SignalName”栏中。特别注意准备进行仿真的网络上所有器件都需要有模型,不要遗漏电阻、电容、电感、测试点、接插件等元件模型,否则在提取网络拓扑时会出错。图3:模型分配窗口图4:创建新模型窗口第三章提取网络拓扑结构在对被仿真网络提取拓扑之前需要对该板的数据库进行设置,整个操作步骤都在一个界面“DatabaseSe

8、tupAdvisor”中进行,之后就可进行拓扑的提取。1、“DatabaseSetupAdvisor”的设置。在Allegro中选择Tools/SetupAdvisor命令进入到“DatabaseSetupAdvisor”界面(在SpecctraQUEST界面中选择Board/SetupAdvisor命令)。选择“Next”出现“DatabaseSetupAdvisorCrossSection”窗口,点击该窗口中的“EditCrossSection”按钮进入叠层设置窗口“LayoutCrossSection”(图5所示),在这个类似Excel表格式的窗口里,输入需要的各种参数,在表格的最后一栏

9、就直接计算出该层的阻抗值。图5:叠层设置窗口选择“Next”出现“DatabaseSetupAdvisorDCNets”窗口,点击该窗口中的“IdentifyDCNets”按钮进入直流网络设置窗口“IdentifyDCNets”(图6所示)。在这个窗口中,可以对所有直流网络设置具体的电压值。图6:直流网络设置窗口选择“Next”出现“DatabaseSetupAdvisor一DeviceSetup”窗口,点击该窗口中的“DeviceSetup”按钮进入直流网络设置窗口“DeviceSetup”(图7所示)。在这个窗口中,可以对所有器件设置正确的分类属性。正确的CLASS属性对于仿真是很重要的,

10、如果设置不正确,提取出的拓扑将会有严重的错误。接插件的CLASS属性为IO,分离器件(电阻、阻排、电容、电感等)的CLASS属性为DISCRETE,集成电路的CLASS属性为IC。除了器件的CLASS属性以外,器件管脚的PINUSE属性也同样很重要。所有CLASS属性为IO和DISCRETE的器件其管脚的PINUSE属性均应为UNSPEC,而CLASS属性为IC的器件其管脚的PINUSE属性示功能不同可以为:IN、OUT、BI。器件的CLASS属性还可通过SpecctraQUEST主窗口中Logic/PartList命令调出PartList窗口进行设置(图8所示)。而器件管脚的PINUSE属性

11、只能在创建原理图库的地方设置和修改。图7:器件属性设置窗口图8:器件属性修改窗口选择“Next”出现“DatabaseSetupAdvisorSIModels”窗口,点击该窗口中的“SIModelsAssignment”按钮进入分配模型窗口“SignalModelAssignment”,这一部分的设置见第一早。选择“Next”出现“DatabaseSetupAdvisorSIAudit”窗口,这一部分通常不用设置直接点击“Finish”按钮结束DatabaseSetupAdvisor的设置。以上每一步完成后都有一个Message窗口显示该部操作引起数据库的变化,可以仔细察看一下Message窗

12、口的报告是否与你所期望的要求相互一致。2、提取拓扑拓扑结构的提取可以在Allegro的主界面也可以在SpecctraQUEST的主界面进行。在Allegro的主界面执行AnalyseSI/EMISIMProbe命令调出“SignalAnalyse”窗口(或者是在SpecctraQUEST的主界面,两者操作相同)(下图9所示),在Net栏中填入你想要进行仿真的网络,回车后与该网络相关的管脚就都出现在DriverPins、LoadPins、OthersPins这三栏中,(在数据库设置正确的情况下)点击“ViewTopology”按钮就会将该网络的拓扑结构在SigXplorer调出。图9:“Sign

13、alAnalyse”窗口Ci:netra1ntM:=Lri.:=Lger(corLTLecte-1toSPECCTRAQuestSIExpert14.1jl.nlx|晞旧I斟圈創副引悄ISipri:dl工n_tityTimingRcutiiLgAllCorLstraLntzSignalIntegrityTimingRciutiiLg_=二二二二二二二二-2t二二二二二二二11rnTrrnTTrrnrrrnTTPaHaHaHErnTrrnTTrmrmTTirmTrnrrirnra:B-:E-:B-:B-&iH-H-s-曰J曰TileEditUbjectsC-olunmViewMLiilyiEAu

14、ditToolsWirLdowHelpForHelp?pr&EeFl图10:ConstrainManager的主界面还可以从Allegro的主界面(或者SpecctraQUEST的主界面)进入ConstraintManager从而进行拓扑结构的提取。在Allegro主界面进入的路径是Setup/ElectricalConstraintSpreadsheet(或者是从SPECCTRAQUEST的主界面进入,两者的操作相同)。ConstrainManager是Cadence的约束管理器,所有连线的拓扑抽取以及对网络赋拓扑都可以在这儿进行的。操作如下:打开ConstrainManager的主界面(图

15、11所示),在Net栏点击SignalIntegrity、Timing、Routing的任何一个,右边就会将本板的全部网络显示出来,如图3.7所示。各个网络按字母排列,其中前面有“+”好的表示是总线或Xnet。右击所选网络选择SigXplorer,就将拓扑抽取出来并进入SQsignalexplorerexpert界面图12,所有网络的前仿真是在这个界面中进行ConstraioJ.Wanacer(cnnriected(nSPBCCrRAjQues+SIEkjer,14.L)-Uets:RotlH疋-Fi1*色dJtDkjftc-teColaiinwaAjL-alyzc*Aulit7d:1eVla

16、doA-ljLpRjDutingKU.Canstrun-t=RcoitiiLE:ActiKleaiTALlB.ODTitSCXl).tfin-slycc-ZEEhWiriiy?/ni(pedance7Min/TWazF41SjipLcTBr.TeiifT论山iJieleclKazKefcreiiL-ced!ydriLaunchSisKDloretrtocreateor.editatapdloE?tenplitefi.usrloTittirsldp.Renjl*CrsiitEa.puj.dLyLlayieUETlH:tlllEllf5CFUiln212115-1吒m由.rllt面FH:Sicn-

17、alLiiecrityTining日SyctciB曰od.t4.jgoai,rjL_LTi-am(so_1):daEH-tfoSfrriirsiiTAcfcinyriiDEferafiriiBTaiiiitsraZTr:iHITliia图11:ConstraintManager中的网络图12:SQsignalexplorerexpert界面还有一种建立拓扑结构的方法就是直接在SigXplorer中创建拓扑结构。打开SigXplorer,执行Anslyse/Library实行库文件的加载,操作类似于第二章的操作。点击工具按钮“AddPart”执行放置传输线、放置驱动和接收器件、放置无源器件等操作

18、(图13所示),最后连接结构体完成仿真拓扑图。FnModelBrowserInterconnectModel-Inlxl1liciostii-plTr-aceStripline._1TIineTimeLibarary:OKHelpModelModelNaneModelType图13:添加模型窗口TypeFili:已t:H-smePattern第四章前仿真前仿真是指在布局和布线之前的仿真,目的为布局和布线作准备,主要在SQsignalexplorerexpert中进行,主要有以下几个步骤:1、设置拓扑结构的仿真参数因为对各个器件及阻容器件的模型已经全部指定,所以抽取出来的拓扑上面的各IO都有相应

19、的IO模型,对那些没有指定模型的管脚,Cadence会赋给它缺省的模型。Cadence抽取出的拓扑结构是根据各元器件的相对位置并考虑到布线方便抽取的,其中互连线的距离是它计算的曼哈顿距离(即Ax+Ay)。仿真的主要目的就是根据仿真的结果来优化网络的拓扑结构,用来约束PCB布线,使布线按照最优结果方向进行。SQSignalExplorerExpert界面除了菜单与工具栏以外分为两个部分,即上面的拓扑示意图与下面的参数、测量选择以及结果、控制的标签窗口。在下面的Parameters标签窗口中的白色区域是可以编辑的,而灰色区域是无法编辑的,CIRCUIT是整个参数的总标题,下面的tlineDelay

20、Mode栏可以选择是用时间还是用长度表示传输线的延时(若用长度表示,则缺省的单位是mm,若用时间表示,则缺省的单位是ns,其中传输线的缺省传输速度是140mm每ns);userRevision表示目前的拓扑版本(第一次一般是1.0,以后修改拓扑时可以将此处的版本提高,这样以后在ConstraintManage里不用重新赋拓扑,只要升级拓扑即可)。点击开单板名称后,下面就列出本拓扑的内各个元件(包括器件、阻容、电源、传输线),可以编辑各个元件的特性;对器件,可以选择对应管脚的IOBUFFER模型,但一般不推荐去更改它的模型,因为已经赋给器件整体模型了,相应的IOBuffer的模型也就确定了。对阻

21、容器件,可以更改它们的阻容值;对电源,可以更改电源值;对传输线,可以更改以下几项:impedance,即传输线的交流阻抗,可以根据叠层情况在适当范围内更改它;propDelay,即传输线的延时来表示的长度;traceGeometry,传输线的类型,即是微带线或带状线,由于在前仿真中传输线是用一个集中式的无损耗模型来表示的,所以这边选择微带线或带状线的关系并不大;velocity,传输线的信号传输速度,这边一般不去改变它,用它的缺省值,即5567.72mil/ns,约14cm/ns。为了得到更大范围内的仿真结果,扩大参数的选择范围,我们一般对阻容器件的阻值、传输线的阻抗、传输线的长度选择多个值进

22、行扫描仿真(sweepsimulation)o2、设置激励源在各个元件的参数设定后,接着进行激励源设置。点击作为驱动源的模型上面、位号下面的Tristate,出现图14所示的窗口进行选择:在Cadence中共有7种激励:Pulse:脉冲方波,就是时钟源性质的波形,如果选择Pulse,整个界面中的其他选项是灰的,不允许再选;Rise:表示一个上升沿;FaH:表示一个下降沿;Custom:表示一种可以自定义的波形激励,这是最常用的波形,在这种形式下,首先在Frequence中输入信号的频率,在Pattern中输入波形的形状。其它的填缺省即可;QuiteHi:稳定高电平;QuiteLo:稳定低电平;

23、Tristate:三态,对非驱动源,都选择三态。设置完成后点击ok即可。图14:激励源设置窗口3、整个仿真参数的设置在SQsignalexplorerexpert主界面选择Analyze/Preference,弹出图15所示的窗口其中标签PulseStimulus设置驱动源类似时钟波形仿真时的仿真参数,在SwitchingFrequence中填入时钟的频率,其它项保持它们的缺省值; 在标签SimulationParameters中设置仿真的时间、精度等,如果你对FixedDuration选中,则仿真时间长度就是后面空格中的值,否则它将对你在激励源中填入的所有波形进行仿真。对WaveformRe

24、solution中是指仿真的精度,即每隔多少时间取一点进行仿真,如果这儿用的是Default,那么Cadence自动认定精度是仿真总时间的百分之一,也就是说它总共抽取100个点进行仿真。对CutoffFrequency中是指选定范围内对互连线的寄生参数进行计算,这主要是指在拓扑中具有真实的传输线线段时,在前仿真中可以不管这一项。对BufferDelays是指如何从仿真中得到BufferDelay,若选择FromLibrary则是指它从仿真模型里得到的,而选择On-the-fly则是从实际仿真数据中得到的,这儿必须选择On-the-fly,以使结果的正确性。 SimulationModes是指仿

25、真的快慢方式,在FTSMode中共有5种模式可以选择:Fast(驱动、接收都在快模式下)、Typical(正常模式)、Slow(慢模式)、Fast/Slow(驱动在快模式、接收在慢模式)、Slow/Fast(驱动在慢模式、接收在快模式)。为了在WorstCase下仿真,我们一般选择Fast和Slow两种模式进行仿真,最后两种模式因为在实际中不容易遇到,所以我们一般不选。DriverExcitation是指对驱动源进行选择,如选择ActiveDriver则表示只将拓扑中指定的驱动源作为驱动进行一次仿真,而如选择All-Drivers则是对拓扑中的每个能作为驱动源的器件作为驱动轮流仿真一次,如在图

26、中四个器件都可以作为驱动源(因为都是IO类型的Buffer),则会仿真4次,注意在这种情况下拓扑中的所有器件都必须设成Tristate模式,而且对驱动源是当成Pulse进行仿真的,所以在这种方式下对驱动源的参数设置在PulseStimulus中。在MeasureMode中主要设置测量的一些选择,对MeasureDelaysAt:如选InputThreshold表示以输入Buffer的Vil与Vih进行BufferDelay测量的,如选Vmeas则表示以输出Buffer的参考电压进行测量的,我们应该选择InputThresholdo对ReceiverSelection,如选All表示所有非驱动的

27、器件都作为接收,如选SelectOne则在仿真开始时它会让你选择其中的一个作为接收源。在我们的实际仿真中,对这两个选择的意义并不大,因为无论选哪一种,在仿真后数据报表中都会列出所有非驱动源的数据结果。在CustomSimulation中选择仿真的类别,Reflection表示时域发射仿真,Crosstalk表示串扰仿真,EMI表示电磁干扰仿真。在EMI标签窗口中,主要设定EMI的规则,及接收天线的距离(Cadence对EMI仿真只能看它的EMI能不能符合设定的规则)。图15:仿真参数设置窗口4、仿真结果的设置在SQsignalexplorerexpert主界面下部分中的Measurement标

28、签窗口(图16所示)中选择Reflection,在Reflection下面将需要显示结果的值选中。图16:SQsignalexplorerexpert主界面下的Measurement标签栏5、仿真在拓扑上各元件的参数设定以后以及仿真参数设定以后,即可以进行仿真。仿真可以点或执行命令Analyse/Simulation。仿真完成后,根据设置的仿真模式和仿真次数,在下面的Result栏中就会显示出相应的仿真结果数据。右击某一个数据后选择ViewWaveform,就可以进入Sigwave界面看波形。如图17所示:双击左边波形名称中任何一个波形符号即可打开或关闭相应的波形,选中波形后还可以更改波形的颜

29、色。对左边的一些波形名称解释如下:ODTAD4K3表示拓扑中D4器件K3Pin处的波形;ODTAD4K3_buffdly表示接测试负载时K3Pin处的波形;ODTAD4K3_buffdlyi表示接测试负载时K3Pad处的波形;ODTAD4K3i表示拓扑中D4器件K3Pad处的波形;注意对buffdly与buffdlyi的波形只有驱动端才有,对接收端,都只有输入端Pin与Pad的两个波形。在波形图上打开测试负载曲线和所关心的接收曲线,同时打开Vmeas和接收端的Vil、Vih,就可以进行SwitchDelay和SettleDelay等数值实际测量,测量的结果应该与主界面Result栏中的数据一致

30、。ODTAD4E3ODTAD5911-.1CDTADB2DODTADIPHeady1:44.&1nSTIO.32mVD虛.“h丰仆严t|0SBEm發1llerrleL-vtVHww说11miuniminilunimiiniHiain5L或IB-JE3IViev5H-l-3TinibUDTi.LnDisplayB戲VavefonnLLbraryElSBIO.tapcueLsii:DI目辺虫紅叫FarametermETil*EditloanGraphTadIe乂iphM&lptliUrdltied-S.iav611Usei:liefintdHi二/HasH丨|ForHeLppressFljlNET

31、图19:赋加拓扑的操作界面第五章布局布线将关键网络的拓扑全部赋完后即可将.brd文件交给PCB工程师进行布线。在设置了约束的网络布线时,会有一个动态的小标尺出现在屏幕上以显示所布线与约束之间的区别。当布线满足约束条件时,小标尺显示为绿色,当布线不满足约束条件时,小标尺显示为红色,并可通过显示的红色数字的正负号表示出布线是超过最长布线长度还是小于最短的布线长度。这种实时动态的显示可以使PCB工程师随时对布线进行调整以达到最佳的布线情况。第六章后仿真后仿真的目的是验证、检验仿真结果,是更加精确的仿真。仿真的过程和前仿真的过程相似,只是在提取拓扑时,前仿真使用的是理想传输线模型,没有考虑实际情况中的

32、各种损耗,但后仿真使用的是实际的布线参数,因此仿真的结果更为精确一些。如果在后仿真中发现问题,重要对部分关键器件及线网进行重新布局和布线。第七章多板仿真多板仿真,就是对于多块PCB板互连情况下的仿真设计,也称为系统及仿真。它们通过连接器或电缆相连接。SPECCTRAQuest通过DesignLink来定义多快PCB板是如何连接的,连接器或电缆可以用PLGC矩阵或SPICE电路模型描述。在进行系统级仿真前需要如前所述的仿真步骤一样,将连接器或电缆的模型分配好。系统级仿真需要做以下工作:在系统配置中设置DesignLink。在Cadence中打开SignalAnalysisLibraryBrows

33、er窗,在其中点击BrowseModels,然后在ModelBrowser中点击AddModel选择DesignLink,这样在模型库中就增加了一个DesignLink模型,编辑此模型,如图20。在Drawings部分需要将系统中互连的单板PCB图文件加入并指定设计名。在Connections部分需要互连的各个连接属性(如连接长度),并指定连接名。在ConnectionPinMap部分需要指定各个连接的管脚对应关系。图20:多板仿真的designlink界面图这样,就可以对存在于系统中各个单板之间的网络进行系统级的仿真,其它的仿真前的环境设置以及整个仿真过程与单板仿真完全相同。附录一:Powe

34、rPCB格式向Allegro格式的转换对于在PowerPCB中已经完成的PCB板,作如下操作:在PowerPCB的窗口界面上,选择文件菜单,选择Export操作,出现FileExport窗口,选择ASCII格式*.asc文件格式,并指定文件名称和路径(如图1.1)。点击图1.1的保存按钮后出现图1.2ASCII输出定制窗口,在该窗口中,点击“SelectALL”项、在ExpandAttributes中选中Parts和Nets两项,尤其注意在Format窗口中只能选择PowerPCBV3.0以下版本格式,否则Allegro不能正确导入。设置完成后点击OK按钮即完成了网络表的输出。在Allegro

35、中导入*.ascPCB板图在Allegro的窗口中,选择文件菜单,选择Import操作,出现一个下拉菜单,在下拉菜单中选择PADS项,出现PADSIN设置窗口(图1.3),在该窗口中设置三个必要参数:IFileEHport?lx|保存在:|OZDk(I:)cimmLinic吕ticmembededeyetenndebug_|pcbtech_JED口_|PR.0erigineer_|IBISTools_Js2ibis2_Jicip_jshannziliao_JImpedencecaculatertools1signal_JNYdocument_Jspecctra和12J文件喀1保存E)燥存类型(

36、1:rASCIIF辽注(l)取消Z图1.1在PowerPCB中输出通用ASC格式文件。ASCIIOutputmJFilenameI:lan9912.ascSelectAllUnialectAllFormatowerPCBV3.0FowerPCBV4.0土PowerPCBV3.5一FowerFCBV3.0PowerPUBV2.1FowerPCBV2.0E:p:=LTLdjV+fLbu+t!E17FartsN&tsSe+icn?0FCBF:if:inietpj-sTlReuse0T已;:t0Linez也匚lusters0Vi宜宫0Dec:iliFiclcagusUFartw切丁5卫3弓切匚ijri

37、TLtjcti-jrLE0Routez0Teardrops*Miscellaiteous“Rules扉CM中PourZAssemblyOptiqilsZTestFointsOECancelHIpASCIIOutputmJASCIIOutputmJ图1.2PowerPCB导出格式设置窗口图1.3导入PADS网表的参数设置窗口第一行输入源asc文件所在路径第二行输入网表格式转换所必需的pads_in.ini文件所在路径(注:pads_in.ini所在路径为:psd_14.2tooIsPCBbin)第三行指定Allegro格式的输出文件的路径。设置完成后运行“Run”,将在指定的目录中生成转化成功的.brd文件。在Allegro文件菜单中使用打开功能将转换好的BRD文件调入Allegro中。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。