LVDS原理与应用简介

LVDS原理与应用简介

《LVDS原理与应用简介》由会员分享,可在线阅读,更多相关《LVDS原理与应用简介(9页珍藏版)》请在装配图网上搜索。

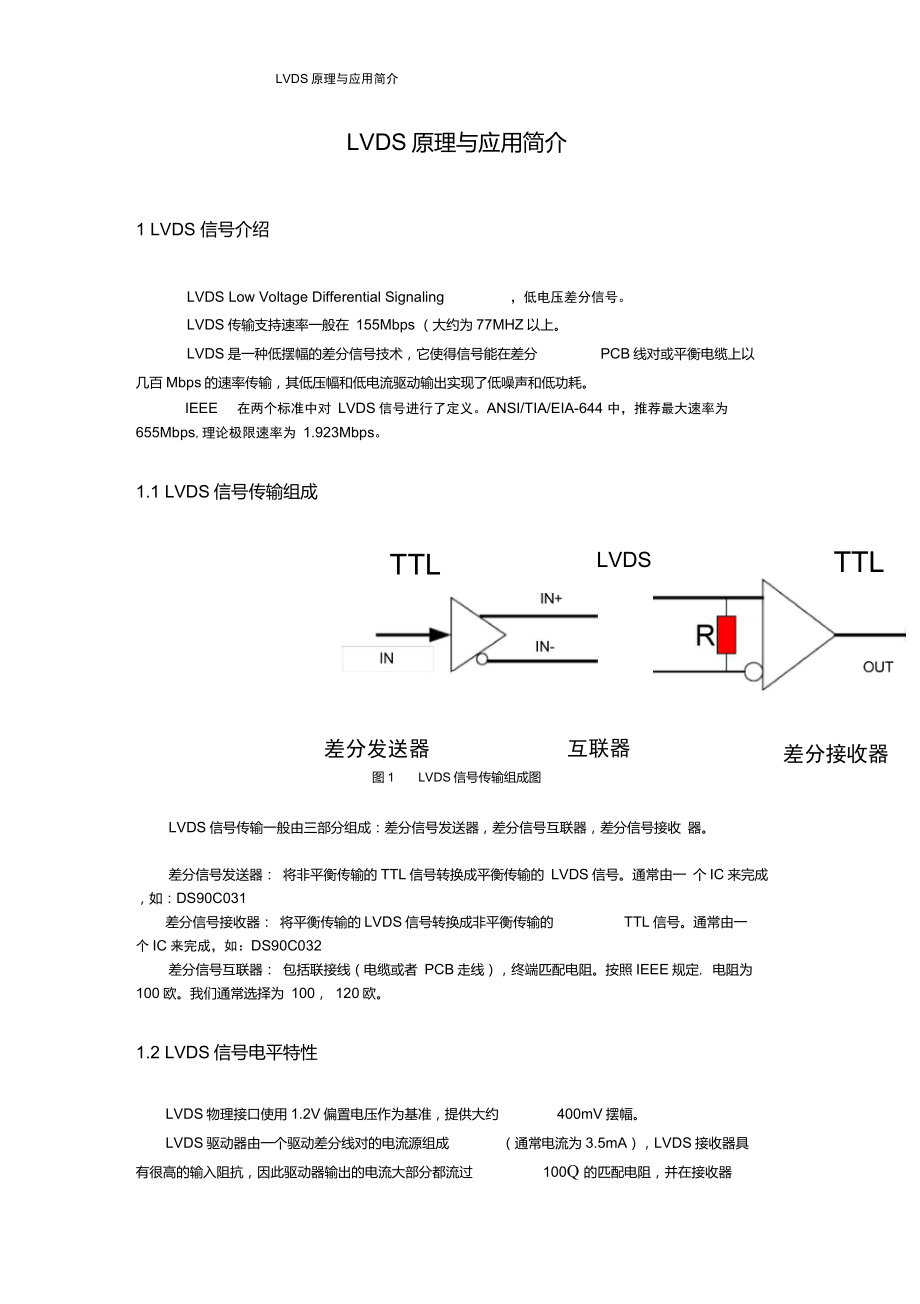

1、LVDS原理与应用简介1LVDS原理与应用简介LVDS原理与应用简介1 LVDS 信号介绍LVDS Low Voltage Differential Signaling,低电压差分信号。LVDS传输支持速率一般在 155Mbps (大约为77MHZ以上。LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。IEEE在两个标准中对 LVDS信号进行了定义。ANSI/TIA/EIA-644 中,推荐最大速率为655Mbps,理论极限速率为 1.923Mbps。1.1 LVDS信号传输组成TTLLVDSTT

2、L差分发送器互联器差分接收器图1LVDS信号传输组成图LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收 器。差分信号发送器: 将非平衡传输的TTL信号转换成平衡传输的 LVDS信号。通常由一 个IC来完成,如:DS90C031差分信号接收器: 将平衡传输的LVDS信号转换成非平衡传输的TTL信号。通常由一个IC来完成,如:DS90C032差分信号互联器: 包括联接线(电缆或者 PCB走线),终端匹配电阻。按照IEEE规定, 电阻为100欧。我们通常选择为 100, 120欧。1.2 LVDS信号电平特性LVDS物理接口使用1.2V偏置电压作为基准,提供大约400m

3、V摆幅。LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Q 的匹配电阻,并在接收器的输入端产生大约 350mV的电压。电流源为恒流特性,终端电阻在100 120欧姆之间,则电压摆动幅度为:3.5mA * 100 =350mV ; 3.5mA * 120 = 420mV。下图为LVDS与PECL (光收发器使用的电平)电平变化。2LVDS原理与应用简介 壬MWMW悔貞三壬 W *三壬 WW1 f PgIE如八期l叶丫r ri厂II*qi cm1呻 1 QVV 1J *f 1 lJ图2LVDS与PECL电

4、平图示由逻辑“ 0”电平变化到逻辑“ 1”电平是需要时间的。由于LVDS信号物理电平变化在 0。851 o 55V之间,其由逻辑“0”电平到逻辑“1 电平变化的时间比 TTL电平要快得多,所以 LVDS更适合用来传输高速变化信号。其低压 特点,功耗也低。采用低压技术适应高速变化信号,在微电子设计中的例子很多,如:FPGA芯片的内核供电电压为2o 5V或1.8V ; PC机的CPU内核电压,PIII800EB为1.8V ;数据传输领域中 很多功能芯片都采用低电压技术。1.3差分信号抗噪特性从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时, 在发送侧,可以形象理解为:IN = IN+ -

5、 IN-在接收侧,可以理解为:IN+ - IN- = OUT所以:OUT = IN在实际线路传输中,线路存在干扰,并且同时出现在差分线对上, 在发送侧,仍然是:IN = IN+ - IN-线路传输干扰同时存在于差分对上,假设干扰为q,则接收则:IN-=OUT(IN+ + q ) - (IN- + q )= IN+所以:OUT = IN噪声被抑止掉。上述可以形象理解差分方式抑止噪声的能力。在实际芯片中,是在噪声容限内,采 用“比较”及“量化”来处理的。LVDS接收器可以承受至少土 1V的驱动器与接收器之间的地的电压变化。由于LVDS驱动器典型的偏置电压为 +1.2V,地的电压变化、驱动器偏置电压

6、以及轻度耦合到的噪声之 和,在接收器的输入端相对于接收器的地是共模电压。这个共模范围是:+0.2V+2.2V。建议接收器的输入电压范围为:0V+2.4V。抑止共模噪声是 DS (差分信号)的共同特性,如 RS485,RS422电平,采用差分平衡传 输,由于其电平幅度大,更不容易受干扰,适合工业现场不太恶劣环境下通讯。2 LVDS 系统设计LVDS系统的设计要求设计者应具备超高速单板设计的经验并了解差分信号的理论。设计高速差分板并不困难,下面将简要介绍一下各注意点。2.1 PCB 板(A )至少使用4层 PCB板 (从顶层到底层):LVDS信号层、地层、电源层、TTL信号层;(B) 使TTL信号

7、和LVDS信号相互隔离,否则 TTL可能会耦合到LVDS线上,最好将 TTL和LVDS信号放在由电源/地层隔离的不同层上;(C) 使LVDS驱动器尽可能地靠近连接器的 LVDS端,即尽可能减小线路距离;(D) 保证LVDS器件电源质量;使用分布式的多个电容来旁路LVDS设备,表面贴电 容靠近电源/地层管脚放置;(E) 电源层和地层应使用粗线;(F) 保持PCB地线层返回路径宽而短;(G) 连接两个系统的地层;2.2板上导线(A) 微带传输线(microstrip )和带状线(stripline)都有较好性能;sig nal / TOP 层GND层(B) 微带传输线的优点:一般有更高的差分阻抗、

8、不需要额外的过孔;GND 层sig nal 层/BOTTOM(C) 带状线在信号间提供了更好的屏蔽,两层地将信号层屏蔽住。GND层sig nal 层GND层带状线带状信号示意图2.3差分线 _差分线的画法(A) 使用与传输媒质的差分阻抗和终端电阻相匹配的受控阻抗线,并且使差分线对离开集成芯片后立刻尽可能地相互靠近(距离小于1 Omm),这样能减少反射并能确保耦合到的噪声为共模噪声;(B) 使差分线对的长度相互匹配以减少信号扭曲,防止引起信号间的相位差而导 致电磁辐射;(C) 不要仅仅依赖自动布线功能,而应仔细修改以实现差分阻抗匹配并实现差分 线的隔离;(D) 尽量减少过孔和其它会引起线路不连续

9、性的因素;(E) 避免将导致阻值不连续性的90走线,使用圆弧或 45折线来代替;(F) 在差分线对内,两条线之间的距离应尽可能短,以保持接收器的共模抑制能 力。在印制板上,两条差分线之间的距离应尽可能保持一致,以避免差分阻抗的不连续性。2.4 终端终端接法5LVDS原理与应用简介(A) 使用终端电阻实现对差分传输线的最大匹配,阻值一般在90130 Q之间,系统也 需要此终端电阻来产生正常工作的差分电压;(B) 最好使用精度12%的表面贴电阻跨接在差分线上,必要时也可使用两个阻值各为50Q的电阻,并在中间通过一个电容接地,以更好滤去共模噪声。如采用电缆传输信号时候,若环境干扰大,就可以用此方式。

10、2.5未使用的管脚所有未使用的LVDS接收器输入管脚悬空, 所有未使用的LVDS和 TTL输出管脚悬空,将 未使用的TTL发送/驱动器输入和控制/使能管脚接电源或地。2.6媒质(电缆和连接器)选择(A)仅就减少噪声和提高信号质量而言,平衡电缆(如双绞线对)通常比非平衡电 缆好;(B)电缆长度小于0.5m时,大部分电缆都能有效工作;距离在0.5m10m之间时,CAT3(Categiory 3)双绞线对电缆效果好、 便宜并且容易买到;距离大于10m并且要求高速率时, 建议使用CAT 5双绞线对。2.7在噪声环境中提高可靠性设计LVDS接收器在内部提供了可靠性线路,用以保护在接收器输入悬空、接收器输

11、入短路 以及接收器输入匹配等情况下输出可靠。但是,当驱动器三态或者接收器上的电缆没有连接到驱动器上时,它并没有提供在噪声环境中的可靠性保证。在此情况下,电缆就变成了浮动的天线,如果电缆感应到的噪声超过LVDS内部可靠性线路的容限时,接收器就会开关或振荡。如果此种情况发生,建议使用平衡或屏蔽电缆。根据实际情况,正确分析设计发送 /接收器的“门控端”,使发送接收数据器受控,当不 需要建立发送/接收链路时候,关闭接收器是避免干扰的有效途径。3实际应用中常见问题3.1 PCB走线问题与TTL隔离,与时钟信号隔离TTL差分线对等长度走线,越是高速信号,越要求严格等长+6LVDS原理与应用简介7LVDS原

12、理与应用简介3.2过孔问题过孔问题一般原则:对于高速信号,尽量减少过孔;信号速度低于155Mbps,对于表面贴片器件,其管脚的 LVDS信号走线在PCB表层或者底层, 布线”方式,避免使用过孔联接信号。对于插件器件,由于不使用过孔,其信号线本就可以联接到PCB的来,尽量使用“带状走线”,其性能更好。3.3信号分发问题对LVDS信号进行分发处理,即将一路 用到的。LVDS信号发送到多个接收器件,使用过孔也无妨。尽量使用“微带“中间层”,这样一是我们经常会直接联接方式候,尽量按照总线走线来布线比较好,如下图示。当信号速度过高时候, 容易导致信号反射;由于避免不了过孔的存在, 高速时不要采用这种方式

13、。另外,要注意的一点是,终端匹配电阻应该是一个电阻,100欧左右,在最远的接收器输入端。若每个接收器输入端都短接上一个 100欧的匹配, 容限,抗干扰能力将下降。接收器数量不超过10个。在 PCB布线时也影响传输质量,这个电阻一定要将大大降低抗噪#LVDS原理与应用简介采用专用芯片对LVDS信号进行分发处理与上述直接总线方式联接相比较,此种做法显得保守一些,但对于提高硬件系统可靠性,保障信号传输质量而言,其优点是不言而喻的。公司推荐的LVDS分发芯片DS90LV110T,具有最大为1 : 10分发能力,10路输 出共用一个门控端。OUT1OUT2OUT3dT斗OUT 5OUT6OUT7OUTS

14、OUTSOUT108LVDS原理与应用简介#LVDS原理与应用简介在需要进行1: N信号分发时候,我们建议采用这种设计方式。3.4 LVDS交叉开关矩阵有时候,我们在设计中,需要对LVDS信号进行交叉接续,如,对 LVDS形式的时钟,通讯进行多路选择控制。此时,可以运用LVDS交叉矩阵芯片来完成设计。这里,简单介绍DS90CP22。OUflEN0畑SElflINQ最大支持800Mbps速率;3.3V供电电压选择控制端与输出门控端都为3V3电平控制330mW功耗3.5 LVDS在公司单板设计中的应用较TTL电平而言,LVDS电平信号之间的干扰,明显小于TTL信号之间的干扰。进出单板插座上的 HW

15、线,多数采用 LVDS电平收发。如交换机的各交换网板的HW线。高速时钟信号,更适合采用LVDS电平进行收发。如各时钟板对外输出时钟。板与板之间的通讯联接及媒体业务信号,也适合采用LVDS接口进行设计。如 ADSL系统中,CORE板与ATUC板之间的32路LVDS联接。3.6 LVDS与RS422/RS485的应用设计比较公司产品中,有些时钟传输使用LVDS电平,有些使用了 RS422电平。其实,RS422电平也是差分形式,其电平幅度比LVDS要大一些,抗干扰能力比 LVDS强一些,在RS422电平规范中,支持的最大速率为10Mbps (传送15米)。当时钟或者数据低于10Mbps,但对抗干扰要

16、求严格一些的时候,使用RS422方式比LVDS优点就明显一些。这在公司的产品中不难发现,如:交换机中,处于不同背板层的单板之间传送时钟,就是使 用的RS422方式。有的系统,机架上不同层的板与板之间的同步通讯,速度不高时,数据 与时钟都采用了 RS422电平接口。与 RS485相比,RS422电路中,只能有一个发送器,最 多可有10个接收器。RS485电平也是差分形式,其电平幅度比RS422还大,可以兼容掉 RS422接口。支持的最大速率为10Mbps(传送15米)o RS485抗干扰能力更强,而且支持多个发送器 (32 个) 多个接收器(32个)联接在一起。与 RS422相比,RS485更适合距离远,环境条件差的多 点通信设计。如一个集中监控单元,对同时摆在机房内的各个交换机的多个电源板进行监控, 组成分布式监控。选择 RS422接口,进行同步串行通讯设计,既有时钟传送,又有数据传送,一般只在 系统内,如同一个背板上槽位相距远一点的单板间进行;或者在同一个机架上, 不同背板层的的单板间通过双绞线电缆进行。若在同一背板上,槽位相距不远,把通讯设计成LVDS接口,也是完全可以的。在不同系统,不同机架上,一般不进行同步串行通讯设计,主要是从可靠性角度而言 的。不同系统,不同机架,数据速率不高,设计成RS485形式的异步串行通讯,更显得合适一些。9

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。