Candence数字仿真参数大全

Candence数字仿真参数大全

《Candence数字仿真参数大全》由会员分享,可在线阅读,更多相关《Candence数字仿真参数大全(7页珍藏版)》请在装配图网上搜索。

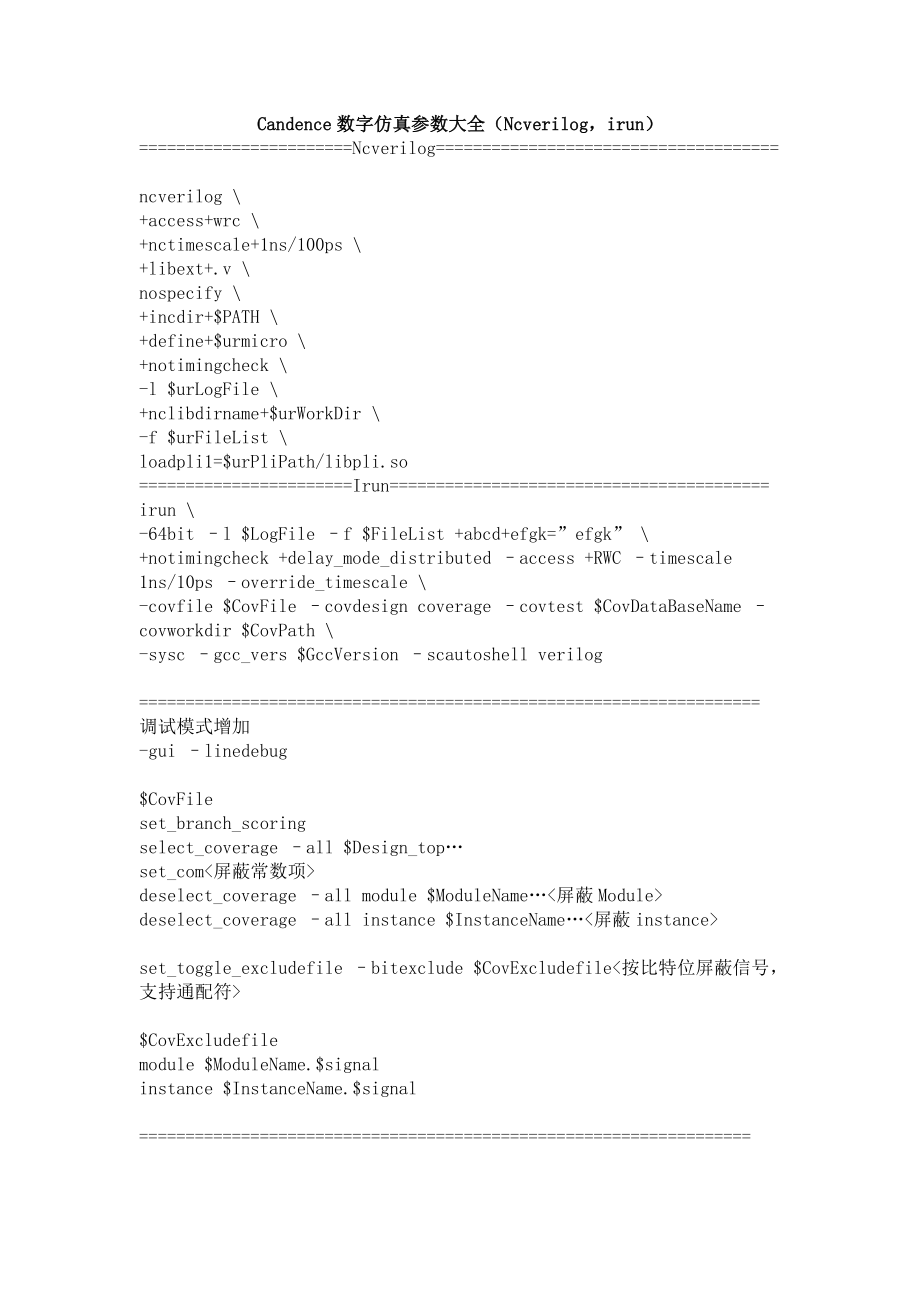

1、Candence数字仿真参数大全(Ncverilog,irun)=Ncverilog=ncverilog +access+wrc +nctimescale+1ns/100ps +libext+.v nospecify +incdir+$PATH +define+$urmicro +notimingcheck -l $urLogFile +nclibdirname+$urWorkDir -f $urFileList loadpli1=$urPliPath/libpli.so=Irun=irun -64bit l $LogFile f $FileList +abcd+efgk=”efgk” +no

2、timingcheck +delay_mode_distributed access +RWC timescale 1ns/10ps override_timescale -covfile $CovFile covdesign coverage covtest $CovDataBaseName covworkdir $CovPath -sysc gcc_vers $GccVersion scautoshell verilog=调试模式增加-gui linedebug$CovFileset_branch_scoringselect_coverage all $Design_topset_comd

3、eselect_coverage all module $ModuleNamedeselect_coverage all instance $InstanceNameset_toggle_excludefile bitexclude $CovExcludefile$CovExcludefilemodule $ModuleName.$signalinstance $InstanceName.$signal=我们知道,由于NC-Verilog使用了Native Compile Code的技术来加强电路模拟的效率,因此在进行模拟时必须经过compile(ncvlog命令)以及elaborate(nc

4、elab命令)的步骤。编译之后,针对每一个HDL设计单元会产生中间表达。接着elaborate命令会建立整个电 路的结构,产生可以用来模拟的资料。最后使用ncsim命令来进行模拟。 1、三命令模式(wolf评论:分步执行,了解即可,没有必要尝试!)命令如下:ncvlog -f run.fncealb tb -access wrcncsim tb -gui第一个命令中,run.f是整个的RTL代码的列表,值得注意的是,我们需要把tb文件放在首位,这样可以避免出现提示timescale的错误。第二个命令中,access选项是确定读取文件的权限。其中的tb是你的tb文件内的模块名字。第三个命令中,g

5、ui选项是加上图形界面值得注意的是,在这种模式下仿真,是用“- ”的。而下边要说的ncverilog是采用“+ ”的。 2、单命令模式ncverilog +access+wrc rtl +gui在这里,各参数与三命令模式相同。注意“+ ”。在本文里将详细讲述ncverilog的各种常用的参数,对于三命令模式,请读者自己查看资料。+cdslib+.设定你所仿真的库所在+define+macro .预编译宏的设定+errormax+整数当错误大于设定时退出仿真+incdir+path设定include的路径+linedebug允许在代码中设定line breakpoint(wolf评论:可以与+g

6、ui结合,利用simvision trace代码!)+log+logfile输出到名为logfile的文件中+status显示内存和CPU的使用情况+work工作库+access+w/r/c读取对象的权限,缺省为无读(-w)无写(-r)无连接(-c)+gui显示图形交互界面+input script_file输入脚本文件(wolf评论:可以通过此option输入tcl脚本)+licqueque如无licence等待licence(wolf评论:遇到licence紧张的情况,可以尝试一下!)+run如果在GUI交互界面下,启动后将自动开始仿真+loadpli1=.动态加入PLI+timescal

7、e设定仿真单位和精度(wolf评论:与nctimescale有何区别?)+nocopyright不显示版权信息+nospecifySuppresses timing checks and path delays in specify blocks.Ignore SDF annotations.+notimingcheckDont execute timing checks在Cadence Verilog仿真器中使用Verilog库:使用库文件在命令行中使用选项:-v file_name使用库目录在命令行中使用选项 y directory_name在命令行中使用选项 +libext+file_e

8、xtension(wolf评论:譬如 libext+.v)在使用库目录时,如果每个文件都有一个扩展名,则在Cadence Verilog仿真器必须用+libext选项指定其扩展名。仿真器中没有缺省地使用.v作扩展名使 用-v或-y选项指定库时,只编译那些设计中用到的模块。如果在命令行中直接输入库文件名而没有使用-v选项 (或在文件中使用编译指导include),则库中所有模块都被编译。使用选项大大压缩编译时间及内存空间。在NC Verilog中也压缩了使用的磁盘空间。3、命令大全1.ncvlog options source_file .Options:-DEFINE - Defines a

9、macro-FILE - Load command line arguments from rmation-MESSAGES- Specifies printing of informative messages-NOCOPYRIGHT- Suppresses printing of copyright banner-NOSTDOUT- Turn off output to screen-NOWARN - Disables printing of the specified warning messageExamples:- To compile all the modules in sour

10、ce.v% ncvlog source.v- To compile with informative messages% ncvlog -messages source.v2. ncelabncelab options lib.cell:viewOptions:-MESSAGES- Specifies printing of informative messages-NOCOPYRIGHT- Suppresses printing of copyright banner-NOSTDOUT- Turn off output to screen-TIMESCALE - Set default ti

11、mescale on Verilog modules.-ACCESS - Set default access visibility. +rwc turn on read/write/connectivity.-FILE - Load command line arguments from -LOADPLI1 - Specify the library_name:boot_routine(s) to dynamically load a PLI1.0 application-MAXDELAYS- Selects maximum delays for simulation-MINDELAYS-

12、Selects minimum delays for simulation-TYPDELAYS- Selects typical delays for simulation-NONEG_TCHK- Disallow negative values in SETUPHOLD & RECREM timing checks-NONOTIFIER- Notifiers are ignored in timing checks.-NOSPECIFY- Dont execute timing checks, ignore path delays and skip SDF annotations.-NOTI

13、MINGCHECKS- Dont execute timing checks-NOWARN - Disables printing of the specified warning message-NO_TCHK_MSG- Turn off timing check warnings-SDF_NO_WARNINGS- Do not report SDF warningsExamples:- To elaborate my_lib.top:behav% ncelab my_lib.top:behav% ncelab my_lib.top% ncelab top- To elaborate wit

14、h informative messages% ncelab -messages my_lib.top:behav3. ncsimncsim options lib.cell:viewOptions:-FILE - Load command line arguments from -GUI- Enter window mode before running simulation-INPUT - Script to be executed during initialization-MESSAGES- Specifies printing of informative messages-NOCO

15、PYRIGHT- Suppresses printing of copyright banner-NONTCGLITCH- Suppress delayed net glitch suppression messages-NOSTDOUT- Turn off output to screen-NOWARN - Disables printing of the specified warning message-SDF_NO_WARNINGS- Do not report SDF warningsExamples:- To simulate the snapshot my_lib.top:sna

16、p% ncsim my_lib.top:snap% ncsim my_lib.top% ncsim top- To simulate while writing to the log file ./ncsim.log% ncsim -log ./ncsim.log my_lib.top:snap- To update the snapshot my_lib.top:snap and simulate% ncsim -update my_lib.top:snap4. ncverilogncverilog all valid Verilog-XL argumentsSupported Dash o

17、ptions:-f Read host command arguments from fileSupported plus options:+access+Turn on Read, Write and/or Connectivity Access+define+Define a macro from commandline+loadpli1=Specify the library_name:boot_routine(s) to dynamically load a PLI1.0 application from commandline+maxdelaysSelects maximum del

18、ays for simulation+mindelaysSelects minimum delays for simulation+typdelaysSelects typical delays for simulation+ncdumpports_format+Specify EVCD format flag for $dumpports+neg_tchkAllow negative values in SETUPHOLD & RECREM timing checks (default)+noneg_tchkDisallow negative values in SETUPHOLD & RE

19、CREM timing checks+nocopyrightSuppresses printing of copyright banner+no_notifierNotifiers are ignored in timing checks+nosdfwarnDo not report SDF warnings+nospecifySuppresses timing checks and path delays in specify blocks.Ignore SDF annotations.+nostdoutTurn off output to screen(terminal)+notchkms

20、gTurn off timing check warnings+notimingcheckDont execute timing checks+nowarn+Disables printing of the specified warning message+sdf_nowarningsDo not report SDF warnings5. ncsdfcncsdfc options sdf_fileOptions:-COMPILE- Compile the specified SDF files (default)-DECOMPILE- Decompile the specified SDF

21、 files-LOGFILE - Specifies the file to contain log information-MESSAGES- Specifies printing of informative messages-NOCOPYRIGHT- Suppresses printing of copyright banner-OUTPUT - Redirects compiled SDF output to the specified file-WORSTCASE_ROUNDING - Truncate min delays, round max delays upExamples:

22、- To compile an SDF file:% ncsdfc dcache.sdfCreates compiled SDF file - To specify a name for the compiled SDF file:% ncsdfc ipipe.sdf -OUTPUT piledCreates compiled SDF file piled- To decompile a compiled SDF file:% ncsdf -DECOMPILE Creates decompiled SDF file - To specify a name for the decompiled

23、SDF file:% ncsdfc -DECOMPILE -OUTPUT ebox.sdfdCreates decompiled SDF file ebox.sdfd6. nchelpnchelp options tool errornchelp -cdslib | -hdlvarExamples:- To find help on the error CUVWSP from ncelab% nchelp ncelab CUVWSP- To find help on the error BADCLP from ncvlog% nchelp ncvlog BADCLP- To list the currently defined libraries% nchelp -cdslib- To list the currently supported tools% nchelp -tools- To list the help for all supported tools with the BADCLP mnemonic% nchelp -all BADCLP

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 嵌入式系统概论-以S3C2440核心为架构课件

- 地理事象的季节变化课件

- 地理中外著名旅游景观欣赏课件

- 地理中图版选修5第一章第二节主要自然灾害及其分布课件

- 地理中考复习-地图课件

- 北师大版历史八年级下册第17课《筑起钢铁长城》课件1

- 北师大版历史八下《祖国统一的历史大潮》课件5

- 北师大版历史八下《欣欣向荣的科教文体事业》3课件

- 北师大版历史八下《蓝色的地中海文明》课件

- 北师大版历史九年级下册第10课“冷战”与“热战”丁飞鹤T-课件

- 北师大版历史八下第17课《大河流域的文明曙光》课件

- 北师大版历史九上1718课课件

- 高中化学热力学复习10多重平衡与化学计算ppt课件

- 高中化学第1章化学反应与能量转化第3节化学能转化为电能电池ppt课件1鲁科版选修

- 高中化学第三节玻璃、陶瓷和水泥公开课课件