半导体存储器的工作原理1

半导体存储器的工作原理1

《半导体存储器的工作原理1》由会员分享,可在线阅读,更多相关《半导体存储器的工作原理1(37页珍藏版)》请在装配图网上搜索。

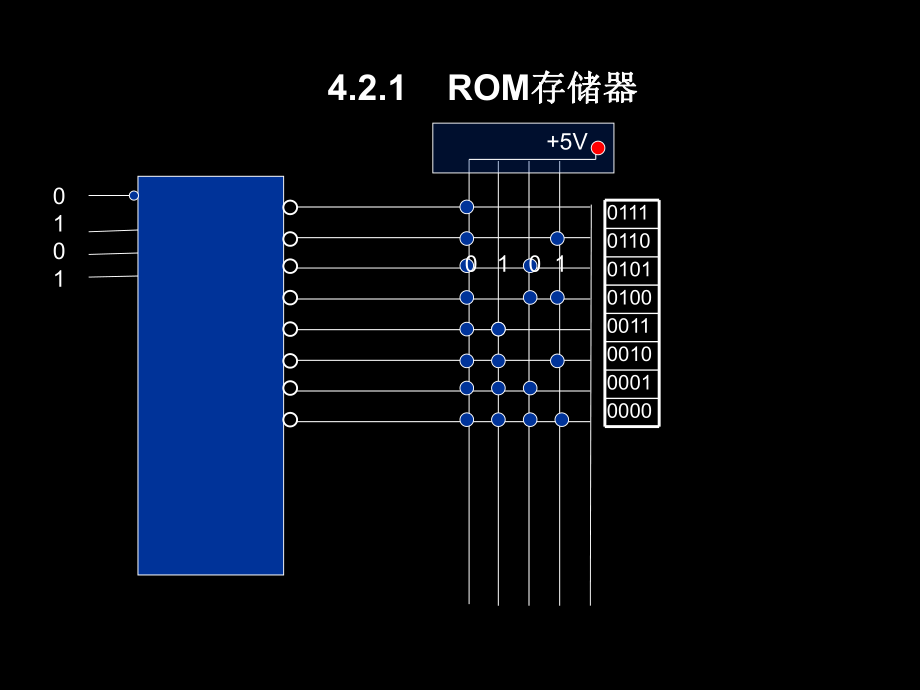

1、4.2.1 ROM存储器存储器01110110010101000011001000010000+5V01010 1 0 14.2.2 RAM的结构及工作原理的结构及工作原理1.芯片的结构及实例芯片的结构及实例存储器芯片集成了存储体及其外围电路的一块硅片(包括地址译码与驱动电路、读写放大电路及时序控制电路等)芯片形状:双列直插由若干引脚引出地址线、数据线、控制线 及电源与地线等。半导体存储器芯片一般有两种结构:字片式结构和位片式结构。存储器芯片An10Dm10R/WCS电源电源地线地线内部存储结构:字片式、位片式字片式结构的存储器(64字8位)单译码方式(一维译码):访存地址仅进行一个方向译码的

2、方式。每个存储单元电路接出一根字线和两根位线。存储阵列的每一行组成一个存储单元,存放一个8位的二进制字。一行中所有单元电路的字线联在一起,接到地址译码器的对应输出端。6位访存地址经地址译码器译码选中某一输出端有效时,与该输出端相联的一行中的每个单元电路同时进行读写操作,实现一个字的同时读/写。存储体中共有64个字,每个字为8位,排成648的阵列。存储芯片共需6根地址线,8根数据线,一次可读出一个字节。存储体中所有存储单元的相同位组成一列,一列中所有单元电路的两根位线分别连在一起,并使用一个读/写放大电路。读/写放大电路与双向数据线相连。读/写控制线 R/W:控制存储芯片的读/写操作。片选控制线

3、 CS:CS 为低电平时,选中芯片工作;CS 为高电平时,芯片不被选中。CSCSWR/操作00写01读1未选中CSWR/CS 字片式结构存储器芯片,由于采用单译码方案,有多少个存储字,就有多少个译码驱动电路,所需译码驱动电路多。双译码方式(二维译码):采用行列译码的方式,位于选中的行和列的交叉处的存储单元被唯一选中。采用双译码方式的存储芯片即位片式结构存储器芯片位片式结构的存储器芯片(4K1位)4096个存储电路,排列成6464的阵列。问:需12位地址。分为6位行地址和6位列地址。给地址 行、列译码 选中对应单元 分别选中一根行地址线和一根列地址选择线 行地址线:选中一行中的64个存储电路进

4、行读写操作。列地址线:选择64个多路转接开关,控制 各列是否能与读/写电路的接通。当选中存储芯片工作时,首先给定访存地址,并给出片选信号 CS 和读写信号 R/W 6行列地址,被选的行、列选择线的交叉处的存储电路被唯一地选中,读出或写入一位二进制信息。思考:对于4096个字采用单译码方案,需4096个译码驱动电路。若采用双译码方案,只需128个译码驱动电路。CSWR/?2.存储器芯片举例 1)Intel 2114芯片 Intel 2114 是1K4位的静态MOS存储器芯片。采用NMOS工艺制作,双列直插式封装。共18个引脚。A9A0:10根地址线,用于寻址1024个存储单元 I/O4I/O1:

5、4根双向数据线 CS:片选信号线 WE:读/写控制线+5V:5V电源线 GND:地线CSWE三态门三态门X0X63Y0Y15 2114芯片由存储体、地址缓冲器、地址译码器、读/写控制电路及三态输入输出缓冲器组成。存储体中共有4096个六管存储单元电路,排列成6464阵列。地址译码采用二维译码结构,10位地址码分成两组A8A3作为6位行地址,经行地址译码器驱动64根行选择线。A2A0及A9作为4位列地址,经列地址译码器驱动16根列选择线,每根列选择线同时选中64列中的4列,控制4个转接电路。控制被选中的4列存储电路的位线与I/O电路的接通。被选的行选择线与列选择线的交叉处的4个存储电路,就是所要

6、访问的存储字。4个存储电路对应一个字的4位。在存储体内部的阵列结构中,存储器的读/写操作由片选信号 CS 与读/写控制信号 WE 控制。CS 为高电平时,输入与输出的三态门均关闭,不能与外部的数据总线交换信息。CS 为低电平时,芯片被选中工作,若 WE 为低电平,则打开4个输入三态门,数据总线上的信息被写入被选的存储单元;若 WE 为高电平,打开4个输出三态门,从被选的存储单元中读出信息并送到数据总线上。CSWECSCSWEWE2)TMS4116芯片 TMS4116是由单管动态MOS存储单元电路构成的随机存取存储器芯片。容量为16k1位。16k的存储器应有14根地址线,为了节省引脚,该芯片只使

7、用7根地址线A6A0,采用分时复用技术,分两次把14位地址送入芯片。行地址选通信号 RAS:用于将低7位地址A6A0打入行地址缓冲器锁存。列地址选通信号 CAS:用于将高7位地址A13A7,打入列地址缓冲器锁存。RASCAS时序与控制时序与控制 行时钟行时钟列时钟列时钟写时钟写时钟 WERASCAS A6A0存储单元阵列存储单元阵列基准单元基准单元行行译译码码列译码器列译码器再生放大器再生放大器列译码器列译码器读读出出放放大大基准单元基准单元存储单元阵列存储单元阵列行行译译码码 I/O缓存器缓存器数据输出数据输出驱动驱动数据输入数据输入寄存器寄存器 DINDOUT行地址行地址缓存器缓存器列地址

8、列地址缓存器缓存器 单管动态单管动态 RAM 4116(16K 1 1位位)外特性外特性DINDOUTA6A0 读放大器读放大器 读放大器读放大器 读放大器读放大器06364127128 根行线根行线Cs01271128列列选选择择读读/写线写线数据输入数据输入I/O缓冲缓冲输出驱动输出驱动DOUTDINCs 4116(16K 1位位)芯片芯片 读读 原理原理 读放大器读放大器 读放大器读放大器 读放大器读放大器630 0 0I/O缓冲缓冲输出驱动输出驱动OUTD 读放大器读放大器 读放大器读放大器 读放大器读放大器06364127128 根行线根行线Cs01271128列列选选择择读读/写线

9、写线数据输入数据输入I/O缓冲缓冲输出驱动输出驱动DOUTDINCs 4116(16K1位位)芯片芯片 写写 原理原理数据输入数据输入I/O缓冲缓冲I/O缓冲缓冲DIN读出放大器读出放大器 读放大器读放大器630 16k1位共16384个单管MOS存储单元电路,排列成128128的阵列,并将其分为两组,每组为64行128列。每根行选择线控制128个存储电路的字线。列选择线控制读出再生放大器与I/O缓冲器的接通,控制数据的读出或写入。每一根列选择线控制一个读出再生放大器,128列共有128个读生再生放大器,一列中的128个存储电路分为两组,每64个存储电路为一组,两组存储电路的位线分别接入读出再

10、生放大器的两端。存储器的读出 行地址经行地址译码选中某一根行线有效,接通此行上的128个存储电路中的MOS管,使电容所存信息分别送到128个读出再生放大器放大。同时,经放大后的信息又回送到原电路进行重写,使信息再生。列地址经列地址译码选中某根列线有效,接通相应的列控制门,将该列上读出放大器输出的信息送入I/O缓冲器,经数据输出寄存器输出到数据总线上。存储器的写入 首先将要写入的信息由数据输入寄存器经I/O缓冲器送入被选列的读出再生放大器中,然后再写入行、列同时被选中的存储单元。DD预充电信号预充电信号读选择线读选择线写数据线写数据线写选择线写选择线读数据线读数据线VCgT4T3T2T11(1)

11、动态动态 RAM 基本单元电路基本单元电路 2.动态动态 RAM(DRAM)读出与原存信息相反读出与原存信息相反读出时数据线有电流读出时数据线有电流 为为“1”数据线数据线CsT字线字线DDV0 10 11 0写入与输入信息相同写入与输入信息相同写入时写入时 CS 充电充电 为为“1”放电放电 为为“0”T3T2T1T无电流无电流有电流有电流TMS4116的刷新 当某个存储单元被选中进行读/写操作时,该单元所在行的其余127个存储电路也将自动进行一次读出再生操作,即完成一次刷新操作。TMS4116的刷新是按行进行的,每次只加行地址,不加列地址,即可实现被选行上的所有存储电路的刷新。即一次可以刷

12、新128个存储单元电路。读出再生放大器电路 放大器由T1、T2、T3、T4组成,T6、T7与Cs是两个预选单元,由XW1与XW2控制。读写前,先使两个预选单元中的电容Cs预充电到0与1电平的中间值,并使控制信号10,21,使T3、T4截止,T5导通,使读出放大器两端Wl、W2处于相同电位。读出时,先使20,T5截止。放大器处于不稳定平衡状态。这时使11,T3、T4导通,T1、T2、T3、T4构成双稳态触发器,其稳定状态取决于W1、W2两点电位。设选中的行选择线处于读出放大器右侧(如行65),同时使处于读出放大器另一侧的预选单元选择线有效(如XW11)。这样,在放大器两侧的位线W1和W2上将有不

13、同电位:预选单元侧具有0与1电平的中间值 被选行侧具有所存信息的电平值0或1。若选中存储电路原存“1”,则W2电位高于W1的电位。使T1导通,T2截止,因而W2端输出高电平,经I/O缓冲器输出“1”信息,并且W2的高电平使被选存储电路的电容充电,实现信息再生。若选中存储电路原存“0”,则W2电位低于W1的电位。使T1截止,T2导通,因而W2端输出低电平,经I/O缓冲器输出“0”信息,并回送到原电路,使信息再生。写入时,在T3、T4开始导通的同时,将待写信息加到W2上。写1:W2加高平,将被选电路的存储电容充电为有电荷,实现写1。写0:W2为低电平,使被选电路的存储电容放电为无电荷,实现写0。4

14、116芯片的读、写周期时序 在读周期中,行地址必须在RAS有效前有效,列地址必须在CAS有效前有效,并且在CAS到来之前,WE必须为高电平,并保持到CAS结束之后。在写周期中,当WE有效之后,所加的DIN信号必须保持到CAS变为低电平之后,RAS、CAS和WE全部有效时,将DIN数据写入被选的存储单元。读周期(列选通下降沿触发)写周期(列选通下降沿触发)例:SRAM的写入时序图。其中R/W是读/写命令控制线,当R/W线为低电平时,存储器按给定地址把数据线上的数据写入存储器。请指出图中写入时序中的错误,并画出正确的写入时序图。解:写入存储器的时序信号必须同步。通常,当R/W线加负脉冲时,地址线和数据线的电平必须是稳定的。当R/W线达到低电平时,数据立即被存储。因此,当R/W线处于低电平时,如果数据线改变了数值,那么存储器将存储新的数据。同样,当R/W线处于低电平时地址线如果发生了变化,那么同样数据将存储到新的地址或。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。