数字电路习题解答

数字电路习题解答

《数字电路习题解答》由会员分享,可在线阅读,更多相关《数字电路习题解答(140页珍藏版)》请在装配图网上搜索。

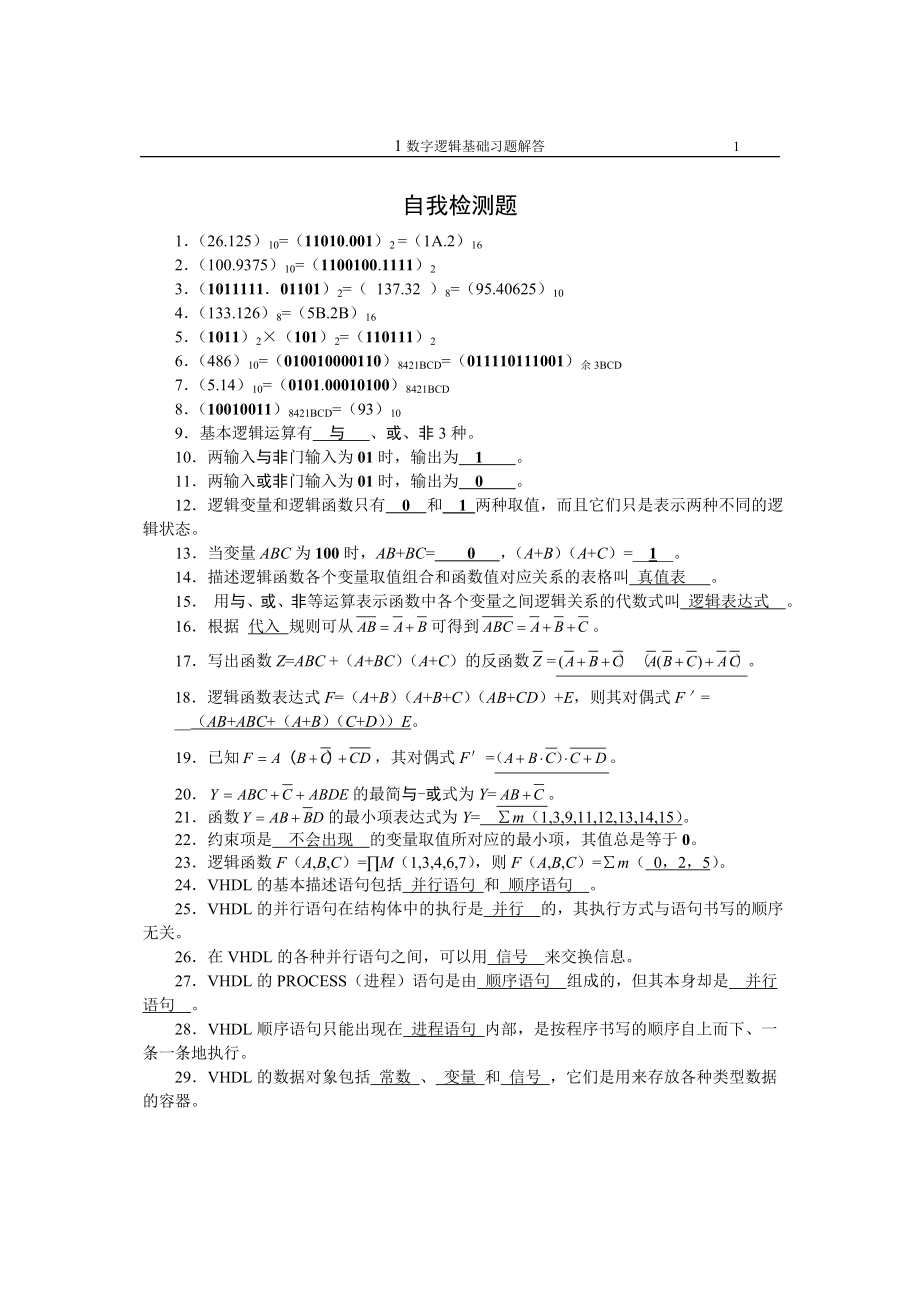

1、 1数字逻辑基础习题解答 140 自我检测题1(26.125)10=(11010.001)2 =(1A.2)162(100.9375)10=(1100100.1111)23(101111101101)2=( 137.32 )8=(95.40625)104(133.126)8=(5B.2B)165(1011)2(101)2=(110111)26(486)10=(010010000110)8421BCD=(011110111001)余3BCD7(5.14)10=(0101.00010100)8421BCD8(10010011)8421BCD=(93)109基本逻辑运算有 与 、或、非3种。10两输

2、入与非门输入为01时,输出为 1 。11两输入或非门输入为01时,输出为 0 。12逻辑变量和逻辑函数只有 0 和 1 两种取值,而且它们只是表示两种不同的逻辑状态。13当变量ABC为100时,AB+BC= 0 ,(A+B)(A+C)=_1_。14描述逻辑函数各个变量取值组合和函数值对应关系的表格叫 真值表 。15 用与、或、非等运算表示函数中各个变量之间逻辑关系的代数式叫 逻辑表达式 。16根据 代入 规则可从可得到。17写出函数Z=ABC +(A+BC)(A+C)的反函数=。 18逻辑函数表达式F=(A+B)(A+B+C)(AB+CD)+E,则其对偶式F=_(AB+ABC+(A+B)(C+

3、D)E。19已知,其对偶式F=。20的最简与-或式为Y=。21函数的最小项表达式为Y= m(1,3,9,11,12,13,14,15)。22约束项是 不会出现 的变量取值所对应的最小项,其值总是等于0。23逻辑函数F(A,B,C)=M(1,3,4,6,7),则F(A,B,C)=m( 0,2,5)。24VHDL的基本描述语句包括 并行语句 和 顺序语句 。25VHDL的并行语句在结构体中的执行是 并行 的,其执行方式与语句书写的顺序无关。26在VHDL的各种并行语句之间,可以用 信号 来交换信息。27VHDL的PROCESS(进程)语句是由 顺序语句 组成的,但其本身却是 并行语句 。28VHD

4、L顺序语句只能出现在 进程语句 内部,是按程序书写的顺序自上而下、一条一条地执行。29VHDL的数据对象包括 常数 、 变量 和 信号 ,它们是用来存放各种类型数据的容器。30下列各组数中,是6进制的是 。A14752 B62936 C53452 D3748131已知二进制数11001010,其对应的十进制数为 。A202 B192 C106 D9232十进制数62对应的十六进制数是 。A(3E)16 B(36)16 C(38)16 D(3D)16 33和二进制数(1100110111.001)2等值的十六进制数是 。 A(337.2)16 B(637.1)16 C(1467.1)16 D(C

5、37.4)1634下列四个数中与十进制数(163)10不相等的是 。A(A3)16 B(10100011)2 C(000101100011)8421BCD D(100100011)835下列数中最大数是 。A(100101110)2 B(12F)16 C(301)10 D(10010111)8421BCD36和八进制数(166)8等值的十六进制数和十进制数分别为 。A76H,118D B76H,142D CE6H,230D D74H,116D37已知A=(10.44)10 ,下列结果正确的是 。A A=(1010.1)2 BA=(0A.8)16 C A=(12.4)8 DA=(20.21)53

6、8表示任意两位无符号十进制数需要 位二进制数。A6 B7 C8 D9 39用0、1两个符号对100个信息进行编码,则至少需要 。A8位 B7位 C9位 D6位40相邻两组编码只有一位不同的编码是 。A2421BCD码 B8421BCD码 C余3码 D格雷码41下列几种说法中与BCD码的性质不符的是 。A一组4位二进制数组成的码只能表示一位十进制数BBCD码是一种人为选定的09十个数字的代码CBCD码是一组4位二进制数,能表示十六以内的任何一个十进制数DBCD码有多种42余3码10111011对应的2421码为 。A10001000 B10111011 C11101110 D1110101143

7、一个四输入端与非门,使其输出为0的输入变量取值组合有 种。 A15 B8 C7 D144一个四输入端或非门,使其输出为1的输入变量取值组合有 种。A15 B8 C7 D145A101101= 。AA B C0 D146下列四种类型的逻辑门中,可以用 实现与、或、非三种基本运算。A与门 B 或门 C非门 D与非门47若将一个异或门(设输入端为A、B)当作反相器使用,则A、B端应 连接。AA或B中有一个接高电平;BA或B中有一个接低电平;C A和B并联使用; D不能实现。48下列逻辑代数式中值为0的是 。AA A BA 1 CA 0 D49与逻辑式相等的式子是 。AABC B1+BC CA D50

8、下列逻辑等式中不成立的有 。A BC D51的最简与-或表达式为 。AFA B CFA+B+C D都不是52若已知,判断等式成立的最简单方法是依据 。A 代入规则 B对偶规则 C反演规则 D反演定理53根据反演规则,逻辑函数的反函数= 。A B C D54逻辑函数的对偶式F= 。A BC D55已知某电路的真值表如表T1.55所示,该电路的逻辑表达式为 。AF=C BF=ABC CF=AB+C D都不是表T1.55 A B CFA B CF0 0 00 0 10 1 00 1 101011 0 01 0 11 1 01 1 1011156函数F =AB +BC,使F=1的输入ABC组合为 。A

9、ABC = 000 BABC = 010 CABC = 101 DABC = 11057已知,下列组合中, 可以肯定使F=0。 AA = 0 , BC = 1 BB = 1,C = 1 CC = 1,D = 0 DBC = 1,D = 158在下列各组变量取值中,能使函数F(A,B,C,D)=m(0,1,2,4,6,13)的值为l是 。A1100 B1001 C0110 D111059以下说法中, 是正确的?A一个逻辑函数全部最小项之和恒等于1B一个逻辑函数全部最大项之和恒等于0C一个逻辑函数全部最小项之积恒等于1D一个逻辑函数全部最大项之积恒等于160标准或-与式是由 构成的逻辑表达式。 A

10、与项相或 B最小项相或 C最大项相与 D或项相与61逻辑函数F (A,B,C)= m (0,1,4,6)的最简与非-与非式为 。A B C D62若ABCDEFGH为最小项,则它有逻辑相邻项个数为 。 A8 B82 C28 D1663在四变量卡诺图中有 个小方格是“1”。A13 B12 C6 D564VHDL是在 年正式推出的。 A1983 B1985 C1987 D198965VHDL的实体部分用来指定设计单元的 。输入端口输出端口引脚以上均可66一个实体可以拥有一个或多个 。设计实体结构体输入输出67在VHDL的端口声明语句中,用 声明端口为输入方向。INOUTINOUT BUFFER68

11、在VHDL的端口声明语句中,用 声明端口为具有读功能的输出方向。INOUTINOUT BUFFER69在VHDL标识符命名规则中,以 开头的标识符是正确的。A字母 B数字C字母或数字 D下划线70 在VHDL中,目标信号的赋值符号是 。A =: B=C := D=习 题1有人说“五彩缤纷的数字世界全是由0、1及与、或、非组成的。”你如何理解这句话的含义?答:任何复杂的数字电路都可由与、或、非门组成。数字电路处理的都是0、1构成的数字信号。2用4位格雷码表示0、1、2、8、9十个数,其中规定用0000四位代码表示数0,试写出三种格雷码表示形式。解:G3G2G1G0G3G2G1G0G3G2G1G0

12、0000000000000001001001000011011011000010010010000110010110011110011110111111111110101101110111101100110001101000100000103书中表1.2-4中列出了多种常见的BCD编码方案。试写出余3循环码的特点,它与余3码有何关系?解:余3循环码的主要特点是任何两个相邻码只有一位不同,它和余3码的关系是:设余3码为B3B2B1B0,余3循环码为G3G2G1G0,可以通过以下规则将余3码转换为余3循环码。(1)如果B0和B1相同,则G0为0,否则为1;(2)如果B1和B2相同,则G1为0,否则

13、为1;(3)如果B2和B3相同,则G2为0,否则为1;(4)G3和B3相同。4如果存在某组基本运算,使任意逻辑函数F(X1,X2,Xn)均可用它们表示,则称该组基本运算组成完备集。已知与、或、非三种运算组成完备集,试证明与、异或运算组成完备集。解:将异或门的其中一个输入端接高电平即转化为非门,根据可知,利用与门和非门可以构成或门,因此,与、异或运算可以实现与、或、非三种运算,从而组成完备集。5布尔量A、B、C存在下列关系吗?(1)已知A+B=A+C,问B=C吗?为什么?(2)已知AB=AC,问B=C吗?为什么?(3)已知A+B=A+C且 AB=AC,问B=C吗?为什么?(4)最小项m115与m

14、116可合并。解:(1),因为只要A=1,不管B、C为何值,A+B=A+C即成立,没有必要B=C。(2),不成立,因为只要A=0,不管B、C为何值,AB=AC即成立,没有必要B=C。(3),当A=0时,根据A+B=A+C可得B=C;当A=1时,根据AB=AC可得B=C。(4),115=1110011B 116=1110100B逻辑不相邻。6列出逻辑函数 的真值表。解:ABCY000000100100011010011011110011107写出如图P1.7所示逻辑电路的与-或表达式,列出真值表。 图P1.7 图P1.8解:ABF0000111011108写出如图P1.8所示逻辑电路的与-或表达

15、式,列出真值表。解:表达式 真值表A B CF0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1000111009试用与非门实现逻辑函数L=AB+BC 。解:逻辑电路图10根据图P1.10所示波形图,写出逻辑关系表达式Z= f(A,B,C),并将表达式简化成最简或非-或非表达式和最简与-或-非表达式。图P1.10解:根据波形图列出真值表:ABCZ00000011010001111000101011011111利用卡诺图化简得到: 或非-或非表达式 与或非表达式11用公式法证明:解:解法一:Y1=Y2 解法二:12证明不等式。解:令当D=0时,列出函数真值表:ABC

16、Y1Y20000100110010010111110011101111100111111从真值表可知:Y1Y213已知逻辑函数,求:最简与-或式、与非-与非式、最小项表达式。解:最简与-或式:与非-与非式:最小项之和:14已知F(A,B,C)=AB+BC,求其最大项之积表达式(标准或-与式)。解:方法一:先求最小项之和,再求最大项之积。方法二:直接求。15某组合逻辑电路如图P1.15所示:(1)写出函数Y的逻辑表达式;(2)将函数Y化为最简与-或式;(3)用与非门画出其简化后的电路。图P1.15解: 16与非门组成的电路如图P1.16所示:(1)写出函数Y的逻辑表达式;(2)将函数Y化为最简与

17、-或式;(3)用与非门画出其简化后的电路。图P1.16解:,17列出如图P1.17所示逻辑电路的真值表。图P.17解:真值表ABCL1L2ABCL1L2000101000100101101010100111001011101110018用公式法化简逻辑函数:(1)(2)(3)(4)解 (1)(2) (3)(利用摩根定理) (包含律逆应用) (4)19将以下逻辑函数化简为:(1)最简或-与式;(2)最简或非-或非式。解:(1)求函数Y的对偶式Y (2)化简Y 用公式化简法化简,得 配项ABD,结合律 (3)求Y 的对偶式(Y ),即函数Y 最简或-与式再两次求反 最简或非-或非式20若两个逻辑变

18、量X、Y同时满足X+Y=1和XY = 0,则有。利用该公理证明: 。证:令,且(利用公式)(利用公式)(利用公式)(利用公式)(利用公式) ,原等式成立。21试用卡诺图法将逻辑函数化为最简与-或式:(1)F(A,B,C)=m(0,1,2,4,5,7)(2)F(A,B,C,D)=m(4,5,6,7,8,9,10,11,12,13)(3)F(A,B,C,D)= m(0,2,4,5,6,7,12)+ d(8,10)(4)F(A、B、C、D)=m(5、7、13、14)+d(3、9、10、11、15)解: (1) (2) (3) (4) 22求下面函数表达式的最简与-或表达式和最简与-或-非表达式。F=

19、m(0,6,9,10,12,15)+d(2,7,8,11,13,14)解:最简与-或表达式 23求F(A,B,C,D)=m(0,1,4,7,9,10,13)+d(2,5,8,12,15)的最简与-或式及最简或-与式。解:(1)最简与-或式 (2)最简或-与式方法一:根据最简与-或式变换得到:方法二:利用卡诺图对0方格画包围圈。24用卡诺图化简逻辑函数,给定约束条件为:。解:25用卡诺图化简逻辑函数,给定约束条件为:AB+CD = 0。解: 26用卡诺图化简逻辑函数:解:方法一:直接按照或-与表达式画卡诺图 方法二: 27用卡诺图化简逻辑函数:解:=m(1,2,3,6,7,9,11,12,13,

20、14,15)m(2,3, 7,9,10,11, 15)28有两个函数F=AB+CD、G=ACD+BC , 求M=FG 及N=F+G的最简与-或表达式。解:画出F和G的卡诺图如下:函数在进行与或运算时,只要将图中编号相同的方块,按下述的运算规则进行运算,即可求得它们的逻辑与、逻辑或等函数。其运算规则如表所示。01+010000001101111101 根据表中运算规则,得到表达式:29有两个函数, F1(A,B,C,D)= m(0,2,7,8,10,13)+ d(1,4,9),F2(A,B,C,D)=M(1,2,6,8,10,12,15)D(4,9,13),其中m、M表示最小项和最大项,d、D表

21、示无关项,试用卡诺图求:(1)的最简与-或表达式;(2)的最简或-与表达式。解:先将F2转化为最小项之和的形式:画出F1和F2的卡诺图:画出P1和P2的卡诺图: 自我检测题1CMOS门电路采用推拉式输出的主要优点是 提高速度,改善负载特性 。2CMOS与非门多余输入端的处理方法是 接高电平,接电源,与其它信号引脚并在一起。3CMOS或非门多余输入端的处理方法是接低电平,接地,与其它信号引脚并接在一起。4CMOS门电路的灌电流负载发生在输出 低 电平情况下。负载电流越大,则门电路输出电压越 高 。5CMOS门电路的静态功耗 很低 。随着输入信号频率的增加,功耗将会 增加 。6OD门在使用时输出端

22、应接 上拉电阻 和电源。7三态门有3种输出状态:0态、1态和 高阻态 。8当多个三态门的输出端连在一条总线上时,应注意 任何时刻只能有一个门电路处于工作态。9在CMOS门电路中,输出端能并联使用的电路有 OD门和 三态门 ;10CMOS传输门可以用来传输 数字 信号或 模拟 信号。11提高LSTTL门电路工作速度的两项主要措施是采用肖特基三极管和采用有源泄放电路。12当CMOS反相器的电源电压VDDVTN+(VTN、VTP分别为NMOS管和PMOS管的开启电压)时能正常工作吗?答:不能正常工作,因为,当反相器输入电压为1/2VDD时,将出现两只管子同时截止的现象,这是不允许的。13CMOS反相

23、器能作为放大器用吗?答:可以。在反相器的两端跨接了一个反馈电阻Rf就可构成高增益放大器。由于CMOS门电路的输入电流几乎等于零,所以Rf上没有压降,静态时反相器必然工作在vI=vO的状态, vI=vO=VT=VDD/ 2就是反相器的静态工作点。反相器的输入电压稍有变化,输出就发生很大变化。14如果电源电压增加5%,或者内部和负载电容增加5%,你认为哪种情况会对CMOS电路的功耗产生较大影响?解:根据公式PD=(CL+CPD)VDD2f,电源的变化对功耗影响更大。15当不同系列门电路互连时,要考虑哪几个电压和电流参数?这些参数应满足怎样的关系? 解:应考虑以下参数:VOH(min)、VIH(mi

24、n)、VOL(max)、VIL(max)、IOH(max)、IOL(max)、IIH(max),IIL(max),这些参数应满足以下条件:VOH(min) VIH(min) VOL(max) VIL(max) nIIH(max) IOL(max) m16已知图T2.16所示电路中各MOSFET管的=2V,若忽略电阻上的压降,则电路 中的管子处于导通状态。A B C D图T2.1617三极管作为开关时工作区域是 。A饱和区+放大区 B击穿区+截止区 C放大区+击穿区 D饱和区+截止区18门电路参数由大到小排列正确的是 。AVOH(min)、VIH(min)、VIL(max)、VOL(max) B

25、VIH(min)、VOH(min)、VOL(max)、VIL(max)CVOH(min)、VIH(min)、VOL(max)、VIL(max) DVIH(min)、VOH(min)、VIL(max)、VOL(max)19对CMOS门电路,以下 说法是错误的。A输入端悬空会造成逻辑出错 B输入端接510k的大电阻到地相当于接高电平 C输入端接510的小电阻到地相当于接低电平 D噪声容限与电源电压有关20某集成电路芯片,查手册知其最大输出低电平VOL(max)=0.5V,最大输入低电平VIL(max)=0.8V,最小输出高电平VOH(min)=2.7V,最小输入高电平VIH(min)=2.0V,则

26、其低电平噪声容限VNL= 。A0.4V B0.6V C0.3V C1.2V21某集成门电路,其低电平输入电流为1.0mA,高电平输入电流为10A,最大灌电流为8mA,最大拉电流为400A,则其扇出系数为N= 。A 8 B10 C 40 D2022设图T2.22所示电路均为LSTTL门电路,能实现功能的电路是 。A B C D图T2.2223设图T2.23所示电路均为CMOS门电路,实现功能的电路是 。A B C D图T2.2324如图T2.24所示LSTTL门电路,当=0时,F的状态为 。A B C D 图T2.24 图T2.2525OD门组成电路如图T2.25所示,其输出函数F为 。A B

27、C D习题1写出如图P2.1所示CMOS门电路的逻辑表达式。 图P2.1 图P2.2解: (与非门)2写出如图P2.2所示CMOS门电路的逻辑表达式。解:3双互补对与反相器引出端如图P2.3所示,试将其分别连接成:(1)三个反相器;(2)3输入端与非门;(3)3输入端或非门;(4)实现逻辑函数;(5)一个非门控制两个传输门分时传送。图P2.3解:(1)3个反相器(2)3输入与非门(3)3输入或非门(4)实现逻辑函数 连接图 等效图当C=0时,Y=1;当C=1时,(5)一个非门控制两个传输门分时传送4电路如图P2.4所示,G1为74HC系列CMOS门电路,其数据手册提供的参数为VOL(max)=

28、0.33V,VOH(min)=3.84V,IOL(max)=4mA,IOH(max)= -4mA。三极管T导通时VBE=0.7V,饱和时VCES=0.3V,发光二极管正向导通时压降VD=2.0V。(1)当输入A、B取何值时,发光二极管D有可能发光?(2)为使T管饱和,T的值应为多少?图P2.4解:(1)要使发光二极管D发光,必须使T管饱和导通,要使T管饱和导通,必须使G1输出高电平,即A和B至少有一个为低电平。(2)为使三极管导通时进入饱和状态,三极管的选择必须满足IBIBS,式中代入给定数据后,可求得17。5有一门电路内部电路如图P2.5所示,写出Y的真值表,画出相应的逻辑符号。解:真值表A

29、ENY00001高阻10111高阻逻辑符号6分析如图P2.6所示电路的逻辑功能,画出其逻辑符号。图P2.5 图P2.6解:A、B为电路输入变量,F为输出变量,只要列出真值表,就可判断其逻辑功能。A BY0 00 11 01 1高阻1高阻07由三态门构成的总线传输电路如图P2.7所示,图中n个三态门的输出接到数据传输总线,D0、D1、Dn-1为数据输入端,、为片选信号输入端。试问:(1)片选信号应满足怎样的时序关系,以便数据D0、D1、Dn-1通过总线进行正常传输?(2)如果片选信号出现两个或两个以上有效,可能发生什么情况?(3)如果所有的信号均无效,总线处在什么状态?图P2.7解:(1)片选信

30、号任何时刻只能有一个为低电平;(2)总线冲突。(3)高阻态。8分析如图P2.8(a)、(b)所示电路的逻辑功能,写出电路输出函数S的逻辑表达式。(a) (b)图P2.8解:(1)ABS000011101110输出S是A和B的异或函数,即(2)ABS000011101110输出S是A和B的异或函数,即9晶体管电路如图P2.9所示,试判断各晶体管处于什么状态? 图P2.9解:(a)根据图中参数因为iBiBS,故T1管处于放大状态。(b)因为iBiBS,故T2管处于饱和状态。10已知电路如图P2.10所示,写出F1、F2、F3和F与输入之间的逻辑表达式。图P2.10解:,11分析如图P2.11所示电

31、路的逻辑功能,指出是什么门。图P2.11解:A、B加不同电平时,T4T8的通断情况如表所示。ABT4T5T6T7T8F00offoffoffonoff101onoffoffoffon010offonoffoffon011onononoffoff1电路为OC输出的同或门.12图P2.12(a)所示为LSTTL门电路,其电气特性曲线如图P2.12(b)所示。请按给定的已知条件写出电压表的读数(填表P2.12)。假设电压表的内阻100k。 (a) (b)图P2.12表P2.12ABCK电压表读数/ V001100110101断开断开闭合闭合解:ABCK电压表读数(V)001100110101断开断开

32、闭合闭合04.31.10.213图P3.13中G1、G2、G3 为LSTTL门电路,G4、G5、G6为CMOS门电路。试指出各门的输出状态(高电平、低电平、高阻态?)。图P2.13解:Y1高电平,Y2高阻态,Y3低电平,Y4高电平,Y5低电平,Y6低电平14如图P2.14所示逻辑电路能否实现所规定的逻辑功能?如能的在括号内写“Y”,错的写“N”。图P2.14 ( ) L2=AB+CD( ) 解:Y,N15如图P2.15所示逻辑电路能否实现所规定的逻辑功能?如能的在括号内写“Y”,错的写“N”。图P2.15 ( ) ( )解:Y,N16由门电路组成的电路如图P2.16所示。试写出其逻辑表达式。图

33、P2.16解:,17由门电路组成的电路如图P2.17所示。试写出其逻辑表达式。图P2.17解:18一个发光二极管导通时的电压降约为2.0V,正常发光时需要5mA电流,当发光二极管采用如图2.2-21(a)那样连接到74LS00与非门上时,请确定电阻R的一个合适值。74LS00的相关参数可参见表2.2-3。解:注意:在大多数应用中,发光二极管串联电阻的准确值是不重要的,本例中可采用510现成电阻。19图P2.19中,LSTTL门电路的输出低电平VOL0.4V时,最大灌电流IOL(max)=8mA,输出高电平时的漏电流IOZ50A;CMOS门的输入电流可以忽略不计。如果要求Z点高、低电平VH4V、

34、VL0.4V,请计算上拉电阻RC的选择范围。图P2.19解:(1)当Z点输出高电平时,应满足下式:VH=+5V-RCIOZ4VRC20k (2)当Z点输出低电平时,应满足下式:VL=+5V-RCIOL(max)0.4VRC0.57k0.57kRC20k20在图P2.20中有两个线与的OC门G1、G2。它们的输出驱动3个LSTTL与非门G3、G4、G5。设OC门输出低电平时允许灌入的最大电流IOL(max)为14mA,输出高电平时输出管截止的漏电流IOZ为0.05mA;LSTTL与非门输入低电平电流IIL为0.22mA,每个输入端的高电平输入电流IIH为0.02mA。如果要求OC门高电平输出电压

35、VOH3V,低电平输出电压VOL0.3V,试求外接电阻RC的取值范围。图P2.21解:(1)G1、G2均输出高电平时电阻RC上流过的电流IC=2IOZ+(2+2+3)IIH=(20.05+70.02)mA=0.24mARC上的压降会使输出高电平电压下降,根据题意应满足VOH=VCC -RCIC3V因此RC应满足(2)G1或G2门输出低电平时考虑最不利的情况,只有一个OC门输出低电平,流入输出低电平OC门的电流IOL=IC+3IIL=14mA所以352RC8.33k21根据表2.4-1,试计算下列情况下的低电平噪声容限和高电平噪声容限。(1)74HCT驱动74LS;(2)74ALS驱动74HCT

36、。解:(1)VNL=VIL(max)(74LS)- VOL(max)(74HCT)= 0.8-0.1=0.7VVNH=VOH(min)(74HCT)- VIH(min)(74LS)=4.4-2=2.4V(2)VNL=VIL(max)(74HCT)- VOL(max)(74ALS)= 0.8-0.5=0.3VVNH=VOH(min)(74 ALS)- VIH(min)(74 HCT)=4.8-2=2.8V22有人使用机器上一个光电传感器,传感器受触发时,输出高电平为5V,但把这个传感器输出端接到某一电路输入端时,再次测试其输出电平,发现是2V,电平被拉低了。当换了另外一个型号的光电传感器,同样传

37、感器受触发时,输出高电平为5V,把这个传感器连接到同一电路输入端时,测试电压依然是5V。请分析可能的原因。答:最大的可能是前一种光传感器的带载能力不够,即光传感器不能提供电路输入端所需的电流,所以输出信号一接到电路输入端就会被拉低.建议:在光传感器的输出端和后级电路之间加一级驱动(射随器或三极管)。23如图P2.24所示,集成电路IC1输出七段显示码ag,高电平有效,由于IC1最大输出高电平电流很小,无法驱动共阴LED数码管(点亮每个笔划需5mA电流以上,数码管中的发光二极管导通压降为1.4V)。试从下表1提供的三种TTL非门中,选择合适器件设计共阴LED数码管的驱动电路,只需画出a和b的驱动

38、电路,需算出限流电阻的数值。图P2.24 表P2.24解:电路图为(2)当输入变高时: R720当输入变低时: R294 294R720自我检测题1组合逻辑电路任何时刻的输出信号,与该时刻的输入信号 有关 ,与以前的输入信号 无关 。2在组合逻辑电路中,当输入信号改变状态时,输出端可能出现瞬间干扰窄脉冲的现象称为 竞争冒险 。38线3线优先编码器74LS148的优先编码顺序是、,输出为。输入输出均为低电平有效。当输入为11010101时,输出为 010 。43线8线译码器74HC138处于译码状态时,当输入A2A1A0=001时,输出= 11111101 。5实现将公共数据上的数字信号按要求分

39、配到不同电路中去的电路叫 数据分配器 。6根据需要选择一路信号送到公共数据线上的电路叫 数据选择器 。7一位数值比较器,输入信号为两个要比较的一位二进制数,用A、B表示,输出信号为比较结果:Y(AB) 、Y(AB)和Y(AB),则Y(AB)的逻辑表达式为。8能完成两个一位二进制数相加,并考虑到低位进位的器件称为 全加器 。9多位加法器采用超前进位的目的是简化电路结构 。 (, )10组合逻辑电路中的冒险是由于 引起的。A电路未达到最简 B电路有多个输出C电路中的时延 D逻辑门类型不同11用取样法消除两级与非门电路中可能出现的冒险,以下说法哪一种是正确并优先考虑的?A在输出级加正取样脉冲 B在输

40、入级加正取样脉冲C在输出级加负取样脉冲 D在输入级加负取样脉冲12当二输入与非门输入为 变化时,输出可能有竞争冒险。A0110 B0010 C1011 D110113译码器74HC138的使能端取值为 时,处于允许译码状态。A011 B100 C101 D01014数据分配器和 有着相同的基本电路结构形式。A加法器 B编码器 C数据选择器 D译码器15在二进制译码器中,若输入有4位代码,则输出有 个信号。A2 B4 C8 D1616比较两位二进制数A=A1A0和B=B1B0,当AB时输出F=1,则F表达式是 。 A B C D17集成4位数值比较器74LS85级联输入IAB、IA=B、IAB分

41、别接001,当输入二个相等的4位数据时,输出FAB、FA=B、FAB分别为 。A010 B001 C100 D01118实现两个四位二进制数相乘的组合电路,应有 个输出函数。A 8 B9 C10 D11 19设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要 个异或门。A2 B3 C4 D520在图T3.20中,能实现函数的电路为 。(a) (b) (c)图T3.20A电路 (a) B电路(b) C电路(c) D都不是习 题1分析图P3.1所示组合逻辑电路的功能,要求写出与-或逻辑表达式,列出其真值表,并说明电路的逻辑功能。图P3.1解: CO=AB+BC+AC真值表ABCSCOAB

42、CSCO0000010010001101010101010110010110111111电路功能:一位全加器,A、B为两个加数,C为来自低位的进位,S是相加的和,CO是进位。2已知逻辑电路如图P3.2所示,试分析其逻辑功能。图P3.2解:(1)逻辑表达式,(2)真值表ABCFABCF00001001001110110101110101111110(3)功能从真值表看出,ABC=000或ABC=111时,F=0,而A、B、C取值不完全相同时,F=1。故这种电路称为“不一致”电路。3试用与非门设计一组合逻辑电路,其输入为3位二进制数,当输入中有奇数个1时输出为1,否则输出为0。解:(1)真值表 A

43、BCFABCF00001001001110100101110001101111(2)(无法用卡诺图化简)(3)逻辑图44位无符号二进制数A( A3A2A1A0),请设计一个组合逻辑电路实现:当0A8或12A15时,F输出1,否则,F输出0。解:(1)真值表:A3A2A1A0FA3A2A1A0F00000000000011110011001101010101111111111111111100001111001100110101010100001110(2)表达式 (3)电路图 (4)如果要求用与非门实现,则:逻辑图:5约翰和简妮夫妇有两个孩子乔和苏,全家外出吃饭一般要么去汉堡店,要么去炸鸡店。

44、每次出去吃饭前,全家要表决以决定去哪家餐厅。表决的规则是如果约翰和简妮都同意,或多数同意吃炸鸡,则他们去炸鸡店,否则就去汉堡店。试设计一组合逻辑电路实现上述表决电路。解:(1)逻辑定义:A、B、C、D分别代表约翰、简妮、乔和苏。F=1表示去炸鸡店,F=0表示去汉堡店。(2)真值表ABCDFABCDF00000000000011110011001101010101000000011111111100001111001100110101010100011111(3)用卡诺图化简 (4)逻辑图 F=AB+ACD+BCD6试设计一个全减器组合逻辑电路。全减器是可以计算三个数X、Y、BI的差,即D=X-

45、Y-CI。当XY+BI时,借位输出BO置位。解:设被减数为X,减数为Y,从低位来的借位为BI,则1位全减器的真值表如图 (a)所示,其中D为全减差,BO为向高位发出的借位输出。(1)真值表XYBIDBOXYBIDBO0000010010001111010001011110000110111111由卡诺图得电路图7设计组合逻辑电路,将4位无符号二进制数转换成格雷码。解:(1)列出4位二进制码4位格雷码的转换真值表,如表所示。输 入输 出输 入输 出B3B2B1B0G3G2G1G0B3B2B1B0G3G2G1G000000000100011000001000110011101001000111010111100110010101111100100011011001010010101111101101101100101

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。