PCI AGP PCIE关键测点

PCI AGP PCIE关键测点

《PCI AGP PCIE关键测点》由会员分享,可在线阅读,更多相关《PCI AGP PCIE关键测点(30页珍藏版)》请在装配图网上搜索。

1、vPCIvPCI总线信号定义 在介绍PCI总线信号之前,有两个名称需要解释:主设备和从设备。按照PCI总线协议,总线上所有引发PCI传输事务的实体都是主设备,凡是响应传输事务的实体都是从设备,从设备又称为目标设备。主设备应具备处理能力,能对总线进行控制,即当一个设备作为主设备时,它就是一个总线主控器。1信号类型说明 在PCI总线规范中对信号类型作了规定。下面的类型是从设备(连接在PCI总线上的每一台设备)角度定义的,而不是从仲裁器和中央资源信号角度定义的。in:表示标准输入信号。out:表示标准输出信号。ts:表示双向的三态信号。sts:表示持续的且低电平有效的三态信号,该信号在某一时刻只能属

2、于一个主设备并被其驱动,它从有效变为浮空(高阻状态)之前必须保证使其具有至少一个时钟周期的高电平状态,另一主设备要想驱动它,至少要等待该信号的原有驱动者将其释放(变为三态)一个时钟周期之后才能开始。od:表示漏极开路,以线或的形式允许多个设备共同驱动和分享。v PCI总线信号描述 1)系统信号 (1)CLK in:PCI系统总线时钟 对于所有的PCI设备该信号均为输入,其频率最高可达33 MHz,最低频率一般为0 Hz(Dc)。除RST#、INTA#、INTB#、INTC#及INTD#之外,所有其他PCI信号都在CLK的上升沿有效(或采样)。(2)RST#in:复位信号 用于复位总线上的接口逻

3、辑,并使PCI专用的寄存器、序列器和有关信号复位到指定的状态。该信号低电平有效,在它的作用下PCI总线的所有输出信号处于高阻状态,SERR#被浮空v 2)地址与数据信号 v (1)AD3100ts:地址数据多路复用信号 这是一组信号,双向三态,为地址和数据公用。在FRAME#有效(低电平)时,表示地址相位开始,该组信号线上传送的是32位物理地址;对于IO端口,这是一个字节地址;对于配置空间或存储器空间,是双字地址。在数据传送相位,该组信号线上传送数据信号,AD70为最低字节数据,而AD3124为最高字节数据。当IRDY#有效时,表示写数据稳定有效,而TRDY#有效时,则表示读数据稳定有效。在:

4、IRDY#和TRDY#都有效期间传送数据。v (2)CBE30#ts:总线命令和字节允许复用信号 双向三态信号。在地址相位中,这四条线上传输的是总线命令;在数据相位内,它们传输的是字节允许信号,表明整个数据相位中AD3100上哪些字节为有效数据,CBE0#CBE3#分别对应字节03。v (3)PAR(Paritv)ts:奇偶校验信号 双向三态。该信号用于对AD3100和cBE30上的信号进行奇偶校验,以保证数据的准确性。对于地址信号,在地址相位之后的一个时钟周期PAR稳定有效;对于数据信号,在IRDY#(写操作)或TRDY#(读操作)有效之后的一个时钟周期PAR稳定并有效,一旦PAR有效,它将

5、保持到当前数据相位结束后一个时钟。在地址相位和写操作的数据相位,PAR由主设备驱动,而在读操作的数据相位,则由从设备驱动。v 3 接口控制信号 接口控制信号共有7个,对这些信号本身及相互间配合的理解是学习PCI总线的一个关键。v(1)FRAME#(Frame)sts:帧周期信号 双向三态,低电平有效。该信号由当前主设备驱动,用来表示一个总线周期的开始和结束。该信号有效,表示总线传输操作开始,此时AD3l0和CBE30上传送的是有效地址和命令。只要该信号有效,总线传输就一直进行着。当FRAME#变为无效时,表示总线传输事务进入最后一个数据相位或该事务已经结束。v(2)IRDY#(Initiato

6、r Ready)sts:主设备准备就绪信号 双向三态,低电平有效,由主设备驱动。该信号有效表明引起本次传输的设备为当前数据相位做好了准备,但要与TRDY#配合,它们同时有效才能完成数据传输。在写周期,IRDY#表示AD310上数据有效;在读周期,该信号表示主控设备已准备好接收数据。如果IRDY#和TRDY#没有同时有效,则插入等待周期 v(3)TRDY#(Target Ready)sts:从设备准备就绪信号。双向三态,低电平有效,由从设备驱动。该信号有效表示从设备已作好当前数据传输的准备工作,可以进行相应的数据传输。同样,该信号要与IRDY#配合使用,二者同时有效才能传输数据。在写周期内,该信

7、号有效表示从设备已作好接收数据的准备;在读周期内,该信号有效表示有效数据已提交到AD310上。如果TRDY#和IRDY#没有同时有效,则插入等待周期。v(4)STOP#(stop)sts:从设备请求主设备停止当前数据传输事务 双向三态,低电平有效,由从设备驱动,用于请求总线主设备停止当前数据传送。v(5)LOCK#(Lock)sts:锁定信号 双向三态信号,低电平有效,由主设备驱动。PCI利用该信号提供一种互斥访问机制。该信号有效表示驱动它的设备对桥所进行的一个原子操作(atomic operation)可能需要多次传输才能完成,此期间该桥路被独占,而非互斥性传输事务可以在未加锁的桥上进行。L

8、OCK#有自己的协议,并和GNt#信号合作。即使有几个不同的设备在使用总线,但对LOCK#的控制权只属于某一个主设备。对主桥、PCI-T0-PCI桥以及扩展总线桥的传输事务都可以加v(6)IDSEL#(Initialization Device Select)in:初始化设备选择信号 输入信号,高电平有效,在参数配置读写传输期间用作芯片选择(片选)。v(7)DEVSEL#(Device Selecl)sts:设备选择信号 双向三态,低电平有效,由从设备驱动。当该信号由某个设备驱动时(输出),表示所译码的地址属于该设备的地址范围;当作为输入信号时,可以判断总线上是否有设备被选中。v 4)仲裁信号

9、(主设备使用)(1)REQ#(Request)ts:总线占用请求信号 双向三态,低电平有效,由希望成为总线主控设备的设备驱动。它是一个点对点信号,并且每一个主控设备都有自己的REQ#。(2)GNT#(Grant)ts:总线占用允许信号 双向三态,低电平有效。当该信号有效时表示总线占用请求被响应。这也是点对点信号,每个总线主控设备都有自己的GNT#。v 5)错误报告信号v(1)PERR#(Parity Error)sts:数据奇偶校验错信号 双向三态,低电平有效。当该信号有效,表示总线数据奇偶错,但该信号不报告特殊周期中的数据奇偶错。一个设备只有在响应设备选择信号(DEVSEL#)和完成数据相位

10、之后,才能报告一个PERR#。对于每个数据接收设备,如果发现数据有错误,就应在数据收到后的两个时钟周期内将PERR#激活。该信号的持续时间与数据相位的多少有关。如果是一个数据相位,则最小持续时间为一个时钟周期;若是一连串的数据相位且每个数据相位都有错,那么,PERR#的持续时间将多于一个时钟周期。该信号是sts信号,和所有sts信号一样,在被释放到三态之前,必须为高电平并维持一个时钟周期。另外,对于数据奇偶错的报告既不能丢失也不能推迟。v(2)SERR#(System Error)od:系统错误报告信号 漏极开路信号,低电平有效。该信号用于报告地址奇偶错、数据奇偶错、命令错等可能引起灾难性后果

11、的系统错误。SERR#信号一般接至微处理器的NMI引脚上,如果系统不希望产生非屏蔽中断,就应该采用其他方法来实现SERR#的报告。由于该信号是一个漏极开路信号,因此,发现错误的设备需将它驱动一个PCI时钟周期。SERR#信号的发出要与时钟同步,并满足所有总线信号的建立和保持的时间需求。而SERR#恢复成无效由中央资源负责,此时需要进行微小的上拉(值与上拉sts信号时相同)并持续3个时钟周期。v6)中断请求信号(可选)(1)INTx#(Interrupt)od:中断请求信号 漏极开路信号,电平触发,低电平有效。此类信号的建立与撤消与时钟不同步。对于单功能设备,只有一条中断线,而多功能设备最多可有

12、四条中断线。在前一种情况下,只能使用INTA#,其他三条中断线没有意义。所谓多功能的设备是指将几仑相互独立的功能集中在一个设备中。PCI总线中共有四条中断请求线,分别是INTA#、INTB#、INTC#和INTD#,均为漏极开路信号,其中后三个只能用于多功能设备。一个多功能设备上的任何功能都可对应于四条中断请求线中的任何一条,即各功能与中断请求线之间的对应关系是任意的,没有附加限制。二者的最终对应关系由中断引脚寄存器定义,因而具有很大的灵活性。如果一个设备要实现一个中断,就定义为INTA#;要实现两个中断,则定义为INTA#和INTB#,其他情况依此类推。对于多功能设备,可以多个功能公用同一条

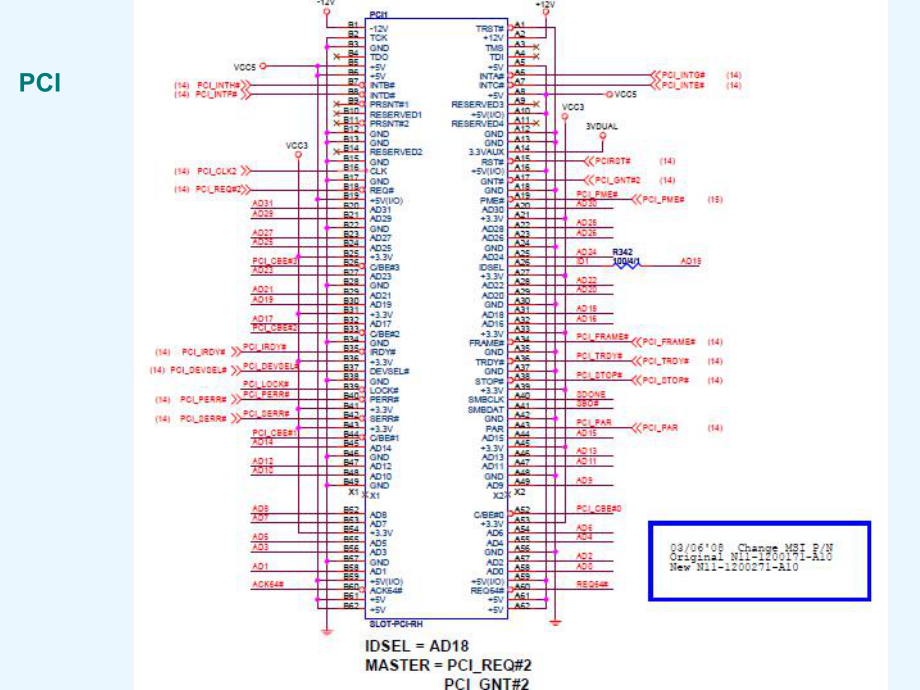

13、中断请求线,或者各自占一条,或者是两种情况的组合;而单功能设备,只能使用一条中断请求线。v 7)高速缓冲支持信号 为了使具有缓存功能的PCI存储器能够和通写式(Write-through)或回写式(Write-back)的Cache操作相配合,PCI总线设置了两个高速缓冲支持信号。(1)SBO#(Snoop Back 0ff)inout:窥视返回信号 双向,低电平有效。当该信号有效时,表示命中了一个修改行。(2)SDONE#(Snoop Done)inout:查询完成信号 双向,低电平有效。当它有效时,表示查询已经完成,反之,查询仍在进行中。vPCI插槽关键测量点v电压(+12V、-12V、+

14、5V、+3.3V)、CLK(B16)(时钟)v32位AD复用信号vFRAME#(A34)、TRDY#(A36)、IRDY(B35)、STOP#(A38)、DEVSEL(B37)、IDSEL#(A26)、C/BE#等控制信号v与PCI相关的线路连接、电阻等vAGPAGP接口訊號說明接口訊號說明1.GPIPE#I/O Pipelined Read(流水線讀)v這個信號由當前的Master來執行,它可以使用在AGP 2.0模式,但不能在AGP 3.0的規範使用。在AGP 3.0的規範中這個信號由DBI_HI(Dynamic Bus Inversion HI)代替。2.GSBA7:0 I Sideba

15、nd Address(邊帶地址)v這組訊號提供了一個附加的總線去傳輸地址和命令從AGP Master(顯示卡)到GMCH(北橋)。3.GRBF#I Read Buffer Full(讀緩存區滿)v這個信號說明Master是否可以接受先前以低優先權請求的要讀取的 數據。當RBF#為Low時,中裁器將停止以低優先權去讀取數據到Master。4.GWBF#I Write Buffer Full(寫緩存區滿)v這個信號說明Master是否可以准備接受從核心控制器的快寫數據。當WBF#為Low時,中裁器將停止這個快寫數據的交易。5.ST2:0 O Status Bus(總線狀態)v這組訊號有三BIT,可

16、以組成八組,每組分別表示當前總線的狀態。6.ADSTB0 I/O AD Bus Strobe 0(地址數據總線選通)v這個訊號可以提供2X的時序為AGP,它負責總線AD15:0。7.ADSTB0#I/O AD Bus Strobe 0(地址數據總線選通)v這個訊號可以提供4X的時序為AGP,它負責總線AD15:0。8.ADSTB1 I/O AD Bus Strobe 1(地址數據總線選通)v這個訊號可以提供2X的時序為AGP,它負責總線AD31:16。9.ADSTB1#I/O AD Bus Strobe 1(地址數據總線選通)v這個訊號可以提供4X的時序為AGP,它負責線總AD31:16。10

17、.SB_STB I SideBand Strobe(SideBand選通)v這個訊號主要為SBA7:0提供時序,它總是由AGP Master驅動。11.SB_STB#I SideBand Strobe(SideBand選通)v這個訊號為SBA7:0提供時序衹在AGP 4X 模式,它總是由AGP Master驅動。12.CLK O CLOCK(頻率)v為AGP和PCI控制訊號提供參考時序。12.PME#Power Management Event(電源管理事件)v這個信號在AGP 協議中不使用,但是它用在PCI協議中由操作系統來管理。關於PME#的詳細定義請參加PCI協議規範。13.TYPEDE

18、T#Type Detect(類型檢查)v從AGP發展來看,有1X、2X、4X和8X四種模式,每種模式所使用的電壓也不盡相同,那AGP控制器怎麼知到你插的是什麼樣的顯卡呢?就是通過這個訊號來告訴AGP Control的。用這個信號來設定當前顯卡所需的電壓。14.FRAME#I/O Frame(周期框架)v在AGP管道傳輸時這個訊號不使用,這個信號衹用在AGP的快寫方式。15.IRDY#I/O Initiator Ready(起始者備妥)v這個信號說明AGP Master已經准備好當前交易所需的數據,它衹用在寫操作,AGP Master不允許插入等待狀態。16.TRDY#I/O Target Re

19、ady(目標備妥)v這個信號說明AGP Target已經准備好整個交易所需要讀的數據,這個Target可以插入等待狀態。17.STOP#I/O Stop(停止)v這個訊號在AGP交易時不使用。對於快寫方式,當STOP#為Low時,停止當前交易。18.DEVSEL#I/O Device Select(設備選擇)v在AGP交易時不使用。在快寫方式,當在一個交易不能完成時,它就會被使用。19.REQ#I Request(請求)v這個訊號用於向中裁器請求當前總線使用權為開始一個PCI or AGP交易。20.GNT#O Grant(保證)v當中裁器收到Initiator發出請求後,若當前總線為空閑,中裁器就會通過GNT#把總線控制權交給Initiator。21.AD31:0 I/O Address Data Bus(數據地址總線)v這些訊號用來傳輸地址和數據。22.C/BE3:0#I/O Command/Byte Enable(命令位元致能)v當一個交易開始時,提供命令信息。在AGP Master做寫交易時,提供有效的位元信息。vAGP关键测试点v检查32位AD复用信号对地阻值v检查控制信号对地阻值vPCI-E vPCI-E X16架构及电压测量点vPCI-E X16时钟连接及测量点vPCI-E X1架构及电压时钟测量点v关键测量点v复位(A11)vTX/RX信号对地阻值应一致

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。