Atmega16单片机介绍

Atmega16单片机介绍

《Atmega16单片机介绍》由会员分享,可在线阅读,更多相关《Atmega16单片机介绍(6页珍藏版)》请在装配图网上搜索。

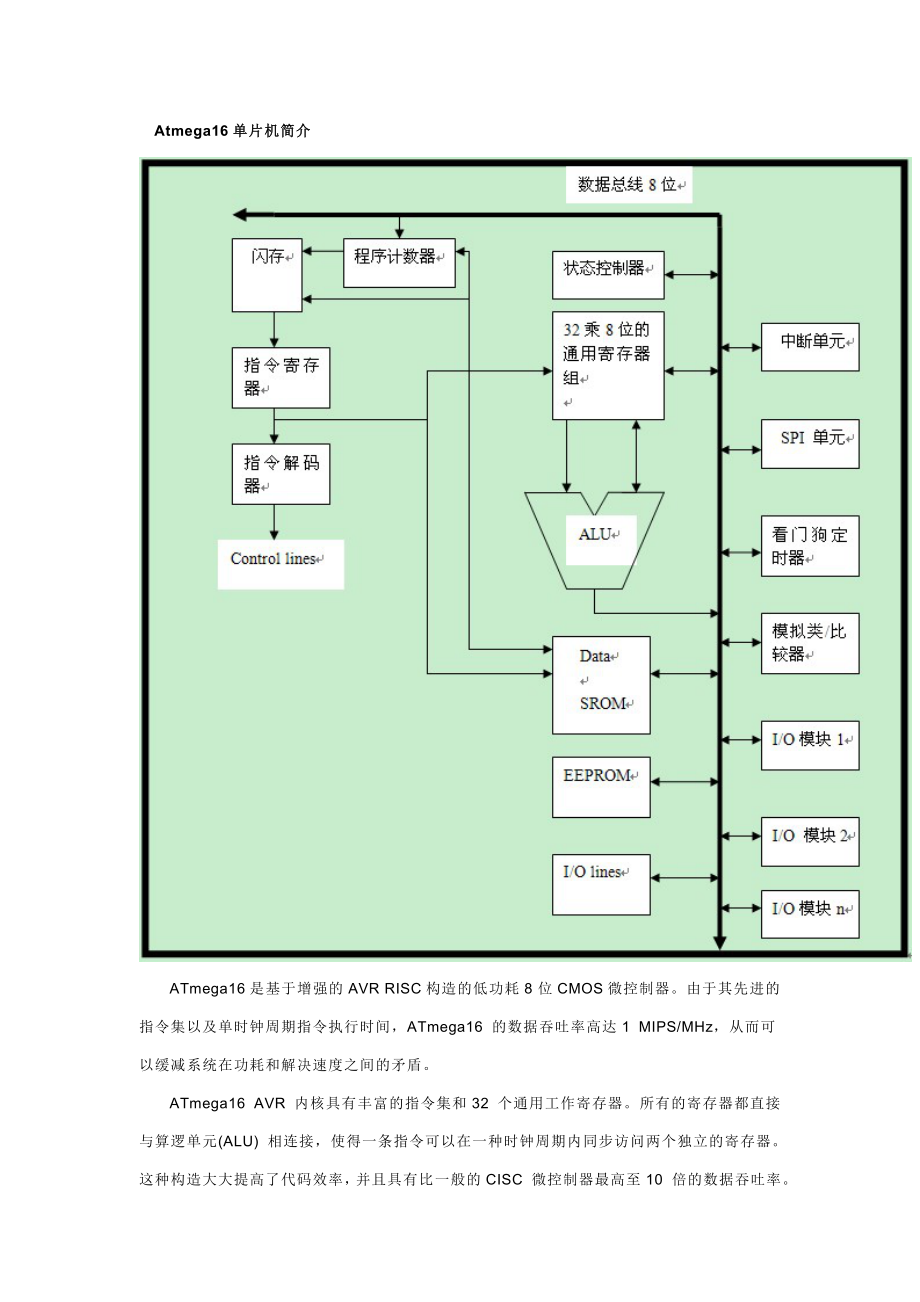

1、Atmega16单片机简介 ATmega16是基于增强的AVR RISC构造的低功耗8 位CMOS微控制器。由于其先进的指令集以及单时钟周期指令执行时间,ATmega16 的数据吞吐率高达1 MIPS/MHz,从而可以缓减系统在功耗和解决速度之间的矛盾。 ATmega16 AVR 内核具有丰富的指令集和32 个通用工作寄存器。所有的寄存器都直接与算逻单元(ALU) 相连接,使得一条指令可以在一种时钟周期内同步访问两个独立的寄存器。这种构造大大提高了代码效率,并且具有比一般的CISC 微控制器最高至10 倍的数据吞吐率。 ATmega16 有如下特点:16K字节的系统内可编程Flash(具有同步

2、读写的能力,即RWW),512 字节EEPROM,1K 字节SRAM,32 个通用I/O 口线,32 个通用工作寄存器,用于边界扫描的JTAG 接口,支持片内调试与编程,三个具有比较模式的灵活的定期器/ 计数器(T/C),片内/外中断,可编程串行USART,有起始条件检测器的通用串行接口,8路10位具有可选差分输入级可编程增益(TQFP 封装) 的ADC ,具有片内振荡器的可编程看门狗定期器,一种SPI 串行端口,以及六个可以通过软件进行选择的省电模式。 工作于空闲模式时CPU 停止工作,而USART、两线接口、A/D 转换器、SRAM、T/C、SPI 端口以及中断系统继续工作;掉电模式时晶体

3、振荡器停止振荡,所有功能除了中断和硬件复位之外都停止工作;在省电模式下,异步定期器继续运营,容许顾客保持一种时间基准,而其他功能模块处在休眠状态; ADC 噪声克制模式时终结CPU 和除了异步定期器与ADC 以外所有I/O 模块的工作,以减少ADC 转换时的开关噪声; Standby 模式下只有晶体或谐振振荡器运营,其他功能模块处在休眠状态,使得器件只消耗很少的电流,同步具有迅速启动能力;扩展Standby 模式下则容许振荡器和异步定期器继续工作。 本芯片是以Atmel 高密度非易失性存储器技术生产的。片内ISP Flash 容许程序存储器通过ISP 串行接口,或者通用编程器进行编程,也可以通

4、过运营于AVR 内核之中的引导程序进行编程。引导程序可以使用任意接口将应用程序下载到应用Flash存储区(ApplicationFlash Memory)。在更新应用Flash存储区时引导Flash区(Boot Flash Memory)的程序继续运营,实现了RWW 操作。 通过将8 位RISC CPU 与系统内可编程的Flash 集成在一种芯片内, ATmega16 成为一种功能强大的单片机,为许多嵌入式控制应用提供了灵活而低成本的解决方案。ATmega16 具有一整套的编程与系统开发工具,涉及:C 语言 编译器、宏汇编、 程序调试器/ 软件仿真器、仿真器及评估板。 2.1.1 ATmega

5、16产品特性 u 高性能、低功耗的8位AVR微解决器 l 先进的RISC 构造 l 131条指令 l 大多数指令执行时间为单个时钟周期 l 32个8位通用工作寄存器 l 全静态工作 l 工作于16MHz时性能高达16MIPS l 只需两个时钟周期的硬件乘法器 l 非易失性程序和数据存储器 l 16K 字节的系统内可编程Flash,擦写寿命: 10,000次 l 具有独立锁定位的可选Boot代码区,通过片上Boot程序实现系统内编程,真正的同步读写操作 l 512 字节的EEPROM,擦写寿命: 100,000次 l 1K字节的片内SRAM l 可以对锁定位进行编程以实现顾客程序的加密 l JT

6、AG 接口( 与IEEE 1149.1 原则兼容) l 符合JTAG 原则的边界扫描功能 l 支持扩展的片内调试功能 l 通过JTAG 接口实现对Flash、EEPROM、熔丝位和锁定位的编程 外设特点 u 两个具有独立预分频器和比较器功能的8位定期器/计数器 l 一种具有预分频器、比较功能和捕获功能的16位定期器/计数器 l 具有独立振荡器的实时计数器RTC l 四通道PWM l 8路10位ADC,8个单端通道,2个具有可编程增益(1x, 10x, 或200x)的差分通道 l 面向字节的两线接口 l 两个可编程的串行USART l 可工作于主机/ 从机模式的SPI 串行接口 l 具有独立片内

7、振荡器的可编程看门狗定期器 l 片内模拟比较器 u 特殊的解决器特点 l 上电复位以及可编程的掉电检测 l 片内通过标定的RC振荡器 l 片内/片外中断源 l 6种睡眠模式: 空闲模式、ADC 噪声克制模式、省电模式、掉电模式、Standby 模式以及扩展的Standby模式 u I/O和封装 l 32个可编程的I/O口 l 40引脚PDIP封装, 44引脚TQFP封装, 与44引脚MLF封装 u 工作电压: l ATmega16L:2.7 - 5.5V l ATmega16:4.5 - 5.5V u 速度级别 l 8MHz ATmega16L l 0-16MHz ATmega16 u ATm

8、ega16L在1MHz, 3V, 25C时的功耗 l 正常模式: 1.1 mA l 空闲模式: 0.35 mA l 掉电模式: 1 A 2.1.2 ATmega16 引脚功能 引脚名称 引脚功能阐明 VCC 电源正 GND 电源地 端口A(PA7.PA0) 端口A 做为A/D 转换器的模拟输入端。端口A 为8 位双向I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸取大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。在复位过程中,虽然系统时钟尚未起振,端口A 处在高阻状态。 端口B(PB7.PB0) 端口B 为8 位双向I/O 口,具有

9、可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸取大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。在复位过程中,虽然系统时钟尚未起振,端口B 处在高阻状态。 端口B 也可以用做其她不同的特殊功能. 端口C(PC7.PC0) 端口C 为8 位双向I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸取大电流。作为输入使用时,若内部上拉电阻使能,端口被外部电路拉低时将输出电流。在复位过程中,虽然系统时钟尚未起振,端口C 处在高阻状态。如果JTAG接口使能,虽然复位浮现引脚 PC5(TDI)、 PC3(TMS)与 PC2(TC

10、K)的上拉电阻被激活。端口C 也可以用做其她不同的特殊功能. 端口D(PD7.PD0) 端口D 为8 位双向I/O 口,具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸取大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电路拉低时将输出电流。在复位过程中,虽然系统时钟尚未起振,端口D 处在高阻状态。端口D 也可以用做其她不同的特殊功能. RESET 复位输入引脚。持续时间超过最小门限时间的低电平将引起系统复位。门限时间见P36Table 15。持续时间不不小于门限间的脉冲不能保证可靠复位。 XTAL1 反向振荡放大器与片内时钟操作电路的输入端。 XTAL2 反向振荡

11、放大器的输出端。 AVCC AVCC是端口A与A/D转换器的电源。不使用ADC时,该引脚应直接与VCC连接。使用ADC时应通过一种低通滤波器与VCC 连接。 AREF A/D 的模拟基准输入引脚。 2.1.3 ATmega16 内核简介 右边为AVR 构造的方框图 为了获得最高的性能以及并行性, AVR 采用了Harvard 构造,具有独立的数据和程序总线。程序存储器里的指令通过一级流水线运营。CPU 在执行一条指令的同步读取下一条指令( 在本文称为预取)。这个概念实现了指令的单时钟周期运营。程序存储器是可以在线编程的FLASH。 迅速访问寄存器文献涉及32 个8 位通用工作寄存器,访问时间为

12、一种时钟周期。从而实现了单时钟周期的ALU 操作。在典型的ALU 操作中,两个位于寄存器文献中的操作数同步被访问,然后执行运算,成果再被送回到寄存器文献。整个过程仅需一种时钟周期。 寄存器文献里有6 个寄存器可以用作3 个16 位的间接寻址寄存器指针以寻址数据空间,实现高效的地址运算。其中一种指针还可以作为程序存储器查询表的地址指针。这些附加的功能寄存器即为16 位的X、Y、Z 寄存器。 ALU支持寄存器之间以及寄存器和常数之间的算术和逻辑运算。ALU也可以执行单寄存器操作。运算完毕之后状态寄存器的内容得到更新以反映操作成果。 程序流程通过有/ 无条件的跳转指令和调用指令来控制,从而直接寻址整

13、个地址空间。大多数指令长度为16 位,亦即每个程序存储器地址都涉及一条16 位或32 位的指令。 程序存储器空间分为两个区:引导程序区(Boot 区) 和应用程序区。这两个区均有专门的锁定位以实现读和读/ 写保护。用于写应用程序区的SPM 指令必须位于引导程序区。 在中断和调用子程序时返回地址的程序计数器(PC) 保存于堆栈之中。堆栈位于通用数据SRAM,因此其深度仅受限于SRAM 的大小。在复位例程里顾客一方面要初始化堆栈指针SP。这个指针位于I/O 空间,可以进行读写访问。数据SRAM 可以通过5 种不同的寻址模 式进行访问。 AVR 存储器空间为线性的平面构造。 AVR有一种灵活的中断模块。控制寄存器位于I/O空间。状态寄存器里有全局中断使能位。每个中断在中断向量表里均有独立的中断向量。各个中断的优先级与其在中断向量表的位置有关,中断向量地址越低,优先级越高。 I/O 存储器空间涉及64 个可以直接寻址的地址,作为CPU 外设的控制寄存器、SPI,以及其她I/O 功能。映射到数据空间即为寄存器文献之后的地址0x20 - 0x5F。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

相关资源

更多 注册会计师《会计》考试试题强化卷及答案(28)

注册会计师《会计》考试试题强化卷及答案(28)

虚拟现实技术——VRML篇24

虚拟现实技术——VRML篇24

2022年浙江省三类人员安全员B证考试试题押题卷及答案(73)

2022年浙江省三类人员安全员B证考试试题押题卷及答案(73)

2022年广西省安全员B证考试题库试题强化卷(必考题)及答案(第12次)

2022年广西省安全员B证考试题库试题强化卷(必考题)及答案(第12次)

![2022年广西省安全员B证考试题库试题强化卷(必考题)及答案[17]](/Images/s.gif) 2022年广西省安全员B证考试题库试题强化卷(必考题)及答案[17]

2022年广西省安全员B证考试题库试题强化卷(必考题)及答案[17]

2022年云南省建筑施工企业安管人员考试题库押题卷(答案)(第55期)

2022年云南省建筑施工企业安管人员考试题库押题卷(答案)(第55期)

2022年安徽省(安管人员)建筑施工企业安全员B证上机考试题库强化卷(必考题)及答案(第93套)

2022年安徽省(安管人员)建筑施工企业安全员B证上机考试题库强化卷(必考题)及答案(第93套)

2022年上班玩手机检讨书【精品模板】

2022年上班玩手机检讨书【精品模板】

老窖资料制作标准工艺大曲小曲特曲的发酵法

老窖资料制作标准工艺大曲小曲特曲的发酵法

2022江苏省建筑施工企业安全员C2土建类考试题库押题卷及答案(59)

2022江苏省建筑施工企业安全员C2土建类考试题库押题卷及答案(59)