04第四章组合逻辑电路

04第四章组合逻辑电路

《04第四章组合逻辑电路》由会员分享,可在线阅读,更多相关《04第四章组合逻辑电路(26页珍藏版)》请在装配图网上搜索。

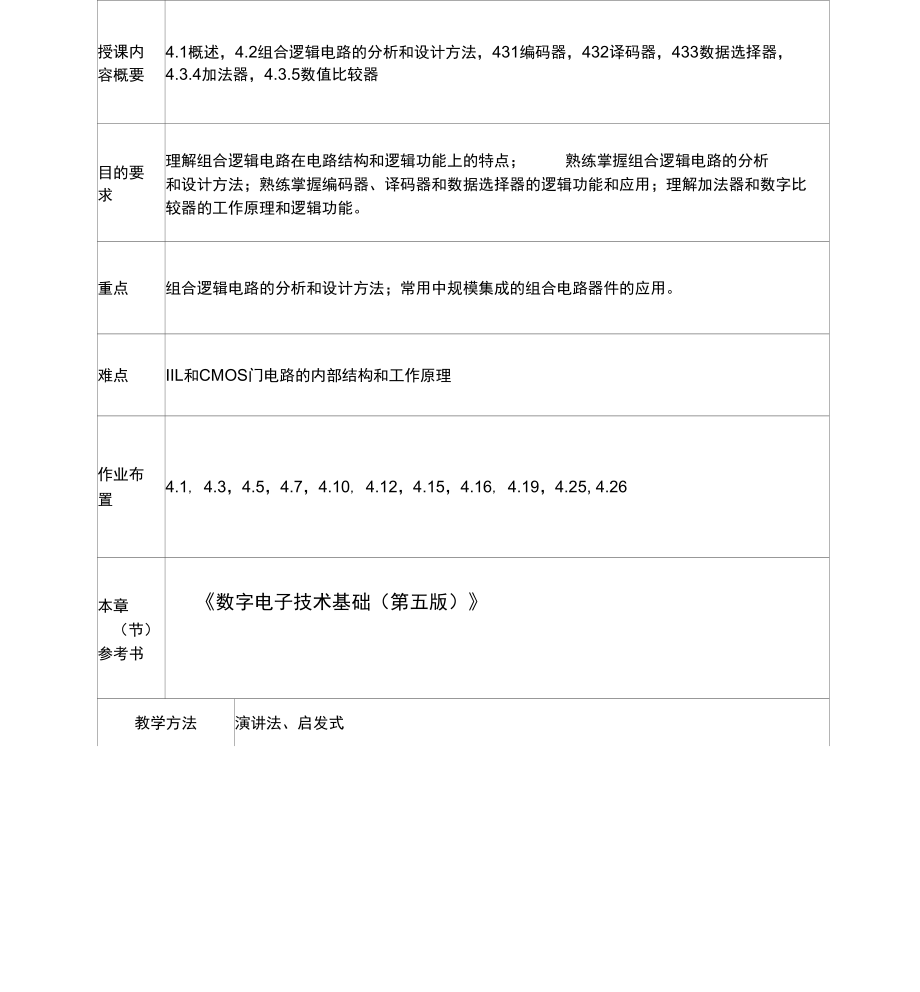

1、授课内 容概要4.1概述,4.2组合逻辑电路的分析和设计方法,431编码器,432译码器,433数据选择器, 4.3.4加法器,4.3.5数值比较器目的要 求理解组合逻辑电路在电路结构和逻辑功能上的特点;熟练掌握组合逻辑电路的分析和设计方法;熟练掌握编码器、译码器和数据选择器的逻辑功能和应用;理解加法器和数字比 较器的工作原理和逻辑功能。重点组合逻辑电路的分析和设计方法;常用中规模集成的组合电路器件的应用。难点IIL和CMOS门电路的内部结构和工作原理作业布置4.1, 4.3,4.5,4.7,4.10, 4.12,4.15,4.16, 4.19,4.25, 4.26本章(节) 参考书数字电子技

2、术基础(第五版)教学方法演讲法、启发式主要教具多媒体课件备注授课过程及内容备注第四章组合逻辑电路 4.1概述1 逻辑电路的分类(1)组合逻辑电路(简称组合电路);(2)时序逻辑电路(简称时序电路)。2、组合逻辑电路的特点(1)功能特点:任一时刻的输出状态仅仅取决于同一时刻的输入状态,而与前时刻的状态无关。(2)结构特点:不包含记忆单元,即存储单元。3、组合逻辑电路的描述如图所示:组合逻辑电路输出信号用一组逻辑函数表示为:斗丫JY(X、X、(X、X、Xn)X)fn(X1、X2、Xn)4.2组合逻辑电路的分析和设计方法一、分析方法分析就是已知电路的逻辑图,分析电路的逻辑功能。分析步骤如下:(1)根

3、据已知的逻辑图,从输入到输出逐级写出逻辑函数表达式。(2)利用公式法或卡诺图法化简逻辑函数表达式(最简与或表达式)(3)列真值表。(4)确定其逻辑功能。例1、分析下图组合逻辑电路的功能。解: (1) Y AB BC AC(2)化筒:Y=AB+BC+AC表:ABC0 0 000 0 100 1 000 1 111 0 001 0 111 1 011 1 11(3)列真值练习:分析如图所示组合逻辑电路的功能(4)由真值表知:若输入两个或者两个以上的1, 输出丫为1功能:在实际应用中可作为多数表决电路 使用。I &L=J |A & 丫1 &- & Ys obI_r二、设计方法设计就是已知实际逻辑问题

4、,设计实现该功能的最简电路。设计步骤如下:(1)根据实际逻辑问题进行逻辑抽象,即确定输入、输出变量的个数,并对 它们进行逻辑赋值(即确定0和1代表的含义)。(2)根据逻辑功能列出真值表,求出逻辑函数表达式。(3)选定逻辑器件。1、若选用SSI (小规模门电路),则化简函数表达式,画出实现电路;2、若选用MSI (中规模门电路),则变换函数表达式形式,画出实现电路。例2、 有三个班学生上自习,大教室能容纳两个班学生,小教室能容纳一个班学生。设计两个 教室是否开灯的逻辑控制电路,用SSI门电路实现。要求如下:(1)一个班学生上自习,开小教室的灯。(2)两个班上自习,开大教室的灯。(3)三个班上自习

5、,两教室均开灯。解:(1)逻辑抽象:设输入变量A、E、C分别表示三个班学生是否上自习,1表示上自习,表示不上 自习;输出变量丫、F分别表示大教室、小教室的灯是否亮,1表示亮,表示灭。(2)列真值表:ABCYF0 0 0000 0 1010 1 0010 1 1101 0 0011 0 1101 1 0101 1 111.Y BC AC AB(3)函数表达式:YABC ABC ABC ABCF ABC ABC ABC ABC利用旧若图化简:00-10030100 01 11 1000011110F ABC ABC ABC ABC =A B (4)画逻辑图:ABYCF课堂练习:P179 3.44.

6、3若干常用的组合逻辑电路(MSI)一、编码器(重点:定义、逻辑真值表)1、定义、分类2、实例介绍3、应用1、定义、分类编码:用二进制代码组合表示特定含义的输入对象 而编码器就是实现编码操作的数字电路。分类:(例如文字、数字、符号等(1)按输入、输出的端数不同二进制编码器:2IN) f n(OUT)二一十进制 编码器:10(IN) f n=4(OUT)(2)按照编码方式规则不同普通编码器:每次只允许一个输入对象。优先 编码器:每次允许多个输入对象,但只对优先 级别最高的进行编码。2、实例介绍(1) 3位二进制编码器(也称8/3线编码器,是一普通编码器)T;T1la14. Il I4T,Yi Y1

7、Yd10Q000A0000010000000(110010(*0000I00J0100u0011000U10口0I0000000aQ10L0门Q0门0L01000Q000Q1I1I输入信号高电平有效。写出输出的函数表达式,化简有:L 14 1Y1lY16 17h IJ7II1113 5 7编码器电路图:(2)优先编码器(74LS148)74LS148 是-看74LS148的逻辑图(P141),I |是输入端,Ys :选通输出端0 7Y 02是输出端,还有一些控制端,下面依次介绍一下:编码器工作;s=1,编码器禁止工作。_oS :片选信号,匕=0,编码器工作,但无信yex :扩展端,YEX=O,

8、编码器工作,且有信号输入 芯片的管脚分布图为:IATH74LS148的功能表 P142numg二 2 “匚74LS147 的功能表(P144 表 3.3.3)3、应用:小测验:用与非门设计一个三变量判偶电路。当输入变量中有偶数个1时,输出1;否则 输出为0。、译码器(重点:定义、分类、输出与输入之间的关系)1、定义、分类2、实例介绍3、扩展问题4、应用:用译码器实现逻辑函数1、定义、分类译码:编码的逆过程,即将每一组输入的二进制代码翻译”为一个高、低电平的输出信号。而实现译码功能的数字电路称为译码器。分类:(1)二进制译码器:n (IN) 2n (OUT)2)二一十进制译码器:4 (IN) 1

9、0 (OUT),即将10个BCD代码译成10个高、低 输出信号。(3)显示译码器(BCD 一七段显示译码器):4(IN) 7 (OUT)2、实例介绍(1) 3位二进制译码器(3/8线译码器):74LS1383位二进制译码器的框图为:.-11 -一/VV1 *1. y |F面介绍一 TTL集成译码器74LS138:功能表A.输1ujYi5 + 5,4,A,4*Y.附FiFYsY.师XXK11111111X1XX嵩1111111Ia100011.111111u011u11L111JQuJ0J101111Ja0i11JI10J11111001I1101111A01111n111命1A0)111flI

10、11V1JI11111a输出为低电平有效 根据功能表写出输出的函数表达式:Y0A2A1A0moYiA2AiA0 mY2A2A1A0m2Y7A2A1A0 m故这种译码器也叫做最小项译码器芯片的管脚分布图:=心 |* | | | 心i i H; 三 * 三三U 1ITQ 旺祸,E = A A 二一十进制译码器:74LS142真值表:P150(3)显示译码器(BCD 段显示译码器)数码显示器按显示方式有分段式、字形重叠式、点阵式。其中,七段显示器应用最普遍。七段显示器分为半导体数码管(LED七段显示器)和液晶显示器两种。LED七段显示器2fiJiSEE分为七段,每段都是一个发 光二极管(LED),有

11、共阳 极和共阴极两种接法。abcdefgdp7COM(a)共七段显示器为了显示BCD码,LED显示器外形图为:c1 11c1 (1 4Z2szB-11-+-abcdefgdpdpdCOM(b)共阳极需用显示译码器将代码译成数码管所需的驱动信号显示译码器(BCD 一七段显示译码器):74LS48 以共阴极接法为例:显示译码器led真值表:(高电平有效)集成显示译码器7448:Ai116V ccA2 -1215Yf三个辅助控制端LT、BI /RBO、RBITT _BI/RBO !341413Yg-Ya的功能和用法见P155RBI-5744812aYbA3 一611YcA0,710丫 dGND-18

12、9Ye3、扩展问题用两片3/8线译码器74LS138扩展一个4/16线译码器。P148例3.3.2当 D3=0, 74LS138(1)T作,而 74LS138(2)禁止工作,故将输入 D3D2D1D0 的 0000 0111代码译成zZ ;当D3=1时,74LS138(2)工作,而74LS138(1)禁止工作,将 D3D2D1D0 的 10001111 代码译成 Z8Z15。4、应用:用译码器实现逻辑函数例1、用3/8线译码器74LS138和门电路产生如下多输出逻辑函数丫 1AC4 解:丫 ABC ABC BC,Y 1AC ABC ABC m7m.Y2A BC ABC BC ABC ABC A

13、BC ABC m mm?m3令 A?=A、A 1=B Ao=CJY1 m7 m5 m?m5Y7Y m m m m mm m m Y Y Y Y21347i34?i347电路的接法LS138为:AA2BAiCA。二5iT53Yi丫丫 2374lY ,8丫2& uYi例2、P158例3.3.3 4.3.3数据选择器(重点:定义、输出表达式)定义 实例介绍四、 应用:用数据选择器实现逻辑函数、定义在数字信号的传输过程中,数据选择器(也称多路开关)可以从多路输入选 择一路输出。其功能如图:控制信号、实例介绍(1)双4选1数据选择器:74LS15374LS153中集成了两个四选一数据选择器,其中一个的逻

14、辑图和符号图是:其中,Aj、Ao为控制数据传送的地址输入信号,Di0 D13供选择的四路输入信号,si为 使能端。当宫=1时,禁止数据输入,选择器不工作;当S=0时,允许数据选通,选择器正常工作。当正常工作时,输出表达式为:Y I。),(AAo)Dii(A iA0)D 12(a 1A0Di3由逻辑表达式可列出功能表:输入输出SAiA0Yi1XX0000Di0001Dii010Di2011Di38选1数据选择器:74LS152管脚分布图:输出表达式为:Y (A2AAo)DO (A2AA0)D1 气气勺 (A 2A 1A0)D3(AAA)D (A AA)D(AAA ) D (A A A)D2 i

15、o 421052 1062 1 o 7三、扩展用一片双4选1数据选择器74LS153组成一个8选1数据选择器第三地址输入端使 用使能端,则真值表为:A2AiA丫丫2_七0 0 0Di00 D0DRDi2 0DD20 1 11 0 01 0 11 1 0Di3 00 D200 D2i0 D22DDDD61 1 10 d23d723/输出为高电平有效,输出用或门实现,如图:若输出为低电平有效,贝U输出用与门实现。四、应用:用数据选择器实现逻辑函数例、用8选1数据选择器(高电平有效)实现以下逻辑函数:Z ABC AC ABC解:思路:定义、输出表达式一逻辑函数步骤:(1)写出8选1数据选择器的输出表

16、达式:Y (A2A,A )D (A2AAn)D(A 八小)。(A AAn)D (AA,A )D (AAAn)D (AA(A )Dfi2 I O 02 I 0!2022!032IO42|052!O6(AqA + JD?(2)将逻辑函数向表达式靠(出现的项乘以1,未出现的项乘以0,未出现的变量保留)。令A = A?, B = A1, C = A。,贝 UZ ABC 1 ABC 0 ABC 0 ABC 1 ABC 0 ABC 1 ABC 0 ABC 1Z。画出数据选择器的接线图1 0现令D。=D3=D5=D7=1,D1=D2=D4=D6=0,即可用数据选择器实现逻辑函数A -注:如果数据选择器有使能

17、端,注意其接法434加法器、一位加法器1、半加器半加器是只考虑两个加数本身,而不考虑来自低位进位的逻辑电路。加器的真值表为:ABSCO0000011010101101其中,A、B分别为加数和被加数,是输入变量;S为和,C为进位,是输出变量。由真值表写逻辑表达式:S AB AB, CO=AB画出逻辑图如图所示:(a)(b)(a)逻辑图;(b )逻辑符号2、全加器全加器是完成两个二进制数和相邻低位的进位相加的逻辑电路全加器的真值表为:CIABSCO000000011001010011011001010101110011其中,A和E分别是被加数和加数,CI为相邻低位的进位,S为本位的和,CO为本位

18、的进位。一种全加器(74LS183)的逻辑图和逻辑符号为:(a)1/2逻辑图;(b)逻辑符号二、多位加法器1、串行进位加法器依次将低位全加器进位输出端CO接到高位全加器的进位输入端CI,就组成了多位串 行进位加法器。如图是一个4位串行进位加法器:缺点:运算速度慢2、超前进位加法器74LS283是一集成的4位超前进位加法器。符号图和管脚图如图所示:L*站 D 顷.yhy三、应用:用加法器实现逻辑函数1、 逻辑函数能化成输入变量与常量相加,则可用加法器实现;P168例4.3.72、逻辑函数能化成输入变量与另一组输入变量相加,也可用加法器实现。例1、设计一电路,已知输入为8421 BCD码,要求当输

19、入小于5时,输出为输入数加2;当输入大于等于5时,输出为输入数加4。用4位加法器及基本逻辑门实现。解:按要求写出真值表:A R c n口口 B1B0丫3 丫 2丫1丫0000 003 02 1032101 o1 1 11 u00 0- VD0DAAo 01,0 01 0,0o011nn1000u U 1 1 U1U-4AAA0 - i 0j u -u-1T U0 1 1U u 0 0,001110100100 00100i U 0- U1 0- 0=-0- 0思路:输入均是变量,可将第二组变量用第一组变量来表示,即可实现B2 ABCD ABCD ABCD A BCD A BCDB1 ABCD

20、ABCD ABCD ABCD ABCDBoB30利用卡诺图化简:i B 2=A+BD+BCY A B A B 1 2n4.3.5数值比较器一、一位数值比较器二、多位数值比较器数值比较器就是比较两个二进制数值大小的逻辑电路。、 位数值比较器功能表:1、2、逻辑表达式:utr a1- wA-BAB)=AB, L2( AvB)= AB, L1(A=B)=AB AB3、逻辑图(两种形式):二、多位数值比较器比较的原则:1、先从高位比起,高位大的数值一定大。2、若高位相等,则再比较低位数,最终结果由低位的比较结果决定下面看一 4位数值比较器的真值表:比较输入输出幻b工aibiLE (A=B)s (AXXX100XXX(101日勺Ab?XX100的XX001叶mxt00alblX001l=hl10(1眄=bib.001a3=h3ai=bi(110本章小结1、理解组合逻辑电路在电路结构和逻辑功能上的特点;2、熟练掌握组合逻辑电路的分析和设计方法;3、熟练掌握编码器、译码器和数据选择器的逻辑功能和应用;4、理解加法器和数字比较器的工作原理和逻辑功能。

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 卡通可爱绿色小学生家长会模板课件

- 卡通可爱老师教育教学模板课件

- 卡通可爱幼儿园大班家长会模板课件

- 卡通夏日暑假班会家长会模板课件

- 卡通可爱创意爱情告白求婚婚礼婚庆策划方案模板课件

- 卡通可爱军人动态模板通用模板课件

- 卡通可爱五一劳动最光荣主题班会模板课件

- 卡通可爱小学生常用急救知识模板课件

- 卡通动画小乌龟Franklin_02_02【声音字幕同步】课件

- 卡通儿童预防冬季流感科普宣传模板课件

- 卡通动漫动物人物绘制课件

- 卡通可爱儿童节主题活动策划方案模板课件

- 卡通儿童珍爱生命防溺水主题班会模板课件

- 卡通动漫教育教学课程设计教师说课模板课件

- 身体工作动态静心资料来源Osho的静心与健康若欲详解敬请课件