AtiumDesigner绘图实习报告

AtiumDesigner绘图实习报告

《AtiumDesigner绘图实习报告》由会员分享,可在线阅读,更多相关《AtiumDesigner绘图实习报告(8页珍藏版)》请在装配图网上搜索。

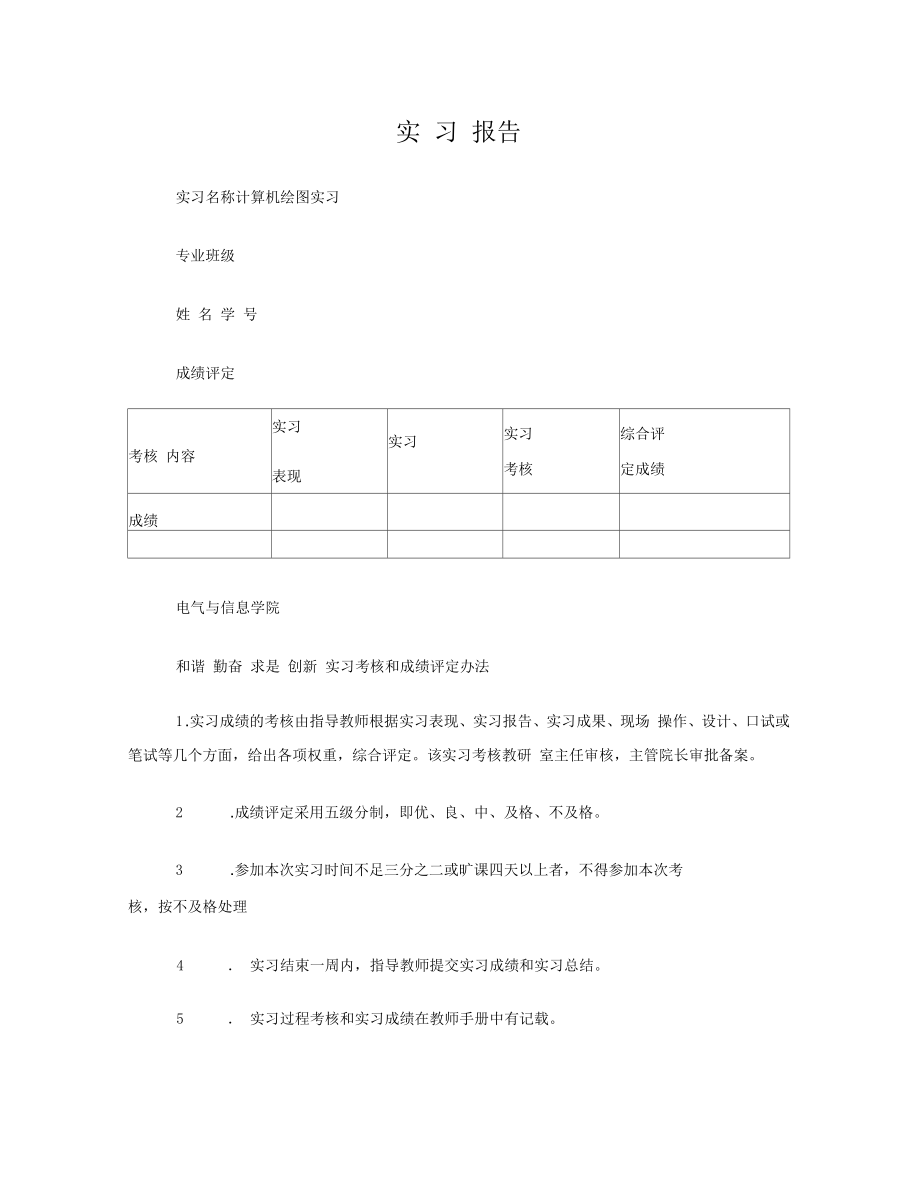

1、实 习 报告实习名称计算机绘图实习专业班级姓 名 学 号成绩评定考核 内容实习表现实习实习考核综合评定成绩成绩电气与信息学院和谐 勤奋 求是 创新 实习考核和成绩评定办法1 .实习成绩的考核由指导教师根据实习表现、实习报告、实习成果、现场 操作、设计、口试或笔试等几个方面,给出各项权重,综合评定。该实习考核教研 室主任审核,主管院长审批备案。2 .成绩评定采用五级分制,即优、良、中、及格、不及格。3 .参加本次实习时间不足三分之二或旷课四天以上者,不得参加本次考核,按不及格处理4 实习结束一周内,指导教师提交实习成绩和实习总结。5 实习过程考核和实习成绩在教师手册中有记载。实习报告内容实习报告

2、内容、格式各专业根据实习类别(技能实习、认识实习、生产实 习、毕业实习等)统一规范,经教研室主任审核、主管院长审批备案。6 : 1. 实习任务书和实习指导书在实习前发给学生,实习任务书放置在实习报告封面后和正文目录前。2. 为了节省纸张,保护环境,便于保管实习报告,统一采用 A4 纸,实习报 告建议双面打印(正文采用宋体五号字)或手写,右侧装订。10/11 学年第一学期计算机绘图实习任务书一、 实习目的能够应用绘图软件把所学专业课程中的各种元器件以及电路图熟练绘制;熟练应用软件创建新的元器件以及创建元件库;掌握计算机绘图的方法、技巧;提高学生计算机绘图的综合能力,使学生在完成设计能力基础上,提

3、升计算机绘图水平,培养学生的综合设计以及绘图能力。二、 实习内容掌握绘图软件设计基础、设计环境、绘图环境、文件管理概述;掌握原理图设计基础、设计步骤、设计工具;掌握原理图设计、装载元件库、放置元件及位置调整;掌握高级绘图知识、元件编辑、绘图工具、电气法则测试;掌握制作元件与建立元件库、元件库的编辑管理;掌握生成报表及出图、网络报表、元件列表、打 印出图、pcb设计等内容。三、时间安排星期具体内容四设计基础、设计环境、原理图设计基础、设计工具五电路原理图设计环境、参数设置、元器件编辑、高级绘图知识一绘制实际电路图、制作元件、建立元件库二绘制实际电路图、生成报表三成图、原理图输出、Pcb窗口管理及

4、基本操作四Pcb编辑环境及pcb设计五上机考试、整理实习日志以及撰写实习才给四、实习要求实习期间,严格遵守课堂纪律,不许迟到、早退;实习期间,学习态度端 正,认真上机练习;熟练掌握绘图软件的应用方法;完成实习日志及实习报告各一 份,内容充实,写出实习的体会与收获;实习报告打印成文。目录第一章Altium系统 1第二章原理图 3、原理图设计二、原理图元件库及其设计4第三章 PCB 图 4一、PC凯件设计4二、PC凯件库元件设计5第四章 问题及解决方法6一、排除器件封装找不到的这种问题 6二、在 Altium Designer 中编辑集体整批修改功能第五章 实习作业7一、电阻、电容、电感电路7二、

5、接触式防盗报警点电路8三、电子琴电路9四、开发板电路11实习心得 14第一章 Altium 系统Altium (前称 Protel International Limited )有限公司由 Nick Matrin 于 1985 年在塔斯马尼亚岛的霍巴特成立,用来开发基于计算机的软件来辅助进行印制电路 板(PCB设计。公司所推出的第一套 DO9S本PCBS计工具被澳大利亚电子行业 广泛接受,至U 1986年中期,Altium公司开始通过销售商向美国和欧洲出口设计 包。随着PCBS计包的成功,Altium开始扩大产品范围,所生产的产品包括原理 图输入、PCB自动布线以及自动PC机件布局软件。Pro

6、tel是目前EDA亍业中使用最方便,操作最快捷,人性化界面最好的辅助 工具。在中国用得最多的EDAX具,电子专业的大学生在大学基本上都学过 protel 99se ,所以学习资源也最广,公司在招聘新人的时候用Protel新人会很快 上手。Altium 声称中国有73%勺工程师和80%勺电子工程相关专业在校学生正在 使用其所提供的解决方案,而目前正版率只有3位右。2008年夏天,Altium 公司对Altium Designer 6 进行了 8次大的改进的基 础上,推出了 Altium Designer Summer 08 。 Altium Designer Summer 08 (简 称:AD刁

7、 将ECADF口 MCA画种文件格式2合在一起,Altium在其最新版的一体 化设计解决方案中为电子工程师带来了全面验证机械设计(如外壳与电子组件)与电气特性关系的能力。还加入了对 OrCADf口 PowerPCB勺支持能力。Altium Designer Summer 08 在FPGAT发方面有以下主要特点。(1)支持不依赖于FPGAT商即各个厂商通用的数字系统开发。Altium Designer Summer 08 支持 NanoBoard开发器。NanoBoard开发器标准配置有两块可以选择的FPGAf板,分别为:Altera Cyclone(EP1C12-Q240C7和Xilinx S

8、partan IIE(XC2s300E-PQ208C,由于各个厂家不同芯片引脚有些不同, Altium Designer summer 08 提供了一个可以定义引脚之间连接的约束文件(Constrain Files ),可以定义不同FPGAW PCB上的引脚对应关系。这样就可在 NanoBoard上将设计好的FPG般辑关系换烧到不同的厂家生产的不同系列的FPGA上;就可以依赖于不同厂商的FPGAM进行开发,这一点在实际开发中有很大的好 处。Altium Designer summer 08 实现了跨厂家 FPGA计,以前 FPGA一个厂 家每一个系列的FPGAg计都需要有专门对应的下载工具,但

9、是现在AltiumDesigner summer 08 克服了这种麻烦,实现了不受芯片厂家型号约束的设计方 法。( 2)丰富的原理图库,有大量的预综合元件,包括处理器。在原理图库里有大量预综合的元器件,设计者可以调用到FPG般计上。包括很多 IP 模块可以直接调用。有大量免费使用的 IP 库可以放心使用。在设计中需要的元件基本上都可以在IP库里找到,包括51核和DS暇块等。这给IP资源复用( IP Reuse )带来了很大的方便。IP 资源复用( IP Reuse )是指在集成电路设计过程中,通过继承、共享或购买所需的智力产权内核,然后再利用EDAX具进行设计、综合和验证,从而加速流片设计过程

10、,降低开发风险。 IP Reuse 已逐渐成为现代集成电路设计的重要手段,在日新月异的各种应用需求面前,超大规模集成电路设计时代正步入一个IP整合的时代。Altium Designer summer 08 把FPGAS计上升到IP核上来,可以不用以前 的HDL语言进行描述。这就降低了 FPGAg计的门槛。3)在工程的设计和调试阶段都支持原理图导向设计方法。开发系统提供原理图设计,在设计阶段可以方便模块之间的连接;在调试阶 段可以很清楚地看出各模块之间的逻辑关系,方便调试。以FPGM核心的PLD产品是近几年集成电路中发展得最快的产品。随着 FPGA4能的高速发展和设计人员自身能力的提高,FPGA

11、等进一步扩大可编程芯片的领地,将复杂专用芯片挤向高端和超复杂应用。随着处理器以 IP 的形式嵌入到 FPG冲,ASIC和FPGAi间的界限将越来越模糊,未来的某些电路板上可能只有这 两部分电路:模拟部分(包括电源)和一块FPGA5片,最多还有一些大容量的存储器。由于芯片设计的复杂性和产品面市时间对于保证终端市场的成功率至关重 要,设计师不断寻求缩短设计周期的方法,以及更有效的设计方式。随着我们步入 系统级芯片时代,利用 IP 内核和可编程逻辑进行设计复用显得日趋重要。( 4)丰富的虚拟仪器。虚拟逻辑分析仪、虚拟频率发生器、频率计数器、 I/O模块、ROMS真器,为 嵌入式系统开发提供很大的便利

12、。虚拟仪器可以对FPGAI面的模块或模块与模块之间的逻辑关系进行测试检验。(5)为了方便在FPGAt设计嵌入式系统,Altium Designer 6.0完全综合了 Altium独特的基于FPGA-现场设计开发板NanaBoard (Nano-levelBreadoard)和一系列的混合到原理图层的 FPG的理设备。一旦设计被综合并下载 到NanaBoard,设计者就可利用JTAG!信技术对任何核进行通信和控制。JTAG是 Joint Test Action Group的缩写,是一个国际标准(IEE 1149.12001) o是为了测试PCB开发的。利用JTAG可以对芯片进行边界扫描仿真。但是

13、 边界扫描仿真器不能提供真实的路径,因为JTAG逻辑没有通向内部地址和数据线单元。一般的JTAG仿真不能看到内部的逻辑情况。而 Altium Designer 6.0 利用 其软链一一Nexus链,可以使用虚拟仪器看清 FPGA勺内部构造并对其进行调试。 在开发调试过程中,可以很方便地看清楚FPG秋部的情况,也可以实时地观察FPG验生的情况,而且在Altium Designer 6.0平台上可以看到FPGA!面烧写进去的模块。( 6)支持软硬件并行开发,克服以往嵌入式系统软硬件开发的串行开发形式中的缺点。这种方法必将成为以后 FPGAF发的主流方法。传统的嵌入式开发流程是:系统级设计-PCB8硬件制作-硬件调试-嵌入 式软件开发-软件调试-整个系统的软硬件综合调试,发现问题后再从流程开始检 查调试。这是一个串行的开发流程,造成的问题是一个系统开发时间过长和调试不方便,发现问题再修改会很麻烦。现在很多嵌入式开发存在的问题是,在硬件开发阶段,那些软件开发工程师无从下手,非得等硬件PCB做出来才可以基本进行开发,从而浪费了人力和时间。而Altium Designer summer 08 提供了一个软硬件并行的开发方法。当系统级设计完成以后,PCBK硬件工程师可以进行制作板子,嵌入式软件工程师可以进行芯片级的嵌入式软件开发,而到最后调试时出现问题可以很方便地进行软硬件各自的修改。继续阅读

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。