试验三简易放大器

试验三简易放大器

《试验三简易放大器》由会员分享,可在线阅读,更多相关《试验三简易放大器(7页珍藏版)》请在装配图网上搜索。

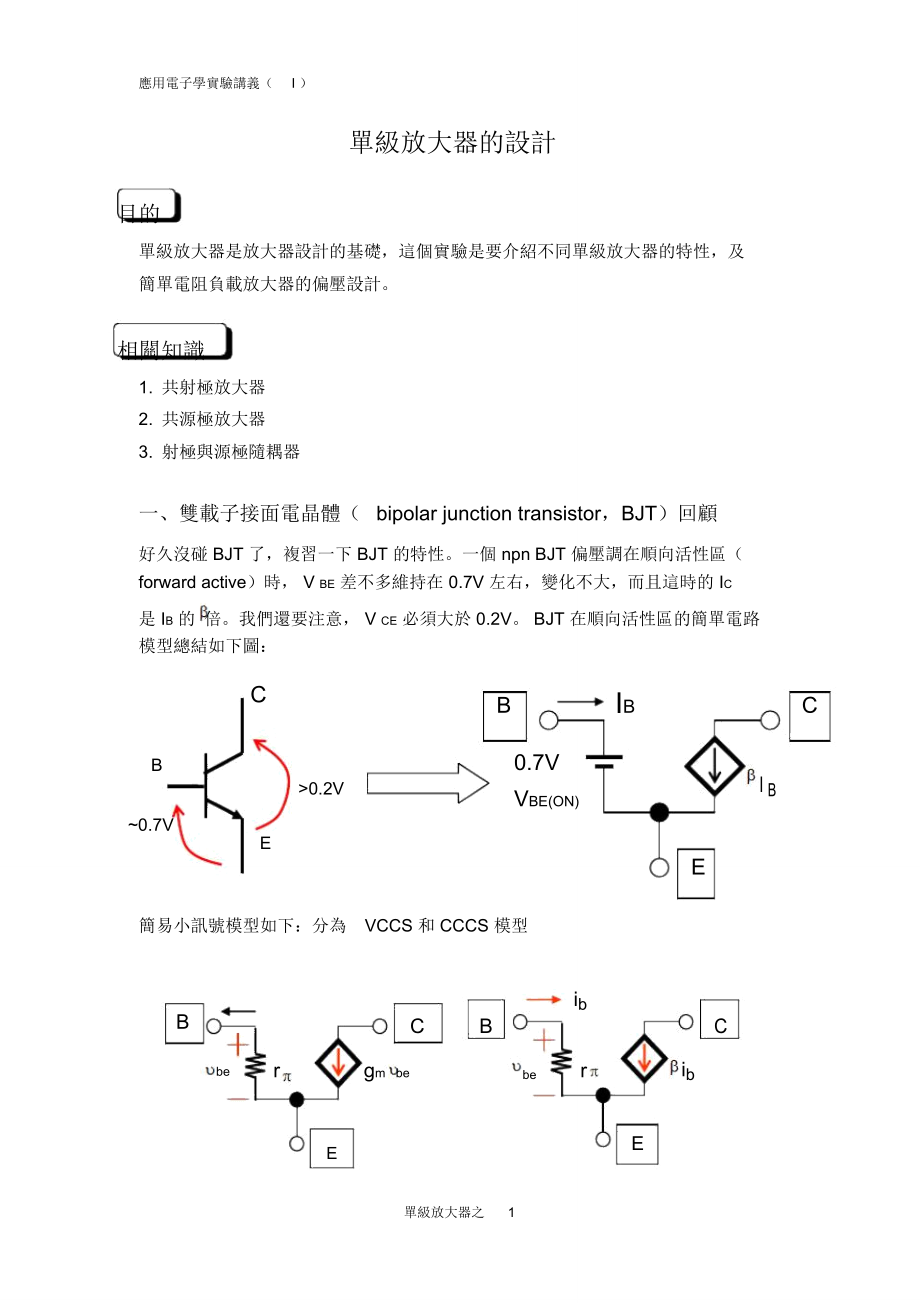

1、應用電子學實驗講義(I )單級放大器的設計目的單級放大器是放大器設計的基礎,這個實驗是要介紹不同單級放大器的特性,及簡單電阻負載放大器的偏壓設計。相關知識1. 共射極放大器2. 共源極放大器3. 射極與源極隨耦器一、雙載子接面電晶體(bipolar junction transistor,BJT)回顧好久沒碰 BJT 了,複習一下 BJT 的特性。一個 npn BJT 偏壓調在順向活性區( forward active)時, V BE 差不多維持在 0.7V 左右,變化不大,而且這時的 IC是 IB 的 倍。我們還要注意, V CE 必須大於 0.2V。 BJT 在順向活性區的簡單電路模型總結

2、如下圖:CBIBCB0.7VI B0.2VVBE(ON)0.7VEE簡易小訊號模型如下:分為VCCS 和 CCCS 模型BbeCBibCrgm beberibEE單級放大器之1應用電子學實驗講義(I )二、共射極放大器( Common-Emitter Amplifier )下面我們利用這個簡單的BJT 模型瞭解右圖電路的操作:1. 靜態偏壓分析這是一個標準的four-resister bias circuit ,R1和 R2 將電晶體 Q1 偏壓在順向活化區,基極的靜態偏壓約為 V B=VCCR2/(R1 +R2),這裡假設 IB 很小,不影響 V B 之偏壓值。射極的偏壓V E 約為V B-

3、0.7V ,射極的靜態電流IE=V E/RE,集極電流 I C=IE /( +1) I E(通常1)。 C1 為阻隔電容( blocking capacitor),使的直流部份影響。2. 功能分析假如在 Vin 輸入交流訊號V ,而 C1 對 V 可視為短路,因此VB= V,又射極的電壓會隨 V B 變化, V E= V B= V,若輸出訊號由射極接出,則此電路為一射極隨耦器( emitter follower ),類似的電路在上學期已經測量過。假如輸出是由集極接出呢?這裡我們看一下 VC 多大。 IC IE= VE/RE= V/R,又V=V-I R,V=-RCI,故ECCC CCCCV=V(

4、-R/R )。(式 3-1)CCE因 此這 個電 路 可視 做一 個放 大器 (稱 做共 射極 放大 器, common-emitter amplifier ),放大率 A V =-RC/RE,負號代表輸出訊號的相位和輸入差了 180 。三、射極接地放大器(Grounded-Emitter Amplifier )假如上面放大器電路中RE=0, A V =-?不太可能吧?問題出在推導式3-1 時,我們假設電晶體在forward active 時 V BE 固定在 0.7V,不受 IC(或 I E)影響,即有IC 但無V BE。事實上,由Ebers-Moll模型可知I CI SeV BE /25m

5、V (在 forward active 時),IC/V BE =(1/25mV) I S eVBE /25mV單級放大器之2應用電子學實驗講義(I )=(1/25mV)I C,我們再定義 reVBE / IC,那麼re25。(式 3-2)I C in mA現在來處理RE=0 的情形。由上電路圖可知V BE = V B= V , I C= V BE/re,VC=-RC IC=-RCVBE/re=V(-R C/re),放大率 A V= V C/ V=-R C/re。注意 re 是 I C 的函數,這樣會使得A V 和輸出訊號大小有關,導致非線性失真(nonlineardistortion)。假如把

6、 re 的效應考慮進去,前面共射極放大器的放大率A V=-RC /(RE+re),RE 可使re 所造成的非線性失真減小 ,但同時 |AV|也減小。同理射極隨耦器的 A V 不再是 1,而是 RE/(RE+re)。四、共源極放大器( Common-Source Amplifier )共源極放大器的原理可參閱前面實驗的補充教材,這裡僅簡單介紹一下。電路如右圖, FET 的靜態偏壓應設計在飽和(或恆流)區,其傳輸特性為ID =IDSS=k(V GS-V t)2/2。(式 3-3)互導 gm 定義為 ID/ V GS,故gm=k(V GS-V t)=(2k I D )1/2(式 3-4)為 V GS

7、 或 ID 的函數。此放大器的放大率AV =-gmRD ,由 RD 控制。RS 用來穩定直流偏壓 ,C2 讓交流訊號看到一個接地的源極。V GS 被偏壓在 - IDRS。五、源極隨耦器( Source Follower)源極隨耦器以前已經量測過,電路如右圖,輸出訊號由源極接出。 C2 要拿掉。ID = IS=gm V GS=gm( V G- VS),又 I S= V S/RS,兩式合併可得AVVSgm RSVGgm RS1RSRS1/ g m(式 3-5)單級放大器之3應用電子學實驗講義(I )六、共基極(閘極)放大器(Common-Base/Gate Amplifier)我們可以利用前面提到

8、的four-resistor bias circuit 設計共基極 /閘極( CB/CG)放大器的直流偏壓,但在基極或閘極必須有一夠大的電容接地,確保在AC 訊號的頻率範圍基極 /閘極是接地的。放大器的輸入是射極/源極,輸出是集極 /汲極。假如不考慮輸入的負載效應 ,此類放大器的增益為gmRC/R L(gmRD/R L),不反相。這種放大器的高頻頻率響應遠較共射極放大器好。BJT 電晶體的射極輸入阻抗為 re25,相當的小。假如訊號源的輸出阻I C in mA抗稍微大一點的話,負載效應就相當嚴重,訊號會變成r /(R+r )倍。esource e對 FET 而言,源極的情形也類似,但輸入阻抗改

9、為1/gm。程序 1射極接地放大器( Grounded-Emitter Amplifier )1. 線路圖如上,接好後先檢查電晶體 E、B、C 三極之直流靜態偏壓的電壓值,推算出電晶體各接腳的直流電流,確定電晶體是在forward active。2. Vin 用一個頻率為 10kHz 之三角波輸入,振幅調到使 V out 之波形剛好不被削截 ,這時的輸出波形式不是有些像 “穀倉頂 ”或 “拱窗 ”,如下圖。請把你所得到的圖記錄下來。VoutVcctime注意! V in 的振幅可能會需要很小,假如你訊號產生器上的AMPL鈕轉到MIN還不夠小到讓 V out 不產生削截的話,記得“ PULL”此

10、鈕,輸出會衰減20dB。AMPL單級放大器之4-20dB應用電子學實驗講義(I )PULLMINMAX3. 現在將電路中的 C2(22 F)移去,將 Vin 之振幅增大(這時 |AV |小很多),觀察 Vout 之波形,失真是不是小很多?記錄 V in 和 V out 振幅,計算增益大小(注意相位)。4. 將 C2 接回去,將 V in 之振幅調到最小(記得 PULL-20dB ),由 V out 和 V in 之振幅比求得 A V ,和你預測的值( -RC/re)一樣嗎?2共射極放大器的輸入及輸出阻抗1.程序 1 的電路若沒有C2,請你設計出一套方法測出此放大器的輸入(Zin )及輸出阻抗(

11、 Zout)。提示:圖 (a) 為放大器的等效電路。圖(b) 顯示在輸入端先串接一個大小適當的RS,觀察RS 所造成V out的衰減( V outA V V S Z in )即可得出 Z in。圖 (c) 顯示在輸出接一適當之電阻RL(中間必須串接Z inR SRL 所造成 V out 的衰減( V outA VVSRL一阻隔電容以免影響放大器之偏壓),觀察)即可得Z outR L出 Zout。2. C2 加上去,測量在 10kHz 的輸入和輸出阻抗。3共源極放大器( Common-Source Amplifier )單級放大器之5應用電子學實驗講義(I )1. 電路圖如右,RD=4.7k 。

12、先將輸入接地(即Vin =0),測量 FET 的靜態偏壓點,包括V G、VS 和 VD,I D 可由 VS/RS 求得。電晶體在飽和區嗎?2. Vin 用一個頻率為 10kHz 之三角波輸入 ,振幅調到使 V out 之波形剛好不被削截,觀察他失真的情形。3. Vin 用 1kHz 的正弦波輸入,振幅調得不使 Vout 波形失真。記錄 V in 和 V out 的振幅及相位,計算 A V。注意!請一定要用探針的x10 檔。4. RD 分別用 10k 和 15k 代替,重複步驟 1 到 3。5. 利用和程序 2 相同的方法測量此放大器的輸入及輸出阻抗。6. 將源極的電容移除,重複步驟 1 到 3

13、。 4共基極放大器( Common-Base Amplifier)1. 這裡我們要測試一個單電源的共基極放大器,電路圖在下一頁。電容找到接近的值即可,注意極性。注意觀察一下,他偏壓的方式就是典型的 four-resistor biascircuit 。檢查各極的直流偏壓,電晶體是不是在forward active? IC 是多大?2. 為了避免輸入的負載效應,訊號在進入放大器前,先加一個利用運算放大器 uA741 接成的 buffer。訊號頻率用100kHz,振幅調小到輸出沒有明顯的失真(可以用三角波試試)。求出放大率。3. 利用程序 2 的方法,量出此放大器的輸入和輸出阻抗。記號測輸入阻抗時

14、,要利用 buffer。5共閘極放大器( Common-Gate Amplifier )單級放大器之6應用電子學實驗講義(I )1. 右圖是一簡單 CG 的 JFET 放大器電路圖,偏壓方式較 BJT 簡單。注意電容極性。先測一下各極的直流電壓。要確定 JFET 在飽和區很容易,你可以調整 V DD,由 0V 開始慢慢增加,用 DVM觀察 1k 電阻兩端的電壓。當V DD 加到此電壓不太變化時,JFET 就已經進入飽和區。量出V GS,V DS 和 I D。2. 為了避免輸入的負載效應 ,訊號在進入放大器前,先加一個利用運算放大器 uA741 接成的 buffer。訊號頻率用10kHz,振幅調

15、小到輸出沒有明顯的失真(可以用三角波試試) 。求出放大率。3. 利用程序 2 的方法,量出此放大器的輸入和輸出阻抗。記號測輸入阻抗時,要利用 buffer。問題與討論1. (a)計算程序 1 電路中 BJT 的靜態操作點,和你的實驗值比較。(b)解釋在步驟 2 所得之輸出波形。(c)為什麼將 C2 移去會使得失真減小?(d)計算有 C2 及沒有 C2 時之 A V ,和實驗值比較。(e)利用 PSPICE 模擬你的結果。2. 仔細說明你在程序 2 測量輸入輸出阻抗的方法,還有結果。3. 由程序 3 的實驗結果求 FET 的 gm。和你在以前實驗測出來的結果比較。4. 分析程序 4 的放大器,和你測量的結果是否一致?並做 PSPICE 模擬。5. 分析程序 5 的放大器,和你測量的結果是否一致?並做 PSPICE 模擬。6. 程序 5 中的電路中,假如改變 RD 為 5k ,I D 會不會改變?放大率呢?做PSPICE模擬。單級放大器之7

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。