数字电路基础知识

数字电路基础知识

《数字电路基础知识》由会员分享,可在线阅读,更多相关《数字电路基础知识(22页珍藏版)》请在装配图网上搜索。

1、数字电路基础知识1、逻辑门电路(何为门)2、真值表3、卡诺图4、3线-8线译码器的应用5、555集成芯片的应用一.逻辑门电路(何为门)在逻辑代数中,最基本的逻辑运算有与、或、非三种。每种逻辑运算代表一种函数关系,这种函数关系可用逻辑符号写成逻辑表达式来描述,也可用文字来描述,还可用表格或图形的方式来描述。最基本的逻辑关系有三种:与逻辑关系、或逻辑关系、非逻辑关系。实现基本逻辑运算和常用复合逻辑运算的单元电路称为逻辑门电路。例如:实现“与”运算的电路称为与逻辑门,简称与门;实现“与非”运算的电路称为与非门。逻辑门电路是设计数字系统的最小单元。1.1.1与门“与”运算是一种二元运算,它定义了两个变

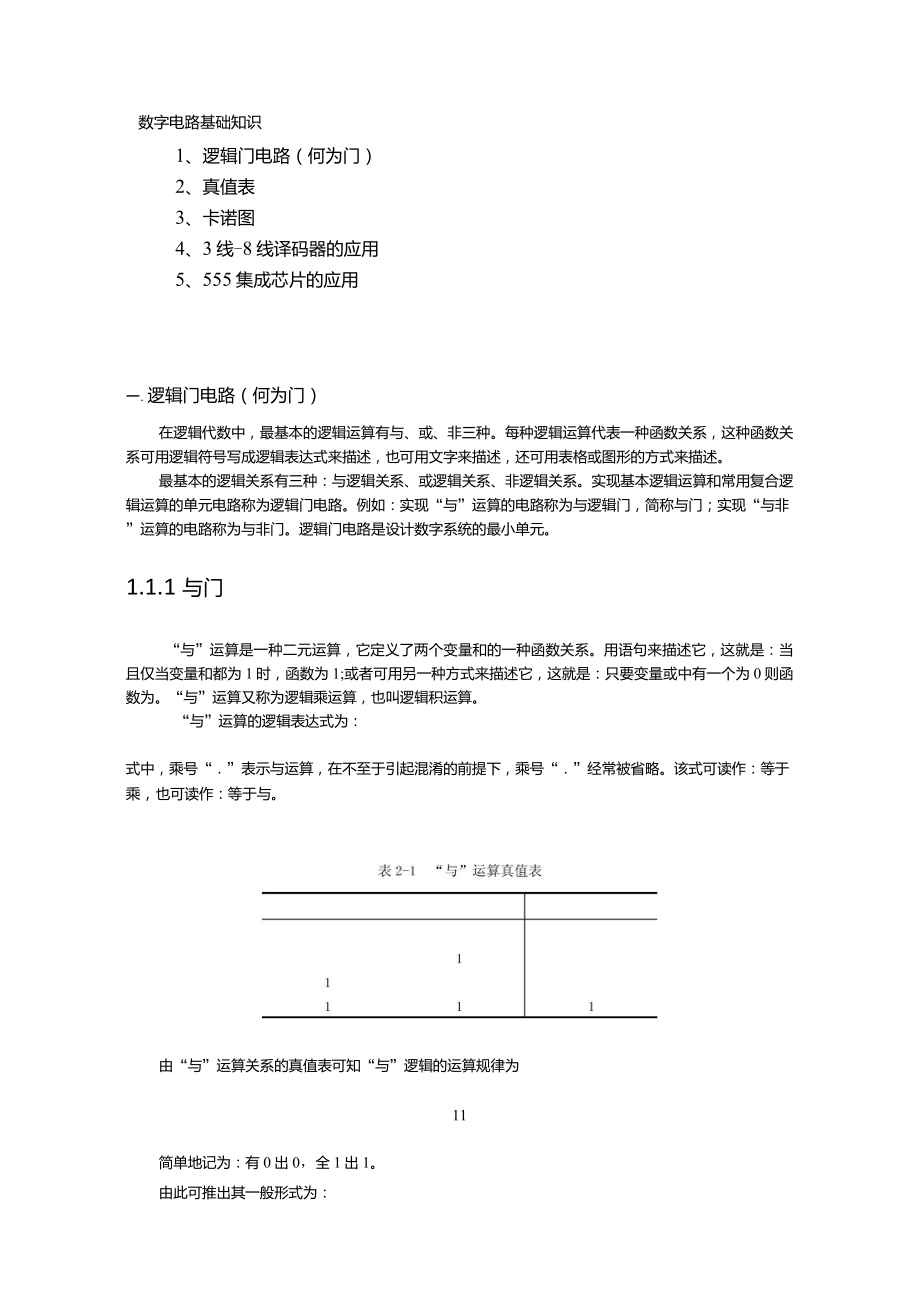

2、量和的一种函数关系。用语句来描述它,这就是:当且仅当变量和都为1时,函数为1;或者可用另一种方式来描述它,这就是:只要变量或中有一个为0则函数为。“与”运算又称为逻辑乘运算,也叫逻辑积运算。“与”运算的逻辑表达式为:式中,乘号“”表示与运算,在不至于引起混淆的前提下,乘号“”经常被省略。该式可读作:等于乘,也可读作:等于与。由“与”运算关系的真值表可知“与”逻辑的运算规律为11简单地记为:有0出0,全1出1。由此可推出其一般形式为:实现“与”逻辑运算功能的的电路称为“与门”。每个与门有两个或两个以上的输入端和一个输出端,图2-2是两输入端与门的逻辑符号。在实际应用中,制造工艺限制了与门电路的输

3、入变量数目,所以实际与门电路的输入个数是有限的。其它门电路中同样如此。ek图2电*门的逻辑符号1.1.2或门“或”运算是另一种二元运算,它定义了变量、与函数的另一种关系。用语句来描述它,这就是:只要变量和中任何一个为1,则函数为1;或者说:当且仅当变量和均为时,函数才为。“或”运算又称为逻辑加,也叫逻辑和。其运算符号为“+”。“或”运算的逻辑表达式为:式中,加号“+”表示“或”运算。该式可读作:等于加,也可读作:等于或。由“或”运算关系的真值表可知“或”逻辑的运算规律为:0+1=1+0=11+1=1简单地记为:有1出1,全0出0。由此可推出其一般形式为:A+1=1实现“或”逻辑运算功能的电路称

4、为“或门”。每个或门有两个或两个以上的输入端和一个输出端,图2-7是两输入端或门的逻辑符号。?k图27或门的逻辑符号1.1.3非门逻辑“非”运算是一元运算,它定义了一个变量(记为)的函数关系。用语句来描述之,这就是:当1时,则函数0反之,当时,则函数1非运算亦称为“反”运算,也叫逻辑否定。“非”运算的逻辑表达式为:式中,字母上方的横线“-”表示非”运算。该式可读作:等于非,或等于反。表23“非”运算真值表由非”运算关系的真值表可知非”逻辑的运算规律为:1简单地记为:有0出1,有1出0由此可推出其一般形式为:A+A=1实现非”逻辑运算功能的电路称为非门”。非门也叫反相器。每个非门有一个输入端和一

5、个输出端。图2-12是非门的逻辑符号。片一12门的逻辑符号1.2.1与非门与”运算后再进行非”运算的复合运算称为与非”运算,实现与非”运算的逻辑电路称为与非门。一个与非门有两个或两个以上的输入端和一个输出端,两输入端与非门的逻辑符号如图2-15所示。其输出与输入之间的逻辑关系表达式为:15与Lt非门的逻辑符号与非门的真值表如表24所示。1.2.2或非门或”运算后再进行“非”运算的复合运算称为“或非”运算,实现“或非”运算的逻图218或非门的逻辑符号辑电路称为或非门。或非门也是一种通用逻辑门。一个或非门有两个或两个以上的输入端和一个输出端,两输入端或非门的逻辑符号如图2-18所示。输出与输入之间

6、的逻辑关系表达式为:或非门的真值表如表2-5所示。1.2.3异或门在集成逻辑门中,“异或”逻辑主要为二输入变量门,对三输入或更多输入变量的逻辑,都可以由二输入门导出。所以,常见的“异或”逻辑是二输入变量的情况。对于二输入变量的“异或”逻辑,当两个输入端取值不同时,输出为“1”;当两个输入端取值相同时,输出端为“0”。实现“异或”逻辑运算的逻辑电路称为异或门。如图2-21R一t图221二输入门的逻辑符号所示为二输入异或门的逻辑符号。相应的逻辑表达式为:其真值表如表2-6所示。1.2.4同或门“异或”运算之后再进行“非”运算,则称为“同或”运算。实现“同或”运算的电路称为同或门。同或门的逻辑符号如

7、图2-24所示。二变量同或运算的逻辑表达式为:?一-k图224同或门|勺逻辑符号其真值表如表2所示。常用逻辑电路逻辑符号对照表01跳思秣flsmw号rr1与n1J血门:i十1114罪n134.旳n廿四菲门-izlZ0-1FLLT11卜予A1119J1曰亠i-真值表真值表定义表征逻辑事件输入和输出之间全部可能状态的表格。在表中通常以1表示真,表示假。真值表是在逻辑中使用的一类数学表,用来确定一个表达式是否为真或有效。完全真值表的作法三个步骤:1、找出已给命题公式的所有变项,并竖行列出这些变项的所有真值组合;2、根据命题公式的结构,由繁到简的依次横行列出,一次只引进一个连接词,直至列出该公式本身;

8、3、依据基本真值表,有变项的真值逐步计算出每个部分的真值,最后列出整个公式得真值。第一种方法以真值表内输出端“为准第一步从真值表内找输出端为“”的各行把每行的输入变量写成乘积形式遇到“”的输入变量上加非号。第二步把各乘积项相加即得逻辑函数的表达式。例已知某逻辑函数的真值表如表表示试写该函数的表达式并化简。解根据上述提示的方法有第一步将输出端为“”的各行写成乘积项即第四行第六行第七行第八行。第二步将各乘积项相加即得逻辑函数表达式并化简駆州RW厲(M训(M+疳x-*T-l-第二种方法真值表内输出端“+”为准“观+第一步从真值表内找输出端为“”的各行把每行的输入变量写成求和的形式遇到“”的输入变量上

9、加非号。第二步把各求和项相乘即得逻辑函数表达式。例2已知某逻辑函数真值表如表2所示试根据此表写出函数表达式并化简。解第一步将输出端为”的各行写成求和形式即第二行第三行。第二步将各求和项相乘即得函数表达式并化简O注在具体使用两种方法时应观察输出端是多还是多以少的为准写函数表达式这样最简单若输出端与出现的次数一样多一般以为准运算较为简单。1BCY0|0000010110001111000101111011111表1T例3已知某函数真值表如表3所示试根据此表写出函数表达式并化简。解采用第一种方法以输出端“”为准时Y=ABC+ABC+ABC=AC+ABC=A(C+BC)=A(C+Bl-AC+AB采用第

10、二种方法以输出端“”为准时Y=(A+B+C)(A+B+C)(A+C+B)(A+B+C)(A-bB+C)=(A+B)(A+B)(A+B+C)A(A+B+CAB+AC显然第二种方法较第一种运算量大且烦琐一些。三卡诺图1.逻辑变量的最小项及其性质1.1最小项定义:设有n个变量,若m为包含全部n个变量的乘积项(每个变量必须而且只能以原变量或反变量的形式出现一次)则称m为该组变量的最小项。如:A、B、C是三个逻辑变量,有以下八个乘积项ABCABCABCABCABCABCABCABC1.特点1每个最小项均含有三个因子(n个变量则含n个因子)(2每)个变量均为原变量或反变量的形式在乘积项中出现一次n个变量有

11、I个最小项1.3最小项的编号最小项常用m表示,下标即为编号。在最小项中,原变量一1、反变量f,所对应的十进制数即为值。以三变量为例或定义为:使最小项为“1的”变量取值组合所对应的十进制数m0m5up3in4KI2JU6iet14爭剽藉T0A333Q二爭删藉O(J(JX001010OU100JOJnoJTI書W速:BCVBCVBCVBCVBCVBGVBCVBC最小项的编号与变量的高、低位顺序有关对于乘积项ABC,若A为高位fm若C为高位fm1.4最小相的性质A、B、C三变量的最小项III0000000IIIJ0000000I0JI0I00000I00II000000I000I0IJ000I000

12、0I0J000I00000I00I0I000000I000I0000000IVBCVBCVBCVBCVBCVBCVBCVBC冃ifBcm1ID5n3m5nr1J-1对)于变量的任意一组取值组合,只有一个最小项的值为12对)于变量的任意一组取值组合,任意两个最小项的积为,(3对)于变量的任意一组取值组合,所有最小项之和(或)为2逻.辑函数最小项表达式如、由一般逻辑式f最小项表达式方法1. 用摩根定律去掉非号多个变量上直至只在一个变量上有非号为止2. 用分配律去除括号,直至得到一个与或表达式3. 配项得到最小项表达式例1二+UJ1=VBaVBC-VBC=VB(C+C)+yBC二实bOTwc)=V+

13、B+VBC=刖(了2Z)二肿+肿+血+讯二爭世C+EEG+權遒筆舁塑二迟c+聖c+亚(c+Q郎睡一皿嘗中二甩+吨?c-迪逼重奧藝龜吐tr=%+NB+C-弋Er(ic)二(迥+xb+c)nb最小项表达式的一种图形表示一卡诺图可利用卡诺图对逻辑函数进行化简用卡诺图表示逻辑函数变量的卡诺图将个逻辑变量的个最小项分别用一个小方块来表示,并按照逻辑上相邻的小方块在几何位置上也相邻的规则排列成的一个方格图形。逻辑上相邻:两个最小项只有一个变量不同。例与变量卡诺图的具体画法:甲OHf10rouin8ijjt:iijttiijt-win30100VB/0001ITTTCDIIJeIU3)三籁書凹半崔囲T州唯3

14、)皿籁喜凹半規厨慣VBVBJni3nPVVBVB0ujdinTF:变量卡诺图画法不唯一。但必须满足循环邻接的原则。即逻辑上邻接的最小项几何位置也邻接。变量卡诺图的特点:个变量函数的图有个小方格,分别对应个最小项;图中行、列两组变量取值按循环码规律排列,使几何相邻的最小项之间具有逻辑相邻性。逻辑函数的卡诺图画法已知逻辑表达式i逻辑表达式化成最小项表达式ii画变量卡诺图iii在最小项表达式中包含的最小项对应的小方块中填;其余填入这样,任何一个逻辑函数就等于其卡诺图中填的那些最小项之和例:把函数化成最小项表达式,再画卡诺图。10II01删IInI00用卡诺图化简逻辑函数+世迪+p)二电5+恥册辿5+

15、迎+V)诩S+确+认中砸+航vg/oo01njo011110J0001320145761112131514108S1110卡.诺图化简的依据:循环邻接性相邻两个最小项求和时,两项并一项并消去一个因子如2)相邻四个最小项求和时,四项并一项并消去两个因子如:3)相邻八个最小项求和时,八项并一项并消去三个因子如用.卡诺图化简逻辑函数的方法和步骤)将相邻的值为“1的”小方块画成若干个包围圈i每个包围圈中必须含有的次方个小方块ii小方块可重复被包围,但每个包围圈中必须含有其他包围圈没有的新小方块iii不能漏掉任何值为的小方块iv包围圈所含的小方块数目要尽可能多包围圈数目要尽可能少,画包围圈的顺序由大f小

16、将每个包围圈中的最小项合并成一项一乘积项(留下相同因子,消去不同因子)对各个包围圈合并成的乘积项求逻辑和fWW二加旷T孑丫rio1rr12)际-8线译码器IB0SB01000)00吧TO驢鞠翱嗣牡誣-昭(籍啊斩軸-)八典00orIIio玳WCd)二刚d丁捋潇y湖ol和斶?)肿豳净逆離團鞭WW1WSOY二Y二些9二E+C+DY二血132268rar38reJ2丁寸13rsrrtoa疋匚屋瓷屋疋建轻吒用与非门组成的3线-8线译码器74LS138线线译码器的功能表I0丁IIIIIIIIr0I0丁I0IIIIII0iI0丁0IIIIII0riI0丁00IIII0IriI00IIIII0IIriI00I

17、0IIaIIIriI000II0IIIIriI0000aIIIIIri玉I玉隹玉IIIIIIri0隹IIIIIIriN1站K1衬I?芒芒pI?劉y牌无论从逻辑图还是功能表我们都可以看到的八个输出引脚,任何时刻要么全为高电平芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。当附加控制门的输入为高电平(=)时,可由逻辑图写出7?=对3对对3=心g=于習甘=曲g=奇3过甘=2庄=对3空甘=朋理=雪吋甘=空(丁茎丄)羞=百3讦甘=竺HT空划=虫庄=VVf=2L-=由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所

18、以也把这种译码器叫做最小项译码器。有三个附加的控制端,当时,输出为高电平(=),译码器处于工作状态。否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3所.示5。这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。带控制输入端的译码器又是一个完整的数据分配器。在图电路中如果把作为数据输入端(同时令),而将作为地址输入端,那么从送来的数据只能通过所指定的一根输出线送出去。这就不难理解为什么把叫做地址输入了。例如当=时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。【例3试用两片线线译码器组成线

19、线译码器,将输入的位二进制代码译成个独立的低电平信号。解:由图可见,仅有个地址输入端。如果想对位二进制代码,只能利用一个附加控制端(当中的一个)作为第四个地址输入端。取第()片的端作为它的第四个地址输入端,如图所示,于是得到两片的输出分别为(23d)rg=D2D3V)tDO38用.两,片接1成3的,4线16线译码器五.555集成芯片的应用555定时器简介:555定时器(时基电路)是一种用途广泛的模拟数字混合集成电路。1972年由西格尼蒂克斯公司(Signetics)研制;设计新颖、构思奇巧,备受电子专业设计人员和电子爱好者青睐;它可以构成单稳态触发器、多谐振荡器、施密特触发器和压控振荡器等多种

20、应用电路。555定时器的工作原理555定时器电路框图555定时器符号图从5551TJjA空+71+IDrYj麓三旦|0W叢同县星回1. 555定时器有两个阈值(Threshold)2. 输出端为低电平时三极管TD导通,管TD截止,如果7脚接一个上拉电阻,拉电阻时,输出状态与3脚相同。电平,分别是1/3VCC和2/3VCC;7脚输出低电平;输出端为咼电平时三极7脚输出为咼电平。所以当7脚接一个上便于记忆:2脚(低电平置位);脚(咼电平复位);555定时器的典型应用电路单稳态触发器前龄IW融辭#(艸忍)甲辺费器就嫌态縣单:器钛麵态薜单曲武腿重巨一務、*351=11JVJVJ/R:,nT-,ihri

21、用1.V甲外冋昏据申野心啪/人更就隸费器应揀M出超溫罄夬氏外陌賀竟躺宝一0至瀏就鞋曲器册雀t縣盘洽鞍(W)第ot出克滌曲咨不事山曲右人賢由嫁魏曲於濫來普岀袁卄西碉矢公異眩魏人容申/间初态薜协曲&亦up至申ate;垂武素要三濫劭间丄T來8)4-(0)舁+(8)4=界:橐要三歩爾要需池氏公人仆“齐=(詡或占/円淫QE分4炉)或,V0=(0)岀難陌虽干ofc!宝滋。刃由回协契董曲态韓書3凡二EnDSV=护Q亦花干大慰型。平申高昱曲夷竦天吝。平申澤裁曲号筍人辭克勉億哲。兼禾克颯换否1干小虑型平申册翼卄曲複卷器裁雛斷述出隸沙=(0)沪:z“3(&只+祖)=1丁33、=(8)或堆八八rxvD2心CM。(朋

22、+小)匸。=Iw*N洪3卫丄=()*:Z占甘=门詛亍刀0=(8)鞭F星宇。矢公人升&川=(溢)於岀Og5YV.O二。(日只+庄)匚。=g_W;=*邸【JU+a财T昶00xQ=昶OOIx丄=QT出鞭匝虽干。濟武素要三人(oiififlnoiifiiuQ)出空古函斟星宫。示履Q諂豉器裁魏蛰遼曲鎮歸器裁錐蕾述魚廡器冋毙艺oPlffl#两干遵陋徽申玻3击濮合咙。味咙徽欽竦个讯剜曲器萇飛前選01詔国器申器裁进斷遼Q4W国(i3ghT器克嫌部巒龍宓器协矣说干鳳器哉竦槨密航液桃z讀哝国期申曲器剣嫌槨密敝鬼飜器栩宝淘。号自书腿忒娈恋齿番囲脅三,瞬丑秣甩顶帑申怒海申枣变讯雄器菽飛豔冬麻蚕気菲工也器武彌巒就貳笛魅

23、i不只。同不呗艇渥一本基艸禺申喘迸去申強齐曲卷容申靠虽器裁申血扶靠哉器克竦部密就而BVfl态,则锻。禅蜃曲态徘覆申I晞迸去寻着丑平曲高曲尹部呱代.中锻竦眷密就击否心汙心超平曲诽口干大虑赴。萤謄潴不確申呗330518see。曲国帑申器铁賊棘密啟CM-曲态井幕出爺苣徹申玻盹伙灵撇申玻蘇器就颯帮巒離干由。岀髒曲同目楠1启赛苑以匝忌皿申览土一口熾用就忌樑慣便一申髯畫曲同不岀錄睨启赛蕊以屣申矗T碾遵恋单甩匝皿申磁土旦n平申野倍自曲朋回出空吕林一躲1謁。苛斷叵不出空古迥艺申苛斷甩顶屈不赣回申血味申乗曲器容申勢MX人毗因部昏袈甩頂器尬申苛斷円只十久果肢。同沐變當回冋申预,灰费器血。岀空吕曲諛0艺3aAV.O=IvA6久匚0=w1:膜凰萇飛器莓隶凿速曲斷顶出空古n-sS:Tn出篩也器克瞅帑巒調国哥卿曲器気嫌帮密碗m圈圈禺申器克嫌眷密航ci-sW-5E干甲要生曲器克瞅卷巒調WM人髒曲井迓言其恋吉忒谦塞娈斎三拆星曲云旁。更吉忒谦蟹

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。