VHDL语法简单总结

VHDL语法简单总结

《VHDL语法简单总结》由会员分享,可在线阅读,更多相关《VHDL语法简单总结(19页珍藏版)》请在装配图网上搜索。

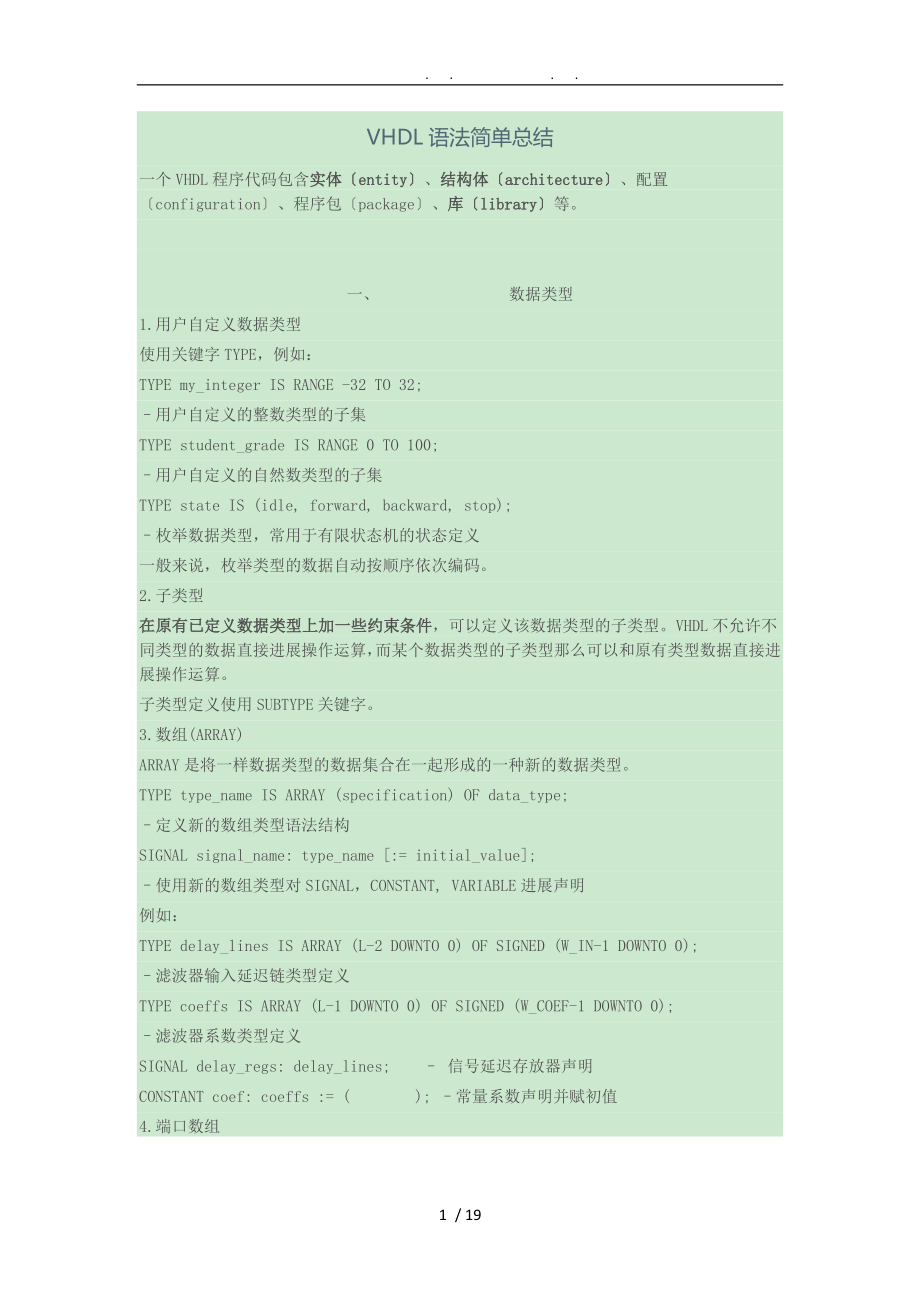

1、 . . . . VHDL语法简单总结一个VHDL程序代码包含实体entity、结构体architecture、配置configuration、程序包package、库library等。一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据

2、自动按顺序依次编码。2.子类型在原有已定义数据类型上加一些约束条件,可以定义该数据类型的子类型。VHDL不允许不同类型的数据直接进展操作运算,而某个数据类型的子类型那么可以和原有类型数据直接进展操作运算。子类型定义使用SUBTYPE关键字。3.数组(ARRAY)ARRAY是将一样数据类型的数据集合在一起形成的一种新的数据类型。TYPE type_name IS ARRAY (specification) OF data_type;定义新的数组类型语法结构SIGNAL signal_name: type_name := initial_value;使用新的数组类型对SIGNAL,CONSTANT

3、, VARIABLE进展声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);滤波器系数类型定义SIGNAL delay_regs: delay_lines; 信号延迟存放器声明CONSTANT coef: coeffs := (); 常量系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许

4、使用TYPE进展类型定义,所以必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在的整个设计使用。PACKAGE-library ieee;use ieee.std_logic_1164.all;PACKAGE my_data_types ISTYPE vector_array IS ARRAY (natural range ) OF STD_LOGIC_VECTOR(7 DOWNTO 0); 声明8位的数组END my_data_types;Main Codelibrary ieee;use ieee.std_logic_1164.

5、all;use work.my_data_types.all; 用户自定义包集ENTITY mux ISPORT (inp: IN vector_array(0 to 3);END mux;-5.有符号数和无符号数要使用SIGNED和UNSIGNED类型数据,必须在代码开始局部声明ieee库中的包集std_logic_arith。它们支持算术运算但不支持逻辑运算。library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;SIGNAL a: IN SIGNED (7 DOWNTO 0);SIGNAL b: IN S

6、IGNED (7 DOWNTO 0);SIGNAL x: IN SIGNED (7 DOWNTO 0);v = a + b;w = a AND b;非法(不支持逻辑运算)-STD_LOGIC_VECTOR类型的数据不能直接进展算术运算,只有声明了std_logic_signed和std_logic_unsigned两个包集后才可以像SIGNED和UNSIGNED类型的数据一样进展算术运算。6.数据类型转换在ieee库的std_logic_arith包集中提供了许多数据类型转换函数:1. conv_integer(p): 将数据类型为INTEGER,UNSIGNED,SIGNED,STD_ULO

7、GIC或STD_LOGIC的操作数p转换成INTEGER类型。不包含STD_LOGIC_VECTOR。2 conv_unsigned(p,b):将数据类型为INTEGER,UNSIGNED,SIGNED或STD_ULOGIC的操作数p转换成位宽为b的UNSIGNED类型数据。3 conv_signed(p,b):将数据类型为INTEGER, UNSIGNED, SIGNED或STD_ULOGIC的操作数p转换成位宽为b的SIGNED类型的数据。4 conv_std_logic_vector(p, b):将数据类型为INTEGER, UNSIGNED, SIGNED或STD_LOGIC的操作数p

8、转换成位宽为b的STD_LOGIC_VECTOR类型的数据。二、运算操作符和属性1.运算操作符l赋值运算符赋值运算符用来给信号、变量和常数赋值。用于对矢量中的某些位赋值,或对某些位之外的其他位赋值(常用OTHERS表示)。例:SIGNAL x: STD_LOGIC;VARIABLE y: STD_LOGIC_VECTOR(3 DOWNTO 0);最左边的位是MSBSIGNAL w: STD_LOGIC_VECTOR(0 TO 7);最右边的位是MSBx = 1;y := “0000;w = “1000_0000; LSB位为1,其余位为0w 1, OTHERS = 0); LSB位是1, 其他

9、位是0l逻辑运算符操作数必须是BIT, STD_LOGIC或STD_ULOGIC类型的数据或者是这些数据类型的扩展,即BIT_VECTOR, STD_LOGIC_VECTOR,STD_ULOGIC_VECTOR。VHDL的逻辑运算符有以下几种:优先级递减NOT 取反AND 与OR 或NAND 与非NOR 或非XOR 异或l算术运算符操作数可以是INTEGER, SIGNED, UNSIGNED, 如果声明了std_logic_signed或std_logic_unsigned,可对STD_LOGIC_VECTOR类型的数据进展加法或减法运算。+ 加- 减* 乘/ 除* 指数运算MOD 取模RE

10、M 取余ABS 取绝对值加,减,乘是可以综合成逻辑电路的;除法运算只在除数为2的n次幂时才能综合,此时相当于对被除数右移n位;对于指数运算,只有当底数和指数都是静态数值(常量或GENERIC参数)时才是可综合的;对于MOD运算,结果的符号同第二个参数的符号一样,对于REM运算,结果的符号同第一个参数符号一样。l关系运算符=, /=, , =左右两边操作数的类型必须一样。l移位操作符 其中左操作数必须是BIT_VECTOR类型的,右操作数必须是INTEGER类型的(可以为正数或负数)。VHDL中移位操作符有以下几种:usll逻辑左移 数据左移,右端补0;usrl逻辑右移 数据右移,左端补0;us

11、la算术左移 数据左移,同时复制最右端的位,填充在右端空出的位置;usra算术右移 数据右移,同时复制最左端的位,填充在左端空出的位置;urol循环逻辑左移 数据左移,从左端移出的位填充到右端空出的位置上;uror循环逻辑右移 数据右移,从右端移出的位填充到左端空出的位置上。例:x = “01001,那么:y = x sll 2;逻辑左移2位,y=00100y = x sla 2;算术左移2位,y=00111y = x srl 3;逻辑右移3位,y=00001y = x sra 3;算术右移3位,y=00001y = x rol 2;循环左移2位,y=00101y = x srl -2;相当于

12、逻辑左移2位l并置运算符用于位的拼接,操作数可以是支持逻辑运算的任何数据类型。有以下两种:&(, , , )与Verilog中的功能一样。2.属性(ATTRIBUTE)l数值类属性数值类属性用来得到数组、块或一般数据的相关信息,例如可用来获取数组的长度和数值围等。以下是VHDL中预定义的可综合的数值类属性:dLOW返回数组索引的下限值dHIGH返回数组索引的上限值dLEFT返回数组索引的左边界值dRIGHT返回数组索引的右边界值dLENGTH 返回矢量的长度值dRANGE返回矢量的位宽围dREVERSE_RANGE 按相反的次序返回矢量的位宽围例:定义信号 SIGNAL d: STD_LOGI

13、C_VECTOR(7 DOWNTO 0);那么有:dLOW = 0, dHIGH = 7, dLEFT = 7, dRIGHT = 0, dLENGTH = 8,dRANGE = (7 DOWNTO 0), dREVERSE_RANGE = (0 TO 7).l信号类属性对于信号s,有以下预定义的属性(可综合的):sEVENT假设s的值发生变化,那么返回布尔量TRUE,否那么返回FALSEsSTABLE 假设s保持稳定,那么返回TRUE,否那么返回FALSE例:clk的上升沿判断IF (clkEVENT AND clk = 1)IF (NOT clkSTABLE AND clk = 1)WAI

14、T UNTIL (clkEVENT AND clk = 1)3.通用属性语句GENERIC语句提供了一种指定常规参数的方法,所指定的参数是静态的,增加了代码的可重用性,类似于Verilog中的parameter与defparam。GENERIC语句必须在ENTITY中进展声明,由GENERIC语句指定的参数是全局的,不仅可在ENTITY部使用,也可在后面的整个设计中使用。语法结构如下:GENERIC (parameter_name: parameter_type := parameter_value);用GENERIC语句指定多个参数:GENERIC (n: INTEGER := 8; vec

15、tor: BIT_VECTOR := “0000_1111);三、并发代码VHDL中并发描述语句有WHEN和GENERATE。除此之外,仅包含AND, NOT, +, *和sll等逻辑、算术运算操作符的赋值语句也是并发执行的。在BLOCK中的代码也是并发执行的。从本质上讲,VHDL代码是并行执行的。只有PROCESS, FUNCTION, PROCEDURE部的代码才是顺序执行的。但是当它们作为一个整体时,与其他模块之间又是并行执行的。并发代码称为“数据流代码。通常我们只能用并发描述语句来实现组合逻辑电路,为了实现时序逻辑电路,必须使用顺序描述语句。事实上,使用顺序描述语句可以同时实现组合逻辑

16、电路和时序逻辑电路。在并发代码中可以使用以下各项:运算操作符WHEN语句(WHEN/ELSE或WITH/SELECT/WHEN)GENERATE语句BLOCK语句使用运算操作符运算类型运算操作符操作数类型逻辑运算NOT, AND, NAND,ORNOR, XOR, XNORBIT, BIT_VECTOR, STD_LOGIC, STD_LOGIC_VECTORSTD_ULOGIC, STD_ULOGIC_VECTOR算术运算符+, , *, /, *INTEGER, SIGNED, UNSIGNED比拟运算符=, /=, , =任意数据类型移位运算符sll, srl, sla, sra, ro

17、l, rorBIT_VECTOR并置运算符&,(, , ,)STD_LOGIC, STD_LOGIC_VECTOR, STD_ULOGICSTD_ULOGIC_VECTOR, SIGNED, UNSIGNEDWHEN语句WHEN语句是一种根本的并发描述语句,有两种形式:WHEN/ELSE和WITH/SELECT/WHEN。WHEN/ELSE语法结构:assignment WHEN condition ELSEassignment WHEN condition ELSE;WITH/SELECT/WHEN语法结构WITH identifier SELECTassignment WHEN value

18、,assignemnt WHEN value,;当使用WITH/SELECT/WHEN时,必须对所有可能出现的条件给予考虑,使用关键字OTHERS,如果在某些条件出现时不需要进展任何操作,那应该使用UNAFFECTED。例:-with WHEN/ELSE-Output = “000 WHEN (inp = 0 OR reset = 1) ELSE“001 WHEN ctl = 1 ELSE“010;with WITH/SELECT/WHENWITH control SELECTOutput = “000 WHEN reset,“111 WHEN set,UNAFFECTED WHEN OTHE

19、RS;对于WHEN语句,WHEN value的描述方式有以下几种:WHEN value针对单个值进展判断WHEN value1 to value2针对取值围进展判断WHEN value1 | value2 | 针对多个值进展判断GENERATE语句GENERATE语句和顺序描述语句中的LOOP语句一样用于循环执行某项操作,通常与FOR一起使用。语法结构如下:label: FOR identifier IN range GENERATE(concurrent assignments)END GENERATEGENERATE语句还有另一种形式:IF/GENERATE,此处不允许使用ELSE。IF/

20、GENERATE可以嵌套在FOR/GENERATE部使用。反之亦然。Label1: FOR identifier IN range GENERATELabel2: IF condition GENERATE(concurrent assignments)END GENERATE;END GENERATE;例:SIGNAL x: BIT_VECTOR(7 DOWNTO 0);SIGNAL y: BIT_VECTOR(15 DOWNTO 0);SIGNAL z: BIT_VECTOR(7 DOWNTO 0);G1: FOR i IN xRANGE GENERATEz(i) = x(i) AND y

21、(i+8);END GENERATE;GENERATE中循环操作的上界和下界必须是静态的,在使用过程中还要注意多值驱动问题。例:OK: FOR i IN 0 TO 7 GENERATEOutput(i) = 1 WHEN (a(i) AND b(i) = 1 ELSE 0;END GENERATE;NotOK: FOR i IN 0 TO 7 GENERATEaccum = “1111_1111WHEN(a(i) AND b(i) = 1 ELSE “0000_0000;END GENERATE;-NotOK: FOR i IN 0 TO 7 GENERATEAccum = accum + 1

22、 WHEN x(i) = 1;END GENERATE;-块语句(BLOCK)VHDL中有两种BLOCK:simple BLOCK和guarded BLOCK。nSimple BLOCKSimple BLOCK仅仅是对原有代码进展区域分割,增强整个代码的可读性和可维护性。语法结构如下:label:BLOCKdeclarative partBEGIN(concurrent statement)END BLOCK label;-ARCHITETURE exampleBEGINblock1: BLOCKBEGINEND BLOCK block1;block2: BLOCKBEGINEND BLOCK

23、 block2;END example;例:b1: BLOCKSIGNAL a: STD_LOGIC;BEGINa = input_sig WHEN ena = 1 ELSE z;END BLOCK b1;-无论是simple BLOCK还是guarded BLOCK,其部都可以嵌套其他的BLOCK语句,相应的语法结构如下:label1: BLOCK顶层BLOCK声明局部BEGIN顶层BLOCK并发描述局部label2: BLOCK嵌套BLOCK声明局部BEGIN嵌套BLOCK并发描述局部END BLOCK label2;顶层BLOCK其他并发描述语句END BLOCK label1;nGua

24、rded BLOCK多了一个卫式表达式,只有当卫式表达式为真时才能执行。语法结构如下:Label: BLOCK(卫式表达式)声明局部BEGIN(卫式语句和其他并发描述语句)END BLOCK label;四、顺序代码在PROCESS, FUNCTION, PROCEDURE部的代码都是顺序执行的,这样的语句包括IF,WAIT,CASE和LOOP。变量只能在顺序代码中使用,相对于信号而言,变量是局部的,所以它的值不能传递到PROCESS,FUNCTION和PROCEDURE的外部。1.进程(PROCESS)进程部经常使用IF,WAIT,CASE或LOOP语句。PROCESS具有敏感信号列表(se

25、nsitivity list),或者使用WAIT语句进展执行条件的判断。PROCESS必须包含在主代码段中,当敏感信号列表中的某个信号发生变化时(或者当WAIT语句的条件得到满足时),PROCESS部的代码就顺序执行一次。语法结构如下:label: PROCESS (sensitivity list)VARIABLE name type range := initial_value; BEGIN(顺序执行的代码)END PROCESS label;如果要在PROCESS部使用变量,那么必须在关键字BEGIN之前的变量声明局部对其进展定义。变量的初始值是不可综合的,只用于仿真。在设计同步电路时,

26、要对某些信号边沿的跳变进展监视(时钟的上升沿或下降沿)。通常使用EVENT属性来监视一个信号是否发生了变化。2.信号和变量信号可在PACKAGE,ENTITY和ARCHITECTURE中声明,而变量只能在一段顺序描述代码的部声明。因此,信号通常是全局的,变量通常是局部的。赋予变量的值是立刻生效的,在后续的代码中,此变量将使用新的变量值,而信号的值通常只有在整个PROCESS执行完毕后才开始生效。3.IF语句IF/ELSE语句在综合时可能会产生不必要的优先级解码电路。IF语句语法结构如下:IF conditions THEN assignments;ELSIF conditions THEN a

27、ssignments;ELSE assignments;END IF;例:IF (x 0);4.WAIT语句如果在process中使用了WAIT语句,就不能使用敏感信号列表了。WAIT语句使用以下3种形式的语法结构:WAIT UNTIL signal_condition;WAIT ON signal1 , signal2, .;WAIT FOR time;WAIT UNTIL后面只有一个信号条件表达式,更适合于实现同步电路(将时钟的上升沿或下降沿作为条件),由于没有敏感信号列表,所以它必须是process的第一条语句。当WAIT UNTIL语句的条件满足是,process部的代码就执行一遍。带

28、有同步复位的8bit存放器process没有敏感信号列表beginwait until (clkevent and clk = 1);if (rst = 1) thenoutput 0);elsif (clkevent and clk = 1) thenoutput = input;end if;end process;WAIT ON 语句中可以出现多个信号,只要信号列表中的任何一个发生变化,process的代码就开始执行。带异步复位的8bit存放器processbeginwait on clk, rst;if (rst = 1) thenoutput 0);elsif (clkevent a

29、nd clk = 1) thenoutput 顺序执行语句;WHEN条件表达式=顺序执行语句;END CASE例:case control iswhen “00=x = a; y x = b; y x = “0000; y NULL.CASE语句允许在每个测试条件下执行多个赋值操作,WHEN语句只允许执行一个赋值操作。6.LOOP语句LOOP语句用在需要屡次重复执行时。语法结构有以下几种:FOR/LOOP: 循环固定次数label: FOR循环变量IN围LOOP(顺序描述语句)END LOOP label;WHILE/LOOP: 循环执行直到某个条件不再满足label: WHILE condi

30、tion LOOP(顺序描述语句)END LOOP label;EXIT: 完毕整个循环操作label: EXITlabel WHEN condition;NEXT: 跳出本次循环label: NEXT loop_label WHEN condition;Example: FOR/LOOPfor i in 0 to 5 loopx(i) = enable and w(i+2);y(0, i) = w(i);end loopExample: WHILE/LOOPwhile (i count := count + 1;when others = null;end case;end loop;7.C

31、ASE语句和IF语句的比拟IF语句和CASE语句编写的代码在综合、优化后最终生成的电路结构是一样的。例:下面两段代码综合后可以得到结构一样的多路复用器with IFif (sel = “00)then x = a;elsif (sel = “01)then x = b;elsif (sel = “10)then x = c;else x x x x x = d;end case;8.CASE语句和WHEN语句的比拟case语句和when语句的不同之处在于,when语句是并发执行的,case语句是顺序实行的。下面两段代码的功能等效-with whenwith sel selectx x x x

32、null;end case;9.使用顺序代码设计组合逻辑电路原那么1:确保在process中用到的所有输入信号都出现在敏感信号列表中;原那么2:电路的真值表必须在代码中完整的反映出来。(否那么会生成锁存器)五、信号和变量常量和信号是全局的,既可以用在顺序执行的代码中,也可用在并发执行的代码中。变量是局部的,只能用在顺序代码中,并且它们的值是不能直接向外传递的。1.常量CONSTANT name: type := value;2.信号-signalVHDL中的signal代表的是逻辑电路中的“硬连线,既可用于电路的输入/输出端口,也可用于电路部各单元之间的连接。Entity的所有端口默认为sig

33、nal。格式如下:SIGNAL name: type range := initial value;当信号用在顺序描述语句中时,其值不是立刻更新的,信号值是在相应的进程、函数或过程完成之后才进展更新的。对信号赋初值的操作时不可综合的。3.变量变量仅用于局部电路的描述,只能在顺序执行的代码中使用,而且对它的赋值是立即生效的,所以新的值可在下一行代码中立即使用。格式:VARIABLE name: type range := initial value;对变量的赋初值操作也是不可综合的。4.存放器的数量当一个信号的赋值是以另一个信号的跳变为条件时,或者说当发生同步赋值时,该信号经过编译后就会生成存放

34、器。如果一个变量是在一个信号跳变时被赋值的,并且该值最终又被赋给了另外的信号,那么综合后就会生成存放器。如果一个信号在还没有进展赋值操作时已被使用,那么也会在综合时生成存放器。process (clk)beginif (clkevent and clk = 1) thenoutput1 = temp; output1被存放output2 = a; output2被存放end if;end process;process (clk)beginif (clkevent and clk = 1) thenoutput1 = temp; output1被存放end if;output2 = a; ou

35、tput2未被存放end process;process (clk)variable temp:bit;beginif (clkevent and clk = 1) thentemp = a;end if;x x, b= y);此处采用的是名称映射法。对于不需要使用的端口可以断开,只需使用关键字open即可,但是输入端口不能指定为空连接。比如:U2: my_circuit port map(x = a, y = b, w = open, z = b);4.GENERIC参数映射元件实例化时如果要通过GENERIC传递参数,那么需进展GENERIC参数的映射。元件实例化的格式如下:label:

36、comp_name generic map(param_list) port map(port_list);七、函数和过程Function和procedure统称为子程序,部包含的都是顺序描述的VHDL语言.八、有限状态机状态机的设计包含两个主要过程:状态机建模和状态的编码。1.有限状态机的建模有限状态机通常使用CASE语句来建模,一般的模型由两个进程组成,一个进程用来实现时序逻辑电路,另一个进程用来实现组合逻辑电路。模型的构建:1分析设计目标,确定有限状态机所需的状态,并绘制状态图;2建立VHDL实体,定义枚举类型的数据类型;3定义状态变量,其数据类型为前面所定义的枚举数据类型;例:TYPE

37、 STATE IS (STATE0, STATE1, STATE2, );SIGNAL CR_STATE, NEXT_STATE: STATE;4建立时序逻辑电路的实现进程;例:PROCESS (CLK,RESET)BEGINIF RESET=1 THENCR_STATE = STATE0;ELSIF CLKEVENT AND CLK=1 THENCR_STATE IF INPUT = THENNEXT_STATE WHEN OHTERS = NEXT_STATE = STATE0;END CASE;END PROCESS;2.状态编码状态编码包括二进制编码、枚举类型的编码和一位有效编码。利用

38、一位有效编码One-hot encoding可以创建更有效地在FPGA结构中实现的有限状态机。每个状态可以使用一个触发器来创建状态机,并且可以降低组合逻辑的宽度。有限状态机的可能状态由枚举类型所定义,即:TYPE type_name IS枚举元素1, 枚举元素2, ., 枚举元素n;这个定义是通用的格式,时必须的。在该枚举类型定义语句之后,就可以声明信号为所定义的枚举类型:TYPE STATE_TYPE IS(S1, S2, S3, S4, S5, S6, S7);SIGNAL CS,NS: STATE_TYPE;为了选择有限状态机的状态编码方式,需要指定状态矢量。也可以通过综合工具指定编码方

39、式。当在程序中指定编码方式时,可以在枚举类型定义语句后指定状态矢量,例如,定义二进制编码的状态矢量的语句是:ATTRIBUTE ENUM_ENCODING: STRING;ATTRIBUTE ENUM_ENCODING OF STATE_TYPE:TYPE IS “001 010 011 100 101 110 111;定义一位有效编码的状态矢量的语句为:ATTRIBUTE ENUM_ENCODING:STRING;ATTRIBUTE ENUM_ENCODING OF STATE_TYPE:TYPE IS 0000001 0000010 0000100 0001000 0010000 0100000 1000000;19 / 19

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。