数字设计基础与应用第2章组合逻辑电路分析与设计

数字设计基础与应用第2章组合逻辑电路分析与设计

《数字设计基础与应用第2章组合逻辑电路分析与设计》由会员分享,可在线阅读,更多相关《数字设计基础与应用第2章组合逻辑电路分析与设计(120页珍藏版)》请在装配图网上搜索。

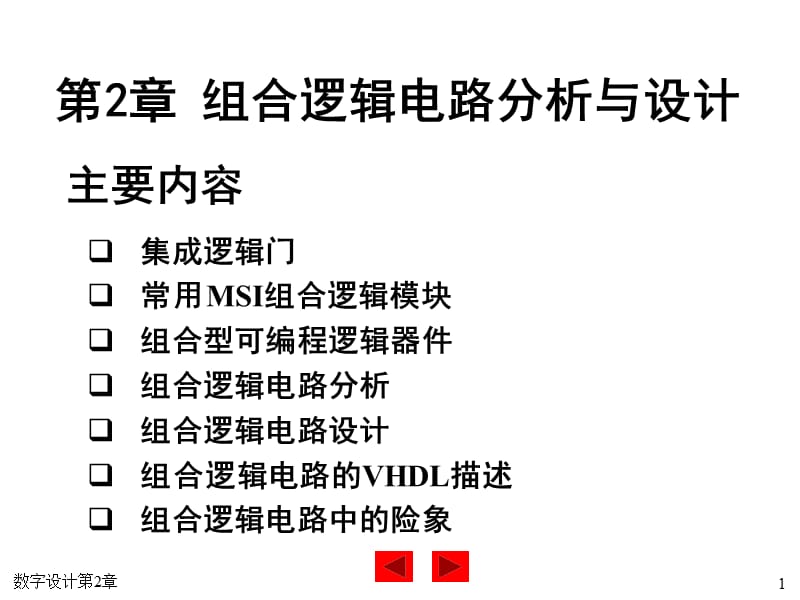

1、数字设计第2章,1,集成逻辑门 常用MSI组合逻辑模块 组合型可编程逻辑器件 组合逻辑电路分析 组合逻辑电路设计 组合逻辑电路的VHDL描述 组合逻辑电路中的险象,第2章 组合逻辑电路分析与设计,主要内容,数字设计第2章,2,2.1 集成逻辑门,数字集成电路的集成度分类 三类典型的数字集成电路 TTL、CMOS、ECL,数字设计第2章,3,一、集成逻辑门系列 1. CMOS逻辑门 最简单的集成逻辑门CMOS非门,数字设计第2章,4,CMOS与非门和或非门,数字设计第2章,5,CMOS逻辑系列 4000系列 74HC系列 74HCT系列 CMOS逻辑电路的特点 逻辑摆幅大,电路抗干扰能力强。 静

2、态功耗低。 输入阻抗极大,驱动同类型逻辑门的能力强。 容易因静电感应造成器件击穿而损坏。 CMOS集成电路使用注意事项 器件防静电包装 人员和设备良好接地 正确处理不用的输入端。,数字设计第2章,6,2. TTL逻辑门 74民品系列、54军品系列 74系列中的子系列 74系列的发展和演变 TTL与CMOS的比较 电源电压:典型TTL(5V),CMOS(318V) 输出高电平:TTL(3.6V),CMOS(VDD0.1) 逻辑摆幅和抗干扰能力:CMOS更好 静态功耗:CMOS的静态功耗很低,数字设计第2章,7,3. ECL逻辑门 高速逻辑电路系列 特点 ECL的基本逻辑门是“或/或非门” 早期E

3、CL电路使用的单一负电源供电,输出低电平为,高电平为,该电平与TTL和CMOS器件的逻辑电平不兼容。新型ECL电路既可以采用、也可以采用供电,方便了不同系列逻辑器件的互联。 强调高速度的ECL系列存在高功耗的缺点。 ECL逻辑门的“或”输出端具有“线与”功能、“或非”输出端具有“线或”功能,数字设计第2章,8,二、集成逻辑门的主要电气指标 1. 逻辑电平 电压传输特性 输入低电平VIL 关门电平VOFF 输入高电平VIH 开门电平VON 输出低电平VOL 输出高电平VOH,数字设计第2章,9,2. 噪声容限 低电平输入时的噪声容限VNL =VOFFVOLMAX 高电平输入时的噪声容限VNH =

4、VOHMINVON,(a) (b) (c) 图25 输入、输出电平和噪声容限示意图 (a) 一般关系; (b) 典型TTL; (c) 典型CMOS,数字设计第2章,10,3. 输出驱动能力 高电平输出电流IOH 低电平输出电流IOL 扇出系数NO 逻辑电路在正常工作条件下,一个输出端可以同时驱动同系列逻辑电路输入端数目的最大值。 4. 功耗 :逻辑电路消耗的电源功率 静态功耗:电路的输出状态不变时的功率损耗。 动态功耗:电路状态变化时产生的功耗。 低速电路的功耗以静态功耗为主;高速电路的功耗以动态功耗为主。,数字设计第2章,11,5. 时延 时延tpd ,就是从输入信号达到电路输入端,到相应的

5、输出信号出现在电路输出端之间所需要的时间。 上升时延tpLH 下降时延tpHL 平均时延tpd,数字设计第2章,12,6不同系列逻辑门的性能比较,数字设计第2章,13,三、逻辑电路的其它输入、输出结构 1. 施密特触发器输入 典型逻辑门对输入电压在阈值电压附近的波动敏感,容易造成输出错误。 施密特触发器输入结构采用两个不同的阈值电压来克服输入电压的波动 。,数字设计第2章,14,2. 三态输出结构 三态输出:逻辑电路的输出端不仅可以输出0和1,还可以呈现高阻抗状态。 具有三态输出结构的非门的逻辑符号和真值表。 三态输出是一种独立于电路逻辑功能的输出结构,不同逻辑功能的电路,可以根据需要设置三态

6、输出端。,数字设计第2章,15,三态总线 将多个三态输出端接在一起就构成了三态总线。 三态门还能用于实现数据的双向传输。,数字设计第2章,16,3. 漏极(集电极)开路输出结构 使用漏极开路门时,必须在输出端Z外接一个负载电阻RL,上拉到一个正电源VCC。改变上拉电源,可以改变输出电平,使之适用于逻辑电平不同的器件系列的互联。 多个漏极开路逻辑门的输出端可以直接连在一起,实现所谓的“线与逻辑”。,数字设计第2章,17,4. CMOS模拟信号传输门结构 当使能信号EN=1时,MOS管导通,A、B之间呈现低阻通道,模拟信号(或数字信号)可以沿任意方向传输(AB或BA)。当使能信号EN=0时,MOS

7、管截止,沟道消失,A、B之间只有极低的漏电流,相当于开关断开。,数字设计第2章,18,一、加法器 加法器是用于实现两个二进制数加法运算的电路。 加法器分类: 不考虑低位进位的2个一位二进制数相加的半加器 考虑低位进位的2个一位二进制数相加的全加器 实现2个多位二进制数相加的加法器 实现两个十进制数相加的BCD码加法器 带符号数加法器等。,2.2 常用MSI组合逻辑模块,数字设计第2章,19,1. 半加器 实现两个1位二进制数相加的电路称为半加器,数字设计第2章,20,2. 全加器 带有低位进位输入的一位加法器,数字设计第2章,21,3串行加法器 串行加法器:将n个一位全加器级联,得到两个n位二

8、进制数的加法电路。 串行加法器时延较大,电路的工作速度较慢。,数字设计第2章,22,4先行进位4位二进制全加器7483/283,数字设计第2章,23,7483/283的级联扩展,数字设计第2章,24,二、比较器 数值比较器用于比较两个数的大小,并给出“大于”、“等于”和“小于”三种比较结果。 两个多位二进制数比较大小的方法: 从高位开始,逐位比较。 高位不同,结果立现。 高位相等,比较结果由低位的比较结果决定。 当各位都对应相等时,则两个数完全相等。 比较器分类: 半比较器:只能比较2个一位二进制数的比较器。 全比较器:比较2个一位二进制数。当它们相等时,全比较器的比较结果由低位送来的比较结果

9、决定。,数字设计第2章,25,1. 4位二进制数比较器7485 7485是采用并行比较结构的4位二进制数比较器,数字设计第2章,26,功能表用于描述芯片功能。,数字设计第2章,27,27485的级联扩展 7485的三个级联输入端用于连接低位芯片的三个比较输出端,实现比较位数的扩展。,数字设计第2章,28,三、编码器 编码:将一组字符或信号用二进制代码加以表示。 编码器:实现编码的数字电路,对于每一个有效的输入信号,编码器输出与之对应的一组二进制代码。 编码器分类: 2n线n线编码器(二进制编码器) BCD码编码器(十进制编码器),数字设计第2章,29,1. 2n线n线编码器 以基本的8线3线编

10、码器为例 存在问题: 没有键被按下(即编码输入全为0)时,编码输出为“000”,无法与I01的编码输入相区别。 若同时有多个键被按下(即有多个编码输入端同时为1),编码输出将出现混乱。,输出函数表达式,数字设计第2章,30,28线3线优先编码器74148 优先编码器:当多个编码输入信号同时有效时,编码器仅对其中优先级最高的信号进行编码。 低电平有效:就是信号有效时为低电平。,数字设计第2章,31,会看MSI的功能表 编码输入 编码输出 使能输入 使能输出 组选择输出,数字设计第2章,32,74148的级联扩展,3BCD码编码器 图222可以用于实现各种BCD码编码器。,数字设计第2章,33,四

11、、译码器 译码器执行与编码器相反的操作。 译码器分类: 全译码器:译码器输入的n位二进制代码有2n种不同的取值,称为2n种不同的编码值。若将每种编码分别译出,则译码器有个2n译码输出端,这种译码器称为全译码器。 部分译码器:若译码器输入的编码是一位BCD码,则不是输入取值的所有组合都有意义,此时只需要与输入BCD码相对应的十个译码输出端,这种译码器称为部分译码器。,数字设计第2章,34,13线8线译码器74138 74138是3位自然二进制编码的全译码器。 使能输入:只有当 时,该译码器才使能。 74138的译码输出信号低电平有效。 74138输出了编码输入变量的所有最大项。,数字设计第2章,

12、35,24线16线译码器74154和BCD码译码器 74154是输出低电平有效的4线16线全译码器。 利用74154可以实现各种BCD码译码器。,数字设计第2章,36,3七段显示译码器 LED七段显示器 通过七个发光段的亮灭组合,实现十进制字符09的显示,各段按ag命名。 共阴极七段显示器的段驱动为高电平有效,共阳极七段显示器的段驱动是低电平有效。,数字设计第2章,37,七段显示译码器7448 功能:将8421BCD码变换为七段显示码,输出高电平有效。,数字设计第2章,38,数字设计第2章,39,7448的四种工作模式:字符显示、灭灯、灭0和试灯。 字符显示模式(功能表第一列为015对应的16

13、行)显示16种字符,其中输入为00001001时输出8421BCD码对应的字符09;输入10101111时输出特殊字符。 灭灯模式就是强行熄灭所有LED。 灭0模式用于多位显示时关闭有效位之外多余的0的显示。 试灯模式检验LED是否正常,各段全亮,与数据输入无关。 利用 实现多位十进制数码显示器中熄灭多余0的电路,数字设计第2章,40,4译码器的扩展和应用 译码器的扩展 译码器用于计算机中的地址译码,数字设计第2章,41,五、数据选择器和数据分配器 数据选择器用于从多路输入信号中选择一路信号输出。 数据分配器用于将一路输入信号分配到不同的输出通道。,数字设计第2章,42,18选1数据选择器74

14、151,数字设计第2章,43,2数据选择器的扩展,3数据分配器,数字设计第2章,44,数字设计第2章,45,可编程逻辑器件中集成了大量的逻辑门、连线、记忆单元等电路资源,这些电路资源的使用由用户通过计算机编程方式加以确定。 本节介绍PLD的基本结构和表示方法,以及PLD在组合逻辑电路中的简单应用。,2.3 组合型可编程逻辑器件,数字设计第2章,46,一、 PLD的一般结构与电路画法 PLD的基本结构中,包括输入输出缓冲电路、与阵列和或阵列。与或阵列是其主体,任何逻辑函数都可以写成与或表达式的形式,通过与或阵列实现函数功能。,数字设计第2章,47,1PLD中连接的表示方法,数字设计第2章,48,

15、2基本逻辑门的PLD表示法,数字设计第2章,49,3与或阵列图 PLD中的与门被组织成与阵列结构,或门被组织成或阵列结构,与门输出的乘积项在或阵列中求和。 图238是一个用与或阵列表示的电路图,与阵列是固定的,四个与门实现了A、B两个变量的四个最小项;或阵列是可以编程的。 函数F1和F2的表达式为,数字设计第2章,50,二、 组合型PLD PLD的分类: 可编程只读存储器(PROM) 可编程逻辑阵列(PLA) 可编程阵列逻辑(PAL) 通用阵列逻辑(GAL) 复杂可编程逻辑器件(CPLD) 现场可编程门阵列(FPGA),简单PLD(SPCD),复杂PLD,数字设计第2章,51,只读存储器(RO

16、M)是计算机中用于存储确定信息的存储器。其中的数据由ROM生产厂家在制造ROM时“写入”,出厂后,用户无法修改。 ROM中的数据通常按字节(8比特)寻址,每个地址对应一字节数据。,1可编程只读存储器PROM和EPROM,数字设计第2章,52,从逻辑函数发生器的角度来看,ROM的地址译码器可以实现n个输入变量An-1A0的全部2n个最小项,其地址译码器就是固定连接的与阵列。数据输出线Di的函数表达式为 从实现逻辑函数的角度来看,存储矩阵的结构就像多输出函数的真值表,存储矩阵中的每一列的取值就是多输出函数的真值表中各函数的取值。存储矩阵就是一个连接关系可以编程的或阵列。 该ROM可以等效为一个与或

17、阵列,可以实现8个n变量的逻辑函数。 可编程ROM可以分为:熔丝型PROM、EPROM、EEPROM。,数字设计第2章,53,PROM结构的缺点:采用固定的与阵列和可编程的或阵列,当输入变量个数增加时,与阵列的规模成倍增加,这种结构限制了PROM作为函数发生器的应用。 可编程逻辑阵列PLA:采用与、或阵列都可编程的结构,使乘积项不必是最小项,从而为实现逻辑函数提供了较大的灵活性。 PLA的问题:由于器件制造中的困难和相关应用软件的开发没有跟上,PLA很快被随后出现的PAL取代。,2可编程逻辑阵列PLA,数字设计第2章,54,PAL中与或阵列的特点:与阵列可编程、或阵列固定。 PAL16L8:

18、输入、输出:10个专用输入端,2个专用三态输出端和6个输入/三态输出(I/O)端。 与阵列:可编程与阵列包括64个与门,每个与门有32个输入端。 或阵列:或阵列包含8个7输入或门,这些或门和与门的连接关系是固定的,可以同时实现8个输出逻辑函数。输出由三态非门控制。 函数形式:用PAL16L8实现的逻辑函数的基本表达式是与或非式。,3可编程阵列逻辑PAL,数字设计第2章,55,数字设计第2章,56,用PAL16L8实现8421BCD码余3循环码的转换电路,4通用阵列逻辑GAL GAL在芯片中增加了存储元件,并采用输出逻辑宏单元OLMC结构,改善了内部资源使用的灵活性,成为低密度可编程逻辑器件的首

19、选。GAL的原理与应用在第4章介绍。,数字设计第2章,57,组合电路的分析,就是分析组合电路输入变量和输出变量的取值关系和函数关系,进而确定电路的功能。 一、基本分析方法(步骤) 据给定的组合电路,写出输出函数表达式 据表达式,列出真值表 说明电路的逻辑功能,2.4 组合逻辑电路分析,数字设计第2章,58,例21 分析图241所示电路。 解:表达式为 真值表如上所示。 逻辑功能:少数服从多数的三人表决电路。,数字设计第2章,59,二、分析实例 例22 分析图241所示电路。 逻辑功能:一位全加器。 其中,J是进位输出,S是本位和输出。,解:表达式为,数字设计第2章,60,例23 分析图243所

20、示电路,已知输入信号B3B2B1B0是5421BCD码。,解:由真值表可以看出,该电路实现了5421码到8421码的转换。,数字设计第2章,61,组合逻辑电路设计就是根据功能要求设计相应的逻辑电路。设计的基本要求是功能正确,电路尽可能简化。 一、基本设计方法(步骤) 据功能要求,确定输入、输出变量,列出相应的真值表。 据设计要求,采用适当的化简方法求出与所要求的逻辑门相适应的输出函数的最简表达式。 画出与最简表达式相对应的逻辑电路图。,2.5 组合逻辑电路设计,数字设计第2章,62,例24 设计一个组合电路,该电路能够判断一位BCD码是否8421码。若是8421码,则当该码能被4或5整除时,输

21、出有所指示。要求分别用与非门、或非门、与或非门实现该电路(允许反变量输入)。 解: 定义输入、输出变量,列出真值表 用输入变量ABCD的取值表示一位8421BCD码,定义输出变量F11表示输入的是8421码,F21表示输入8421码可以被4或5整除。 列出真值表。,数字设计第2章,63, 用卡诺图化简法求最简式: 用与非门实现时,应圈1得最简与或式,再转换为最简与非式。 用或非门实现时,应圈0得最简或与式,再转换为最简或非式。 用与或非门实现时,应圈0得最简或与式,再转换为最简与或非式。,数字设计第2章,64,输出函数的最简与或式和最简与非式为 输出函数的最简或与式、最简或非式和最简与或非式为

22、,数字设计第2章,65, 画出实现该逻辑功能的三种不同门电路形式。,数字设计第2章,66,二、设计实例(基于MSI的组合电路设计) 例25 试用4位全加器7483实现5421BCD码到8421BCD码的转换。 解:,数字设计第2章,67,例26 试用4位全加器芯片7483实现一位8421BCD码加法器。 解:两个一位十进制数相加时,和的取值范围是018,将该范围内二进制数和8421BCD码的取值列表,寻找将二进制结果转换为8421BCD码的规律。,数字设计第2章,68,N109时,二进制数与8421码相同 N1010时,8421码比相应的二进制数大6。 判断N1010的电路就用表中的DC。 当

23、C4=1时,或S3=1且S2和S1中至少有一个为1时,DC=1。 DC的表达式为,数字设计第2章,69,由真值表直接写出输出函数的最小项表达式。并变换为与74138低电平有效的输出端相符的形式。 画出电路图,例27 试用3线8线译码器74138实现一位二进制全减器。 解:一位二进制数全减器就是两个一位二进制数的带借位的减法运算。,定义变量:设被减数、减数和低位的借位输入分别为X、Y、Bi,运算结果为本位的差D和向高位的借位输出Bo 列出真值表,数字设计第2章,70,例28 试用输出高电平有效的3线8线译码器实现逻辑函数 解:输出高电平有效的译码器的输出函数就是输入变量的最小项。 直接实现该最小

24、项表达式需要外接一个6输入的或门。 对函数表达式稍加变换,就可以使电路更简单,如图249所示。,数字设计第2章,71,例29 试用8选1数据选择器实现逻辑函数,解:首先将函数F写成最小项表达式的变量形式,然后从四个自变量中选择三个作为MUX的地址变量(本例选ABC),并将表达式写成MUX输出函数表达式形式。 当MUX的地址变量A2A1A0=ABC时, 输入数据端,数字设计第2章,72,例210 试用4选1数据选择器实现例29中的逻辑函数。,解:选AB作为MUX的地址变量,按AB两个变量的最小项形式变换函数F的表达式 当4选1 MUX的地址变量 A1A0=AB时,MUX的数据 输入端 实现D0和

25、D2需要附加两个与门。,数字设计第2章,73,例211 试用8选1数据选择器实现逻辑函数,解:采用降维卡诺图法 选择MUX的地址变量A2A1A0=BCD,将BCD作为卡诺图中的一组变量,函数F中的其它变量作为另一组变量,画出降维卡诺图。,数字设计第2章,74,数字电路的描述方法 真值表、表达式、电路图。 硬件描述语言:VHDL、Verilog HDL等。 一、VHDL源程序的基本结构 VHDL源程序5个组成部分:实体说明、结构体、库、程序包和配置。 实体说明和结构体组成设计实体,简称实体。 通常,将实体理解为一个逻辑模块,实体说明用来描述该模块的端口。结构体用来描述该模块的内部功能。,2.6

26、组合逻辑电路的VHDL描述,数字设计第2章,75,实体说明 实体说明用于描述逻辑模块的输入/输出信号,其语法如下: 例212 用实体说明语句描述2输入与非门的输入输出端口。,数字设计第2章,76,端口说明 语句格式: port (端口名: 端口模式 数据类型;.); 端口模式指端口的数据传输方向,共有以下4种: in:输入端口,该引脚接收外部信号 out:输出端口,该引脚向外输出信号 inout:双向端口,可以双向传输信号 buffer:缓冲端口,工作于缓冲模式 数据类型是端口信号的取值类型,VHDL有着丰富的数据类型。 工业标准逻辑型是最常用的数据类型,该类型的数据有 0、1、X(未知)、Z

27、(高阻)等9种取值。 类属说明:类属说明语句用于指定参数,其格式为 generic(常数名: 数据类型:=设定值;.);,数字设计第2章,77,例213 用类属说明语句定义总线宽度。 类属说明语句也常用来定义仿真时需要的时间参数,例如: 实体说明只是指出了输入、输出信号的名称、方向、类型。 而电路的逻辑功能,即函数关系,是模块的内部信息,由相应的结构体定义。,数字设计第2章,78,结构体 结构体的关键字是architecture,结构体用于具体描述实体的逻辑功能,其语法如下: 例214 与例212中实体说明对应的一种结构体。,数字设计第2章,79,配置 一个实体可以用不同的结构体来描述,配置语

28、句用于确定一个具体的实体和结构体对。 配置语句的关键字是configuration,语句的一般格式如下 例如,将例214的结构体配置给实体说明,其配置语句如下,数字设计第2章,80,库和程序包 库和程序包结构用于实现数据类型、常量和子程序在不同实体中的共享。 程序包用来存放各个设计都能共享的数据类型、子程序说明、属性说明和元件说明。程序包由程序包说明和程序包体两部分组成,其语法格式为 数据类型、常量,以及子程序和元件等首先在程序包说明中定义,然后在程序包体中描述各项的具体内容。,数字设计第2章,81,例215 库是已编译数据的集合,它存放包集合定义、实体定义、结构定义和配置定义。库以VHDL源

29、文件形式存在,主要包括: STD库、WORK库、IEEE库、ASIC库、用户自定义库等 vhdl的库说明语句格式为:,数字设计第2章,82,二、VHDL的基本语法 VHDL的语言要素:数据对象、数据类型和运算操作符 数据对象:包括变量、信号和常数。 变量:VHDL的变量是局部量,只能用于进程和子程序中,变量的使用包括变量定义语句和变量赋值语句。 变量定义语句的语法格式为 variable 变量名:数据类型 := 初始值; 例216 变量定义语句举例。,数字设计第2章,83,变量赋值语句的格式为 变量名 := 表达式; 例217 变量赋值语句举例 信号: 其概念类似于硬件电路中的连接线,与之相关

30、的信号赋值、延时等语句适合于描述硬件电路的一些基本特征。信号的适用范围是实体、结构体和程序包,信号不能用于进程和子程序。信号语句包括信号定义语句和信号赋值语句。,数字设计第2章,84,信号定义语句的格式为 signal 信号名: 数据类型 : 初始值; 例218 信号定义语句举例。 信号赋值语句的格式为 信号名 = 表达式; 例219 信号赋值语句举例。 信号定义语句用来说明电路内部使用的信号,这些信号并不送往外部端口,所以在结构体中说明,而不是在实体说明语句中说明。,数字设计第2章,85,例220 用信号定义与赋值语句说明图255所示电路。 常数:可以使程序容易阅读和修改。定义常数后,程序中

31、所有用到该常数值的地方都用定义的常数名表示,需要修改该常数时,只要在该常数名定义处修改即可。 常数定义的语法格式为 constant 常数名:数据类型 := 表达式;,数字设计第2章,86,例221 常数定义语句举例。 VHDL的数据类型:标准数据类型和用户自定义数据类型 标准数据类型:VHDL的STD库中STANDARD程序包中定义了十种数据类型,称为标准数据类型或预定义数据类型。 bit(位型数据)、bit_vector(位矢量型)、integer(整型数据)、boolean(布尔型数据)、real(实型数据)、character(字符型数据)、string(字符串)、time(时间型数据

32、)、severity level(错误等级类型)、natural (自然数类型)和positive(正整数类型) IEEE库的STD_LOGIC_1164程序包中还定义了两种应用十分广泛的数据类型:std_logic(工业标准逻辑型)和std_logic_vector(标准逻辑矢量型)。 用户自定义数据类型:用户可以选择VHDL标准数据类型的一个子集,作为自定义数据类型。,数字设计第2章,87,VHDL的运算操作符 常用的运算操作符包括逻辑运算符、算术运算符和关系运算符。 逻辑运算符用于对逻辑型数据bit和std_logic、逻辑型数组bit_vector和std_logic_vector、以

33、及布尔型数据boolean的逻辑运算。逻辑运算经VHDL综合器综合后通常直接产生组合电路。 算术运算符包括对整型数的加、减运算符,对整型或实型(含浮点数)的乘、除运算符,对整型数的取模和取余运算符,对单操作数添加符号的符号操作符“”和“”,以及指数运算符“*”和取绝对值运算符“ABS”。 并置运算符“&”用于将位或数组组合起来,形成新的数组,例如,“VH”&“DL”的结果是“VHDL”,”01”&”00”的结果是”0100”。 关系运算符的作用是比较相同类型的数据,并将结果表示为boolean型数据的ture或false。关系运算符包括等于(=)、不等于(/=)、大于()、大于等于(=)、小于

34、()、小于等于(=)。,数字设计第2章,88,VHDL的语句:并行执行语句和顺序执行语句 并行语句:并行语句主要用来描述模块之间的连接关系。并行语句之间是并行关系,当某个信号发生变化时,受此信号触发的所有语句同时执行。 常用的并行语句包括信号赋值语句、条件赋值语句和元件例化语句。 条件赋值语句:包括when_else和with_select_when when_else语句的语法格式为,数字设计第2章,89,例222 采用when_else语句描述表219所示的24线译码器。,with_select_when语句的语法格式为,数字设计第2章,90,例223 采用with_select_when

35、语句描述表220所示的42线编码器。,元件例化语句 元件例化就是引入一种连接关系,将预先设计好的实体定义为一个元件,然后通过关联将实际信号与当前实体中指定的端口相连接。,数字设计第2章,91,元件例化分为两部分: 元件定义语句:将一个已有的设计实体定义为一个元件,实现封装,使之只保留对外的端口,可以被其它模块调用。 元件例化语句:就是元件的调用,方法是将元件端口(输入输出信号、即引脚)映射到需要连接的位置上。 语句格式,数字设计第2章,92,例224 采用元件例化的方式实现图256所示电路。 解:首先用VHDL描述一个两输入与非门,然后把该与非门当作一个已有元件,用元件例化语句结构实现图256

36、所示的连接关系。,数字设计第2章,93,数字设计第2章,94,顺序语句:顺序语句按照程序书写顺序执行,顺序语句只能出现在进程和子程序中。 顺序语句包括赋值语句、流程控制语句、子程序调用语句和等待语句等类别,这里只介绍流程控制语句中的if和case语句。 if语句:分为三种,if_then_end if、if_then_else_end if和if_elsif_else_end if。 if_then_end if语句的语法格式是,当条件成立时,执行顺序语句,否则跳过该语句。,例225 if_then_end if语句举例,数字设计第2章,95,if_then_else_end if语句的语法格

37、式是,若条件成立,就执行顺序语句1;否则,就执行顺序语句2。,例226 用if语句描述一个表221所示的三态非门。,数字设计第2章,96,if_elsif_else_end if语句的语法格式是,若条件成立,就执行then后的顺序语句;否则,检测后面的条件,并在条件满足时,执行相应的顺序语句。 if语句至少有一个条件句,条件句必须是boolean表达式,当条件句的值为ture时(即条件成立),执行then后的顺序语句。方括号中的内容是可选项,用于多个条件的情形。,数字设计第2章,97,case语句 case语句根据表达式的取值直接从多组顺序语句中选择一组执行。 语句格式为,例227 用case

38、语句描述一个表222所示的1线4线分配器。,数字设计第2章,98,结构体功能描述语句的结构类型 用结构体进行功能描述可以采用五种不同类型的语句结构,如图所示。 块语句 块语句将结构体中的并行描述语句组成一个模块,类似于电路图中的模块划分,用于改善并行语句的结构,增加可读性,或用来限制某些信号的使用范围。 block语句的格式为,数字设计第2章,99,例228 由半加器和或门构成的一位二进制全加器电路如图所示,试采用block语句结构描述该电路。 解:在VHDL描述时,采用block语句结构将两个半加器H_ADDER和或门OR2分别实现,可以使VHDL源程序更加清晰易懂。,数字设计第2章,100

39、,数字设计第2章,101,进程语句 进程语句结构采用顺序语句描述事件,其语法结构为 例2 29 一个2选1多路选择器MUX2的进程描述语句。,数字设计第2章,102,子程序调用语句 在被主程序调用后,子程序可以将处理结果返回主程序。子程序中只能使用顺序语句。VHDL中的子程序有两种类型:过程和函数。 函数 函数的语句格式为 在VHDL中,function语句只能计算数值,不能改变其参数的值,所以其参数的模式只能是in,常省略不写。通常,各种功能的函数语句的程序都被集中放置在包集合中,并且可以在结构体中直接调用。,数字设计第2章,103,例2 30 函数MIN的功能是比较两个变量X、Y的大小,并

40、返回两数中较小的一个。 在VHDL中,function语句只能计算数值,不能改变其参数的值,所以其参数的模式只能是in,常省略不写。通常,各种功能的函数语句的程序都被集中放置在包集合中,并且可以在结构体中直接调用。,数字设计第2章,104, 过程 过程的语句格式为 例231 用过程语句结构实现24线译码器,数字设计第2章,105,数字设计第2章,106,三、用VHDL描述组合逻辑电路 VHDL结构体的功能描述有三种方式:行为描述方式、数据流描述方式(RTL描述)、结构化描述方式。 行为描述方式属于高级描述方式,通过对电路行为的描述实现设计。这种描述方式不包含与硬件结构有关的信息,易于实现系统优

41、化,易于维护。 数据流描述方式的特点是采用逻辑函数表达式形式表示信号关系。 结构化描述方式通过元件例化来实现,这种方法类似电路图的描述方式,将电路的逻辑功能分解为功能单元,每个功能单元都被定义为一个元件,通过元件说明和元件调用的方式,构成电路中各元件的连接关系。,数字设计第2章,107,例232 分别用数据流描述、结构化描述和行为描述方式设计一个三人表决电路。 解:三人表决电路的电路图和真值表如下面的图表所示。,数字设计第2章,108,数字设计第2章,109,数字设计第2章,110,例233 用VHDL描述一个三态输出总线电路,总线宽度BUS_WIDTH为8位,数据输入和输出分别用D_IN和D

42、_OUT表示,使能输入信号OE高电平有效。,数字设计第2章,111,例234 用VHDL描述一个8线3线优先编码器,该编码器的编码输入端是I(7)I(0),编码优先顺序由高到低是I(7)到I(0),编码输出端是A(2)A(0),该电路还有一个高电平有效的编码有效输出端GS。,数字设计第2章,112,例235 用VHDL描述一个将一位8421BCD码转换为高电平有效的七段显示码的七段显示译码器。,数字设计第2章,113,数字设计第2章,114,2.7 组合逻辑电路中的险象,逻辑门的传输时延、以及多个输入信号变化时刻不同步可能引起短暂的输出差错,这种现象称为逻辑电路的冒险现象,简称险象。 电路中出

43、现的短暂的错误输出称为毛刺。 险象的持续时间虽然短暂,危害却不可忽视。 一、险象的来源、种类与识别方法 逻辑险象:信号的传输时延引起的险象。 逻辑险象可以通过修改逻辑设计来消除。 功能险象:多个输入信号的变化时刻不同步引起的险象。 功能险象无法通过逻辑设计来清除,只能通过适当选择输出信号的读取时间避开险象。,数字设计第2章,115,静态险象:若输入信号的变化只引起一个毛刺,这种险象称为静态险象。 动态险象:若输入信号的变化引起多个毛刺,这种险象称为动态险象。 根据毛刺的不同极性,可以把险象分为0型险象和1型险象。 0型险象:输出信号中的毛刺为负向脉冲的险象称为0型险象,通常出现在与或、与非、与

44、或非型电路中。 1型险象:输出信号中的毛刺为正向脉冲的险象称为1型险象,通常出现在或与、或非型电路中。 静态逻辑险象可以用两种方法来识别:代数法和卡诺图法。,数字设计第2章,116,代数识别法 对于一个逻辑表达式,若在给定了其它自变量适当的逻辑值后,出现了下列两种情形之一,则存在逻辑险象: 例236 判断图260所示电路是否存在险象,说明险象类型,并画出输出波形。,数字设计第2章,117,显然,F中只有变量B同时具有原变量和反变量形式,当自变量A=C=D=1时, 。因此,该电路存在变量B引起的0型险象。 由波形图可以看到,当输入信号B出现下降沿时,由于信号在电路中传输时延的不同,输出信号中出现

45、不应有的负脉冲(毛刺),即该电路确实存在0型险象。,数字设计第2章,118,卡诺图识别法 在卡诺图中,若有两个圈存在相切部分,且相切部分没有被另一个圈覆盖时,则相应的逻辑函数存在险象。 例237 用卡诺图法判断函数 是否存在险象。,解:由卡诺图可以看出,与乘积项BD和 对应的两个圈相切,且相切部分的“1”没有被其它圈覆盖。当变量D的取值变化时,函数将从一个圈转移到另一个圈,因此产生险象。由于函数是与或式,该险象是D变量引起的0型险象。,数字设计第2章,119,二、险象的消除方法 通过逻辑设计消除险象:是消除险象的根本方法,对于简单电路和静态险象是一种可行的方法。对于复杂的电路和其它类型的险象,

46、采用逻辑设计的方法消除险象十分困难。 选通法:避开险象发生的时刻,等输出稳定后再读取其值。选通法存在的问题是选通信号的产生并不总是很方便。 滤波法:采用额外的滤波电路消除输出信号中的毛刺。滤波法存在的问题是滤波器虽然清除了毛刺,但也使输出信号的上升沿和下降沿变坏。,数字设计第2章,120,修改逻辑设计消除险象 通过增加冗余项使函数在任何情况下都不会出现 从卡诺图上看,就是在两个圈的相切部分增加一个冗余圈,将相切处的0或1圈起来。 例238 采用增加冗余项的方法,消除例237中存在的险象。,和,解:在卡诺图中增加一个冗余的圈,该卡诺图对应的函数表达式为 新增加的乘积项 是冗余项。当ABC=011时,函数为 ,显然,冗余项的存在屏蔽了原来产生0型险象的 。为了消除险象而增加的冗余项,也使函数变得不是最简了。,

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 党纪学习教育专题研讨发言提纲二篇

- 党纪学习教育专题研讨发言材料二篇

- 二篇党纪学习教育中心组研讨发言材料

- 在2024年市区委党纪学习教育工作安排部署讲话提纲心得体会合集

- 2024年在全县党纪学习教育工作动员部署会上的讲话心得体会合集

- 2024年党纪学习教育领导干部纪律教育专题培训讲话心得体会多篇

- 党纪学习教育心得体会参考范文6篇汇编

- 2024党纪学习教育实施方案计划表

- 镇党委开展党纪学习教育实施方案二篇

- 某县委书记在全县党纪学习教育动员部署会

- 某县委常委、纪委书记在党纪学习教育专题读书班专题研讨会上的发言

- 某县纪委书记学习新修订《中国共产党纪律处分条例》的研讨发言

- 某县委书记在县委党纪学习教育读书班暨县委理论学习中心组专题学习会议上的讲话

- 某县委书记在党纪学习教育动员部署会上的讲话

- 某县委书记在党纪学习教育专题读书班开班式上的讲话