触发器和时序逻辑电路.ppt

触发器和时序逻辑电路.ppt

《触发器和时序逻辑电路.ppt》由会员分享,可在线阅读,更多相关《触发器和时序逻辑电路.ppt(95页珍藏版)》请在装配图网上搜索。

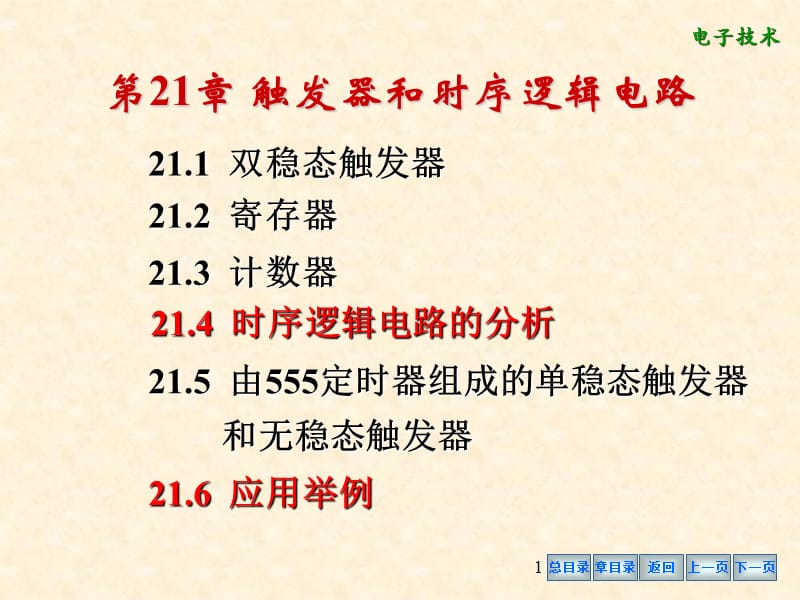

1、第21章 触发器和时序逻辑电路,21.1 双稳态触发器,21.2 寄存器,21.3 计数器,21.5 由555定时器组成的单稳态触发器 和无稳态触发器,21.6 应用举例,21.4 时序逻辑电路的分析,电路的输出状态不仅取决于当时的输入信号,而且与电路原来的状态有关。当输入信号消失后,电路状态仍维持不变。这种具有存贮记忆功能的电路称为时序逻辑电路。,时序逻辑电路的特点:,下面介绍双稳态触发器,它是构成时序电路的基本逻辑单元。,21.1 双稳态触发器,21.1.2 JK 触发器,21.1.3 D 触发器,22.1.4 触发器逻辑功能转换,21.1.1 RS 触发器,21.1 双稳态触发器,特点:

2、 1、有两个稳定状态“0”态和“1”态; 2、能根据输入信号将触发器置成“0”或“1”态; 3、输入信号消失后,被置成的“0”或“1”态能 保存下来,即具有记忆功能。,双稳态触发器: 是一种具有记忆功能的逻辑单元电路,它能储存一位二进制码。,21.1.1 RS 触发器,两互补输出端,1. 基本 RS 触发器,两输入端,反馈线,触发器输出与输入的逻辑关系,设触发器原态为“1”态。,(1) S=1,R = 0,1,0,1,0,触发器输出与输入的逻辑关系,设触发器原态为“0”态。,(1) S=1,R = 0,0,0,0,0,1,设原态为“0”态,1,1,0,触发器保持“1”态不变,置位,0,结论:

3、不论 触发器原来 为何种状态, 当 S=1, R=0时, 将使触发器 置“1”或称 为置位。,1,1,设原态为“1”态,1,1,0,0,(2) S=0,R = 1,1,设原态为“1”态,0,0,1,触发器保持“0”态不变,复位,1,结论: 不论 触发器原来 为何种状态, 当 S=0, R=1时, 将使触发器 置“0”或称 为复位。,1,1,设原态为“1”态,0,0,1,1,(3) S=1,R = 1,1,1,设原态为“1”态,0,0,1,触发器保持“1”态不变,1,当 S=1, R=1时, 触发器保持 原来的状态, 即触发器具 有保持、记 忆功能。,1,0,若G1先翻转,则触发器为“0”态,“

4、1”态,若先翻转,基本 RS 触发器状态表,逻辑符号,缺陷:存在不确定态,不能受控制。,2. 可控 RS 触发器,基本R-S触发器,导引电路,时钟脉冲,当C=0时,0,R,S 输入状态 不起作用。 触发器状态不变,当 C = 1 时,1,打开,触发器状态由R,S 输入状态决定。,打开,当 C = 1 时,1,打开,(1) S=0, R=0,触发器状态由R,S 输入状态决定。,打开,1,1,0,(2) S = 0, R= 1,(3) S =1, R= 0,1,Q=1,Q=0,(4) S =1, R= 1,可控RS状态表,C高电平时触发器状态由R、S确定,例:画出可控 RS 触发器的输出波形,可控

5、 RS状态表,C高电平时触发器状态由R、S确定,存在问题:,时钟脉冲不能过宽,否则出现空翻现象,即在一个时钟脉冲期间触发器翻转一次以上。,克服办法:采用 JK 触发器或 D 触发器,21.1.2 JK触发器,1.电路结构,从触发器,主触发器,反馈线,2. 工作原理,F主打开,F主状态由J、K决定,接收信号并暂存。,F从封锁,F从状态保持不变。,C,C,状态保持不变。,从触发器的状态取决于主触发器,并保持主、从状态一致,因此称之为主从触发器。,F从打开,F主封锁,C,C高电平时触发器接收信号并暂存(即F主状态由J、K决定,F从状态保持不变)。,要求C高电平期间J、K的状态保持不变。,C低电平时,

6、F主封锁J、K不起作用,C,分析JK触发器的逻辑功能,(1)J=1, K=1,设触发器原态为“0”态,主从状态一致,C,(1)J=1,K=1,设触发器原态为“1”态,为“?”状态,J=1, K=1时,每来 一个时钟脉冲,状 态翻转一次,即具 有计数功能。,(1)J=1, K=1,“0”态,C,(2)J=0,K=1,设触发器原态为“1”态,设触发器原态为“0”态,“0”态,C,(3)J=1,K=0,设触发器原态为“0”态,设触发器原态为“1”态,“1”态,C,(4)J=0,K=0,设触发器原态为“0”态,设触发器原态为“1”态,“1”态,C,结论:,C高电平时F主状态由J、K决定,F从状态不变。

7、,3. JK触发器的逻辑功能,Qn,1,0 0,1 1,1 0,0,0 1,C高电平时F主状态由J、K决定,F从状态不变。,(保持功能),(置“0”功能),(置“1”功能),(计数功能),C下降沿触发翻转,0,Qn,1,Qn,例:JK 触发器工作波形,1,0,0,0,0,1,1,1,0,0,触发器状态由C高电平时的J、K决定。,C,J,K,Q,1,1,1,0,0,1,0,0,1,1,C,J,K,Q,0,1,1,0,1,1,1,0,0,1,基本R-S触发器,导引电路,21.1.3 D 触发器,1.电路结构,反馈线,2.逻辑功能,(1)D = 0,1,0,当C = 0时,0,当C = 1时,0,1

8、,封锁,在C = 1期间,触发器保持“0”不变,2.逻辑功能,(2)D = 1,0,1,当C = 0时,1,当C = 1时,0,1,封锁,在C = 1期间,触发器保持“1”不变,封锁,上升沿触 发翻转,C上升沿前接收信号,上升沿时触发器翻转,( 其Q的状态与D状态一致;但Q的状态总比D的状态变化晚一步,即Qn+1 =Dn;上升沿后输入 D不再起作用,触发器状态保持。 (即不会空翻),结论:,例:D 触发器工作波形图,1,0,1,0,0,C,D,Q,0,1,0,1,0,21.1.4 触发器逻辑功能的转换,1. 将JK触发器转换为 D 触发器,仍为下降沿 触发翻转,2. 将JK触发器转换为 T 触

9、发器,当J=K时,两触发器状态相同,3. 将 D 触发器转换为 T 触发器,触发器仅具有计数功能,即来一个C, 触发器就翻转一次。,21.2 寄存器,寄存器是数字系统常用的逻辑部件,它用来存放数码或指令等。它由触发器和门电路组成。一个触发器只能存放一位二进制数,存放 n 位二进制时,要 n个触发器。,21.2.1 数码寄存器,仅有寄存数码的功能。,清零,寄存指令,通常由D触发器或R-S触发器组成,并行输入方式,寄存数码,触发器状态不变,清零,寄存指令,并行输出方式,&,&,&,&,Q,Q,Q,Q,状态保持不变,21.2.2 移位寄存器,不仅能寄存数码,还有移位的功能。,所谓移位,就是每来一个移

10、位脉冲,寄存器中所寄存的数据就向左或向右顺序移动一位。,寄存数码,1.单向移位寄存器,D,1011,1,Q,1011,1,0,1,1,J,K,F3,数据依次向左移动,称左移寄存器,输入方式为串行输入。,Q,Q,Q,再输入四个移位脉冲,1011由高位至低位依次从Q3端输出。,串行输出方式,左移寄存器波形图,1,1,1,1,1,1,0,待存数据,1011存入寄存器,从Q3取出,四位左移移位寄存器状态表,1,2,3,1,0,1,并 行 输 出,再继续输入四个移位脉冲,从Q3端串行输出1011数码,串行输出,2.并行、串行输入/串行输出寄存器,寄存器分类,并行输入/并行输出,串行输入/并行输出,并行输

11、入/串行输出,串行输入/串行输出,21.3 计数器,计数器是数字电路和计算机中广泛应用的一种逻辑部件,可累计输入脉冲的个数,可用于定时、分频、时序控制等。,21.3.1 二进制计数器,按二进制的规律累计脉冲个数,它也是构成其它进制计数器的基础。要构成 n位二进制计数器,需用 n个具有计数功能的触发器。,1. 异步二进制加法计数器,异步计数器:计数脉冲C不是同时加到各位触发器。最低位触发器由计数脉冲触发翻转,其他各位触发器有时需由相邻低位触发器输出的进位脉冲来触发,因此各位触发器状态变换的时间先后不一,只有在前级触发器翻转后,后级触发器才能翻转。,二 进 制 数 Q2 Q1 Q0,0 0 0 0

12、 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 1 1 1 8 0 0 0,脉冲数 (C),二进制加法计数器状态表,从状态表可看出: 最低位触发器来 一个脉冲就翻转 一次,每个触发 器由 1变为 0 时, 要产生进位信号, 这个进位信号应 使相邻的高位触 发器翻转。,当J、K=1时,具有计数功能,每来一个脉冲触发器就翻转一次.,三位异步二进制加法计数器,在电路图中J、悬空表示 J=K=1,下降沿 触发翻转,当相邻低位触发器由1变 0 时翻转,异步二进制加法器工作波形,每个触发器翻转的时间有先后,与计数脉冲不同步,用D触发器构成三位二进制异步

13、加法器,2、若构成减法计数器C又如何连接?,思考,1、各触发器C应如何连接?,各D触发器已接成T触发器,即具有计数功能,2. 同步二进制加法计数器,异步二进制加法计数器线路联接简单。 各触发器是逐级翻转,因而工作速度较慢。,同步计数器:计数脉冲同时接到各位触发器,各触发器状态的变换与计数脉冲同步。,同步计数器由于各触发器同步翻转,因此工作速度快。但接线较复杂。,二 进 制 数 Q2 Q1 Q0,0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 1 0 0 5 1 0 1 6 1 1 0 7 1 1 1 8 0 0 0,脉冲数 (C),二进制加法计数器状态表,最低位触发器F0每

14、来一个脉冲就翻转一次;,F1:当Q0=1时,再来一个脉冲则翻转一次;,F2:当Q0=Q1= 1时,再来一个脉冲则翻转一次。,四位二进制同步加法计数器级间连接的逻辑关系,触发器翻转条件,J、K端逻辑表达式,J、K端逻辑表达式,F0,每输入一C翻一次,F1,F2,F3,J0 =K0 =1,Q0 =1,J1 =K1 = Q0,Q0 = Q1 = 1,J2 =K2 = Q1 Q0,Q0 = Q1 = Q2 = 1,J3 =K3= Q2 Q1 Q0,由J、K端逻辑表达式,可得出四位同步二进制计数器的逻辑电路。(只画出三位同步二进制计数器的逻辑电路),(加法),(减法),三位同步二进制加法计数器,计数脉冲

15、同时加到各位触发器上,当每个脉冲到来后触发器状态是否改变要看J、K的状态。,各触发器状态的变换和计数脉冲同步,例1:分析图示逻辑电路的逻辑功能,说明其用处。 设初始状态为“000”。,解:1. 写出各触发器 J、K端和C端的逻辑表达式,解:当初始状态为“000”时, 各触发器J、K端和C端的电平为,由表可知,经5个脉冲循环一次,为五进制计数器。,2.列写状态转换表,分析其状态转换过程,C1= Q0,由于计数脉冲没有同时加到各位触发器上,所以为异步计数器。,C0= C=0,K0 =1,异步五进制计数器工作波形,1,1,1,1,1,0,0,0,0,0,0,0,0,0,0,0,0,0,例2:分析图示

16、逻辑电路的逻辑功能,说明其用处。 设初始状态为“000”。,解:写出各触发器输入端的逻辑表达式,列写状态转换表,分析其状态转换过程,C,Q2 Q1 Q0,由表可知,经6个脉冲循环一次,为六进制计数器。,C1= C2 = Q0,异步六进制计数器工作波形,1,0,0,0,0,0,0,0,0,0,0,1,0,0,0,0,1,1,1,1,1,21.3.2 十进制计数器,十进制计数器: 计数规律:“逢十进一”。它是用四位二进制数表示对应的十进制数,所以又称为二-十进制计数器。,四位二进制可以表示十六种状态,为了表示十进制数的十个状态,需要去掉六种状态,具体去掉哪六种状态,有不同的安排,这里仅介绍广泛使用

17、 8421编码的十进制计数器。,十进制加法计数器状态表,1. 十进制同步加法计数器,十进制计数器工作波形,1,0,0,1,0,0,0,0,2. 异步十进制计数器,74LS290是异步二-五-十进制集成计数器,逻辑功能及外引线排列,(1) R01 、 R02 : 置“0”输入端,逻辑功能,逻辑功能及外引线排列,(1) S91 、 S92 : 置“9”输入端,逻辑功能,逻辑功能及外引线排列,计数功能,0,0,0,0,1,1,0,0,1,1,74LS290 功能表,输 入,输 出,Q2,Q3,Q1,Q0,1,1,0,1,1,0,1,1,R01,S92,S91,R02,有任一为“0”,有任一为“0”,

18、计数,置9,8421异步十进制计数器,计数状态,异步五进制计数器,工作波形,5421异步十进制计数器,工作波形,反馈置“0”法:当满足一定的条件时,利用计数器的复位端强迫计数器清零,重新开始新一轮计数。 利用反馈置“0”法可用已有的计数器得出小于原进制的计数器。 例:用一片74LS290可构成十进制计数器,如将十进制计数器适当改接,利用其清零端进行反馈清零,则可得出十以内的任意进制计数器。,21.3.3 任意进制计数器,用一片74LS290构成十以内的任意进制计数器,例:六进制计数器,例:六进制计数器,当状态 0110(6)出现时,将 Q2=1,Q1=1 送到复位端 R01和R02,使计数器立即清零。状态 0110仅瞬间存在。,74LS290为异步 清零的计数器,反馈置“0”实现方法:,六进制计数器,S92,S91,Q3,Q0,Q2,Q1,R01,R02,C1,C0,计数脉冲,计数器清零,七进制计数器,当出现 0110(6)时,应立即使计数器清零,重新开始新一轮计数。,当出现 0111(7)时,计数器立即清零,重新开始新一轮计数。,计数器清零,二片74LS290可构成100以内的计数器,例:二十四进制计数器,0010(2),0100(4),十位,个位,两位十进制计数器(100进制),

- 温馨提示:

1: 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

2: 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

3.本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

5. 装配图网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 糖尿病个案精品医学ppt课件

- 苏教版-小学数学-五年级-下册-分数的意义练习-课件

- 苏教版小学五年级数学下册《分数的大小比较》ppt课件

- 苏教版小学数学二年级上册期末复习优质课课件

- 苏教版小学数学二年级上册认识除法优质课课件

- 苏教版-小学数学-六年级-上册-6.3百分数与分数的互化--课件

- 苏教版五年级下册数学教学ppt课件第第四单元分数的意义和性质第6课时--分数与小数的互化

- 苏教版数学一年级下册-43-数学游戏:汉诺塔游戏-优质课件

- 苏教版数学六上《分数乘法的简单运用》-公开课获奖ppt课件

- 苏教版数学二上《乘加、乘减》精品公开课优质课ppt课件

- 苏教版三年级数学下册第七单元《分数的初步认识二》课件

- 苏教版小学数学二年级上册6的乘法口诀优质课课件

- 苏教版物理八年级上册最新ppt课件

- 苏教版四年级上册数学《可能性-第1课时-可能性》优质课ppt课件

- 苏教版数学六上2.4《分数乘分数》精品公开课优质课ppt课件3